STM32F103和TPS65251的多电源时序控制电路

2019-01-17

(国电南京自动化股份有限公司,南京 210037)

引 言

随着半导体技术的不断发展,处理器的性能和复杂度越来越高,为了降低功耗,提高稳定性,处理器普遍采用多电源供电技术,一般按内核、外设、模拟部分(如PLL或ADC)、数字部分(如DDR、GPIO等)设计不同的电源,每个部分都有一个电源轨。这些电源的电压等级不一定相同,一般内核的电源功耗大,因此电压较低,如1.0 V或1.1 V等,而外设需要考虑处理器的接口与其他器件的电压等级能兼容,一般以3.3 V或2.5 V等为主。芯片厂商对处理器的各路电源的上下电顺序有严格的要求,忽视该要求会导致处理器不能正常工作甚至会被烧坏。

1 Zynq-7020的多路电源简述

处理器所需的多路电源由开关电源模块将交流220 V转换成12 V,该12 V电源作为数字回路的总电源,使用TI公司的Buck转换器TPS65251,将12 V转换成所需的多路电源。多路电源一般有1.0 V、1.1 V、1.2 V、1.35 V、1.8 V、2.5 V、3.3 V、5 V等。本设计以Xilinx公司的Zynq-7020为例,其集成了基于处理系统(PS)的多功能Cortex-A9双内核和基于Artix-7技术的可编程逻辑阵列(PL)。对PS部分,严格的上电顺序是PS_VCCPINT、PS_VCCPAUX、PS_VCCPLL、PS_VCCOMIO1先同时上电,然后是PS_VCCODDR、PS_VCCOMIO0,这样可以保证对电源的汲取电流最小,且I/O接口在上电时处在三态状态中,PS_VCCPAUX和PS_VCCPLL必须是同一个电源。下电顺序与上电顺序完全相反。假如 PS_VCCOMIO1电压等级与PS_VCCPAUX、PS_VCCPLL相同,则可以与它们同时上电和下电。但PS_VCCPAUX和PS_VCCPLL必须是同一个电源。PS部分电源上下电顺序如表1所列。

表1 PS部分电源上下电顺序

对PL部分,上电顺序是PL_VCCINT、PL_VCCBRAM、PL_VCCAUX、PL_VCCO,这样也可以获得最小的汲取电流,确保I/O接口线在上电时处在三态状态。假如PL_VCCINT和PL_VCCBRAM是同一个电源,则它们可以同时上下电。假如PL_VCCAUX和PL-VCCO是同一电源,它们也是同时上下电。注意下电顺序与上电顺序完全相反。PL部分电源上下电顺序如表2所列。

表2 PL部分电源上下电顺

PS和PL部分的电源是完全独立的。PS的电源可以先于或后于PL的电源上电。PS和PL部分的电源互相隔离,这样可以防止被破坏。因此结合表1和表2看,只设计4路电源就可满足要求,分别是1.0 V、1.8 V、3.3 V、1.35 V,上电顺序应该为1.0 V、1.8 V、1.35 V、3.3 V,下电顺序应该为3.3 V、1.35 V、1.8 V、1.0 V。

2 硬件设计

2.1 原理简图

为了节约成本及满足电压计算的实时性,交流220 V电压在被互感器隔离后用信号调理电路调理成为偏置值为1.5 V、峰值范围在0~2.05 V的脉动电压后接入STM32F103的ADC,考虑1.5倍的裕量,最大输入电压为交流250 V时,峰值为3.3 V。ADC还采集了12 V、1.0 V、1.8 V、3.3 V、1.35 V电压。另外STM32F103输出4根I/O接口线,IO_0 ~IO_3接转换器的EN引脚,还输出一根IO_4接口线用来控制看门狗芯片的动作。STM32F103自身的供电电源由第一片转换器的Buck3输出,EN3引脚直接上拉,Buck3始终使能。原理简图如图1所示。

图1 原理图

2.2 输入电容选择

通过合理选择并联在开关电源模块里的整流桥输出侧电容器的电容值,使输入电源在装置掉电后至少能持续输出1.5 s,电容能量计算公式为w=0.5CU2,单位为焦耳,装置功耗约为6 W,若要放电时间达到t= 1.5 s,因为W=P×t,则电容值选为C=6 W×1.5 s/(0.5×220 V2)≈217 μF,实际可以选取220 μF/450 V的电解电容。

2.3 转换器TPS65251相关设计

(1)工作频率设置

按公式ROSC(kΩ)=174×f-1.122计算频率,设置工作频率为500 kHz,需在ROSC引脚与地之间串联电阻ROSC= 383 kΩ。

(2)输出电压设置

按公式R2=R1×(0.8 V ÷(VO-0.8 V))合理选择每一路输出反馈电阻R1和R2的阻值。对3.3 V输出,R1=40.2 kΩ,R2=12.7 kΩ;对1.35 V输出,R1=15 kΩ,R2=22 kΩ;对1.8 V输出,R1=20 kΩ,R2=16 kΩ;对1.0 V输出,R1=22 kΩ,R2=82 kΩ,电阻全部选用1%精度等级。

(3)限流保护设置

对Buck1按公式ILIM=180÷RLIM+1.3计算,设置ILIM为3 A,则RLIM为100 kΩ。对Buck2和Buck3,按公式ILIM=150÷RLIM+1.12计算,设置ILIM为2.5 A,则RLIM为120 kΩ。如果过电流延续10 ms以上,转换器会关断输出10 ms后重新启动。

(4)布局布线设计

电路板按4层板设计,内部两层分别为GND和POWER。使用Cadence 16.6 Allegro软件设计电路板文件,将VO和LX分别设置成铜皮(Shape)并放置在顶层,输入电源VIN也设置成Shape并放置在POWER层上。VIN的滤波电容和VO的LC里的滤波电容应使用低ESR的陶瓷电容(如用X5R或X7R电容),且尽量靠近转换器放置,距离引脚不要超过50 mil。尤其重要的是芯片底部的POWER PAD与电路板顶层的GND网络的Shape连接,该Shape一定要通过VIA与内部的GND层连接,这样有利于降低芯片对GND的热阻,增加芯片的散热功能,本设计中该Shape共放置了35个外径为0.05 mm、内径为0.03 mm的VIA。

3 软件设计

3.1 改进的方均根算法

STM32F103的ADC为12位的单极性SAR型ADC,为了保证有效值计算的精度,采用了改进型的方均根算法。方均根计算公式为:

设采样频率固定为fs=4.8 kHz(整周期时为96点),而信号频率f由CPU的Timer测量得出,f变化时整周期内的采样点会随之变化,为了提高计算精度,需要把整周期内不足一个完整采样间隔的部分也考虑进去,则每周期波的采样数量为:N.n = fs/f,其中N为整数部分,n为小数部分。考虑信号本身的偏置电压及ADC采样时产生的固有偏置量,程序实时计算总偏置量:

Uoffset ={ [U(0)/2+U(1)/2]+[U(1)/2+U(2)/2]+…+[U(N-1)/2+U(N)/2]+[U(N)/2+U(N.n)/2]*(N.n-N)}/N.n

由于U(0)=U(N.n),则可化简为:

U(N)*(1+0.n)/2]/N.n

则有:

U2={{[U(0)- Uoffset]2/2+[U(1)-Uoffset]2/2}+{[U(1)-Uoffset]2/2+[U(2)-Uoffset]2/2}+…+{[U(N-1)-Uoffset]2/2+[U(N)-Uoffset]2/2}+{[U(N)-Uoffset]2/2+[U(N.n)-Uoffset]2/2}* (N.n-N)}/N.n

同理化简为:

{[U(N)-Uoffset]2*(1+0.n)/2}}/N.n

再开方求得U。经试验得出,误差小于0.5%。数据如表3所列。

表3 测量精度误差

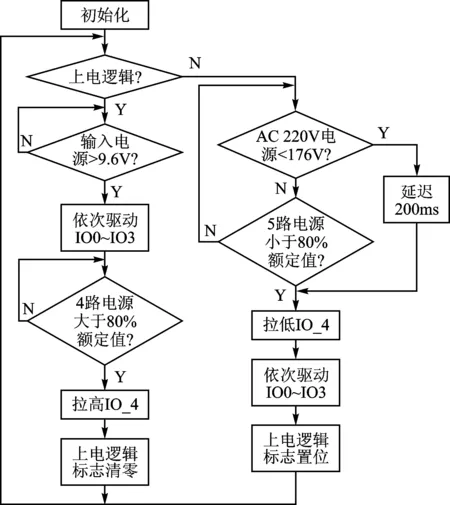

3.2 上下电控制逻辑

上电控制逻辑可以判断12 V是否到80%额定值(即9.6 V),如果到了且一直持续10 ms,则说明电源完好,依次拉高IO_0~ IO_3接口线,把1.0 V、1.8 V、3.3 V、1.35 V四路输出电源的EN引脚电平依次使能,然后采样这4路电源,均大于80%额定值时就把接口线IO_4拉高,驱动看门狗芯片的复位输出接口线返回,使得Zynq-7020的复位过程结束,程序启动起来。

下电控制逻辑是在运行过程中,如果交流220 V电压小于80%额定值,为了躲过电压的短时跌落,延迟200 ms后执行下电操作,即拉低接口线IO_4,复位Zynq-7020,再把4路输出电源的EN引脚依次全部拉低,4路输出电源输出为0 V,处理器就全部掉电。或者是12 V、1.0 V、1.8 V、3.3 V、1.35 V的任意一路低于80%额定值,则立刻执行下电操作。

STM32F103的程序一直在上电控制逻辑和下电控制逻辑这两个状态间切换,上电控制逻辑状态结束后进入下电控制逻辑,下电控制逻辑状态结束后进入上电控制逻辑。程序流程图如图2所示。

图2 程序流程图

4 试验结果

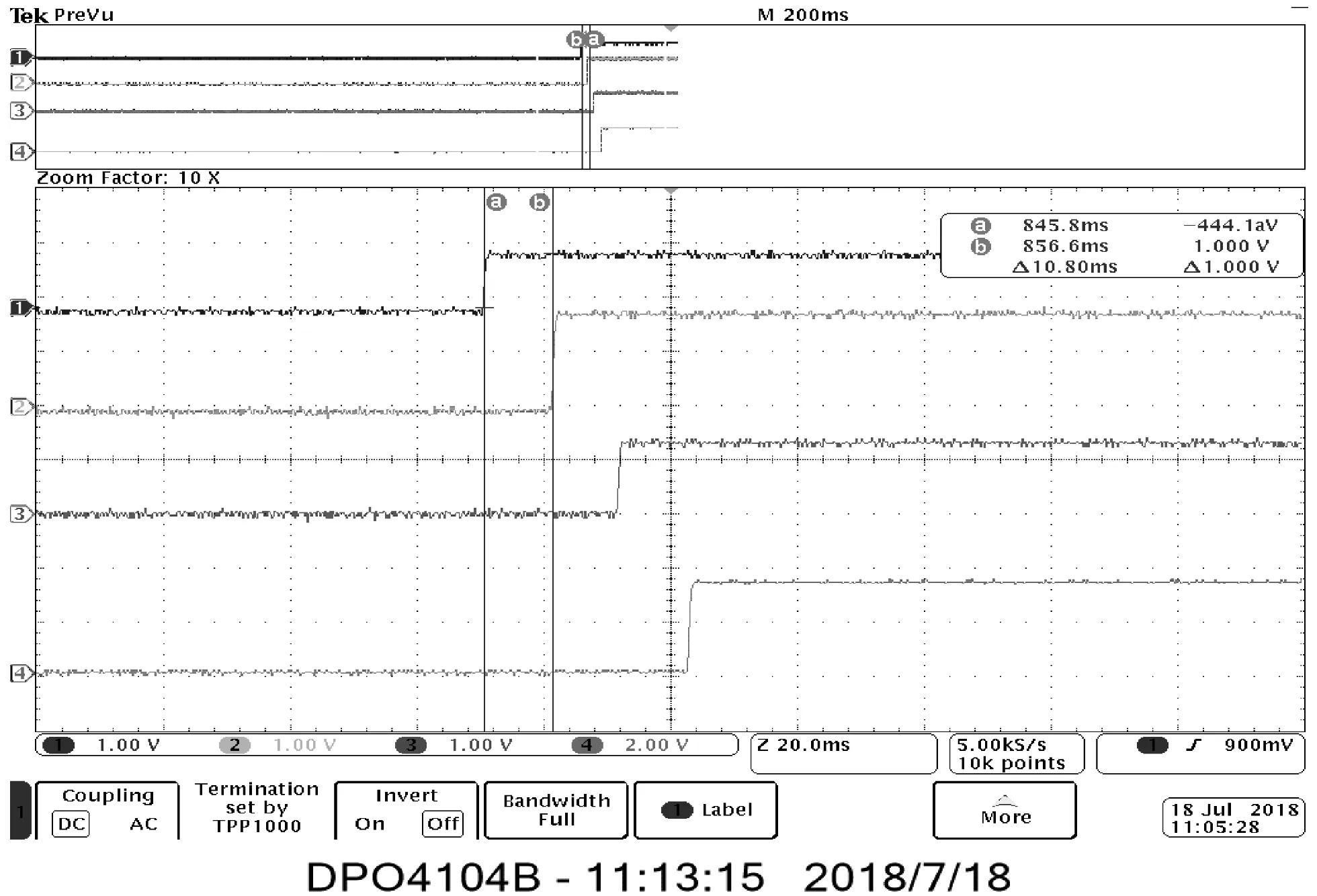

本设计的试验结果包括如图3所示的上电波形和图4所示的下电波形。

图3 上电顺序波形

图4 下电顺序波形

结 语