电子战宽带数字信道化的优化设计方法

2018-11-29周新星谢祖刚邱耀明

周新星,谢祖刚,邱耀明,曹 凡

(中国船舶重工集团第七二二研究所,湖北 武汉430205)

0 引言

现代电子战面临的信号环境越来越复杂密集,基于宽带数字阵列体制的电子侦察系统成为发展趋势,该系统要求侦察接收机必须具有很宽的瞬时处理带宽、高灵敏度、大动态范围,且为了测向和DBF,要求通道间一致性好。宽带数字信道化接收机由于覆盖带宽宽、多信道并行处理、能有效检测跳频突发信号且易于实现高增益多波束及测向,而在宽带数字阵列侦察系统中得到越来越多的应用[1-3]。

宽带数字信道化接收机对频带进行无盲区子带划分,信道数目以及信道的抽取因子是其关键因素。信道数目决定了多相支路的个数,抽取因子决定了滤波器的特性和阶数以及后端传输处理的数据量。传统的数字信道化方法由于多相支路多,每路的抽取因子大,导致滤波的数据率低,占用大量的计算资源,不利于瞬时处理带宽的扩展;且滤波运算速率与FFT速率不匹配,需额外的硬件资源进行转换,增加了实现的复杂度[4-5]。为此,本文提出一种高效的宽带信道化设计方法,在推导任意过采因子信道化模型的基础上,对各多相支路进行优化,设计新的多相支路结构,提高支路的吞吐率,降低硬件资源的开销,并且新结构使得信道化的滤波、FFT等运算都工作于同一速率上,使设计便于实现,增加了信道化处理的可扩展性。某系统中的硬件实现验证了该设计方法的有效性。

1 过采因子任意的信道化接收机

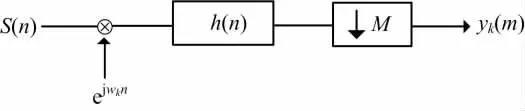

侦察接收机为提高信号的截获概率,采用无盲区的均匀信道划分,各信道的通带无缝相邻,过渡带重叠。过渡带的重叠大小决定了各信道的抽取因子和信道输出的数据率,过渡带重叠越小,则信道的抽取因子可越大,后端处理数据量越小,相应地原型滤波器的阶数越高。设系统划分信道数目为K,信道的抽取因子为M ,定义过采因子为F,F满足K=FM 。第k个信道的示意图如图1所示。其中wk=-2πk/K,k=0,1,2,…,K -1。

图1 信道k的示意图

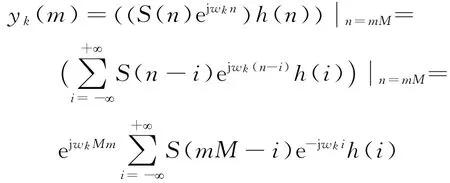

信道k的输出为:

令i=qK +p,q=(-!,+!),p=0,1,2,…,K-1,则有:

式中,珔hp(m)具有如下形式:

可见,hp(q)是由原型低通滤波器h(n)按K 倍抽取得到的第p支路的系数;进一步对hp(q)内插F倍,即得到系数h-p(m);Sp(m)是由输入S(n)按 M倍抽取得到的第p支路的信号。上述p的取值范围为p=0,1,2,…,K -1。

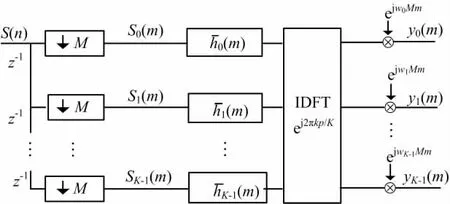

根据以上推导,得到过采因子任意的信道化接收机模型如图2所示。

图2 过采因子任意的信道化接收机模型

2 优化的信道化多相结构设计

本节在选取过采因子的基础上,分析传统多相结构信道化接收机存在的处理速率低、占用资源多等问题,然后提出优化的信道化设计方法。

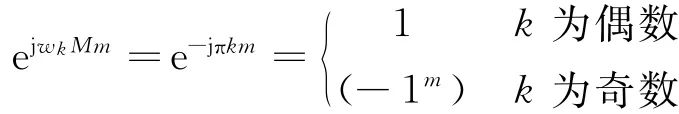

过采因子的选择对信道化的实现复杂度及系统计算量有直接影响,文献[5]从理论上分析了过采因子与系统计算量的关系,但未考虑系统的可实现性。由于FPGA硬件中各多相支路的数据是通过移位寄存器链或RAM来进行整形排列,过采因子选取不当会导致实现的复杂度急剧增加甚至无法实现,也不利于提高处理速率[6-7]。综合考虑,这里选取过采因子F=2,此时原型低通滤波器的过渡带宽度与通带相等,相邻信道重叠一半。对于F=2,图2中的指数项ejwkMm变为:

此时信道化接收机模型如图3所示。

图3 过采因子为2的信道化接收机

图3 直接用于硬件实现的主要问题是占用资源多、处理速率低、速率不匹配。设图中宽带输入信号的采样率为fs,信号依次延迟分别进K个支路,则每个支路的数据率为fs/M 。由于支路个数多达K 路,导致I/O和串并转换消耗较多资源。K个支路独立并行卷积运算,需占用大量的DSP计算资源,若原型低通滤波器的长度为L,则卷积运算共需使用2L个实数乘法器,这是很大的乘法器开销,尤其在数字阵列系统中,其占用的乘法器资源将急剧增加。再者,IFFT的串行输入数据率为2fs,这与支路的数据率不匹配,增加了系统实现的复杂度。

为此,提出信道化接收机的优化设计方法,从3个方面来改进传统信道化的结构。一是减少多相并行支路的路数,这可降低I/O数量和串并转换资源开销。由于支路K/2至支路K-1的输入信号是支路0至支路K/2-1的输入信号的一个样点的延迟,所以可将多相支路的路数减少一半,由K 路降为K/2路。同时,可根据处理带宽和支路数据率进行支路复用,进一步减少支路路数。二是提高卷积运算的处理速度,以降低乘法器的开销。乘法器是FPGA的主要计算单元,是系统设计的首要考虑因素,若卷积运算的速度提高至N倍,则需要的乘法器数量将降为1/N 倍。可通过提高支路的卷积输入数据率来实现乘法器在多个支路间的复用,乘法器工作于较高速率,分时对多个支路的信号进行滤波。三是将支路滤波的速率与IFFT运算的速率设计为一致,这可避免跨时钟转换的问题,降低系统复杂度。设宽带输入信号的采样率为fs,有N 个多相支路,则各支路的滤波速率为fs/N ,且IFFT的等效总速率为2fs,因此使用2fs/(fs/N)=2 N个IFFT模块即可保证IFFT与卷积滤波的速率相一致,使信道化的全部运算工作于相同速率上。

3 应用分析

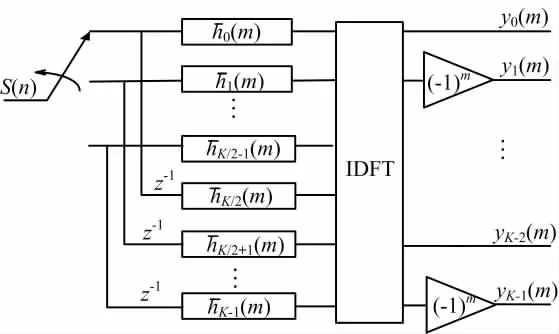

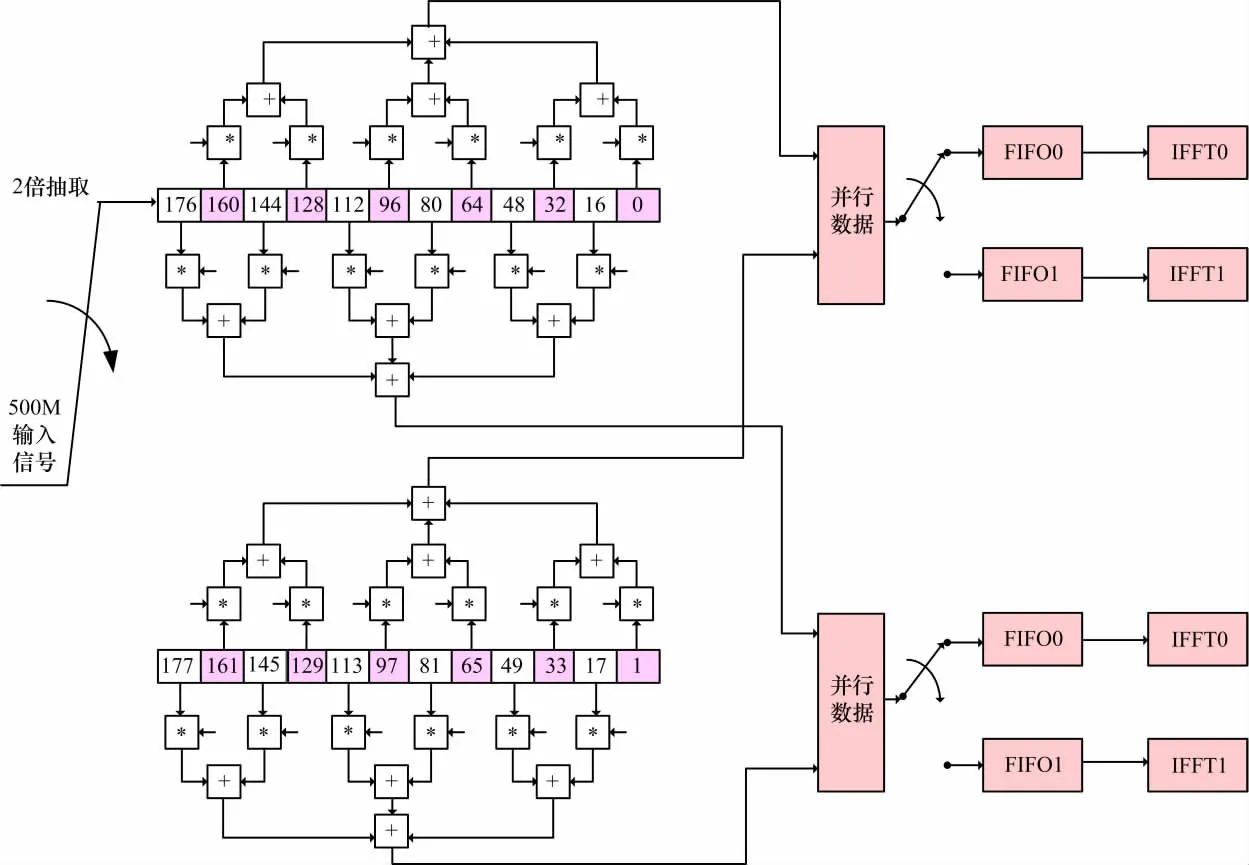

以某系统中信道化接收机的具体设计来分析验证本文方法的可行性。信道化的输入宽带IQ信号采样率为500M,划分32个子信道,原型低通滤波器的阶数为为191,FPGA采用Xilinx V7系列。依据提出的优化设计方法,得到信道化接收机结构图,如图4所示。

图4中,输入信号以2路并行的形式送给2个多相支路,每个支路的数据率为250M,各支路接24个实数乘法器进行滤波运算,2个支路一共使用48个实数乘法器。乘法器的输入系数每个周期更新一次,系数的存储深度为16。支路的延迟抽头通过移位寄存器链实现,抽头间隔为8。2个支路每个周期并行输出2个卷积结果,16个周期产生一帧IFFT所需的32个样点。各支路分为上卷积部分和下卷积部分,上卷积部分用于产生偶数帧IFFT所需的数据,下卷积部分用于产生奇数帧IFFT所需的数据。共使用4个IFFT模块。系统中卷积和IFFT等所有处理都工作于250M速率。

图4 优化的信道化接收机结构图

与图3所示的传统信道化接收机结构进行比较。依据图3来设计,则并行多相支路路数为32,每个支路的数据率为31.25M,各支路接12个实数乘法器,卷积运算共需384个实数乘法器。由于32个支路滤波输出的等效速率为1G,即IFFT总的速率需达到1G,若IFFT模块的处理速率与支路滤波的速率相同,则需要的IFFT模块数量多达32个。另一方面,若减少IFFT的资源开销,则其速率与卷积运算的速率不一致,会引入跨时钟问题。

在FPGA中实现了如图4所示的信道化接收机。利用宽带LFM信号对其进行在线实测,从ILA采集的信道化处理后各信道的输出结果可以看出,所设计的信道化接收机功能正确。

通过某系统中信道化接收机的具体设计及实现,提出的方法的优势得到了验证:相比传统的信道化接收机,本文方法能大幅降低硬件资源的开销,处理速率匹配便于应用实现,尤其在处理大带宽高采样率信号时优势明显;且当瞬时带宽增加或信道数发生变化时,本方法除滤波器系数发生改变外,所设计的处理结构基本不变,增加了可移植性。

4 结束语

宽带数字阵列侦察系统逐渐成为电子侦察的发展方向,而宽带数字信道化接收机作为该系统的重要组成部分,是实现高灵敏度接收、形成高增益多波束、DF、处理突发跳频信号等功能的关键。针对传统宽带数字信道化接收机存在的占用硬件资源多、实现复杂、吞吐率不高的问题,本文在推导任意过采因子信道化接收机模型的基础上,提出信道化的优化设计方法,减少多相支路的个数,提高滤波速率,并使信道化的所有运算处理都工作于相同速率。本设计方法在某系统中进行了验证,结果表明能节省硬件资源、处理速度快、便于实现,该方法在宽带数字阵列侦察系统中有实际应用价值。■