ZnO 自整流忆阻器及其神经突触行为

2018-11-02,,,,,,,,,

, ,, , ,,,,,

(1.江苏大学材料科学与工程学院,江苏 镇江 212013; 2.江苏星源电站冶金设备制造有限公司,江苏 靖江 214500; 3.江苏科技大学 材料科学与工程学院,江苏 镇江 212013; 4.中国科学院宁波材料技术与工程研究所,浙江 宁波 315201)

1 引 言

忆阻器具有电阻量纲,其阻值会随流经电荷发生非线性变化,被广泛应用于信息存储和神经突触模拟[1-10]。通常情况下忆阻器件发生阻态变化主要是因为在电场作用下离子的迁移或者焦耳热引发的相变,这一过程涉及到材料微结构的变化,因此器件工作不稳定,工作参数发散。此外,随着忆阻器集成度的提高,电路中的串扰电流问题日益突出[11],通常在电路中串联二极管、晶体管等选通元件来抑制串扰电流,但是,这不可避免会严重限制器件的集成度,较为理想的办法是通过忆阻器自身的整流特性来抑制电路中的串扰电流[12-14]。ZnO忆阻器具有优异的忆阻特性,在信息存储和突触模拟领域得到广泛研究[15-19]。本研究制备了Ti/ZnO/AZO/Pt结构忆阻器,器件表现出无Forming及自整流的非易失双极性忆阻特性。进一步研究了器件工作机理,以及神经突触行为。

2 实 验

先以纯度99.99 wt%的ZnO∶Al (3wt.% Al2O3)陶瓷片作为溅射靶材,镀Pt硅片(Pt/Ti/SiO2/Si)作为衬底,采用直流磁控溅射的方法,在室温下制备了厚度为30nm 的铝掺杂ZnO(AZO)薄膜做为ZnO功能层的缓冲层。磁控溅射腔体本底真空度低于2×10-4Pa,高纯Ar/O2混合气体作为溅射气氛,两种气体的分压比为Ar∶O2=8∶2,溅射气压为0.4Pa,溅射功率80W。再以纯度99.99wt%的ZnO陶瓷片作为溅射靶材,在AZO上采用相同的分压和溅射功率制备厚度为50nm的ZnO薄膜做为忆阻器的阻变层。最后采用电子束蒸发结合金属掩膜板的方法,在ZnO薄膜表面依次沉积金属Ti和Au,厚度分别为30nm和 10nm,Ti/Au电极尺寸为100μm。其中Au作为保护层,防止顶电极Ti在空气中氧化。利用Keithley 4200半导体参数分析仪测试Au/Ti/ZnO/AZO/Pt器件的电学性能以及进行“突触”实验,底电极Pt接地,在Au/Ti顶电极上施加电压,电压正向定义为电流方向从顶电极流向底电极。

3 结果与讨论

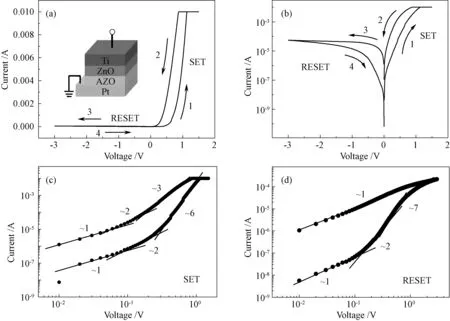

图1(a)和(b)为Ti/ZnO/AZO/Pt自整流忆阻器件分别在线性和单log坐标下的I-V曲线,器件表现出自整流、非易失的双极性电阻转变特性。器件最初处于高阻态,初始阻值约为3×106Ω(读取电压为-0.1V)。器件不需要一个电压较大的Forming(从初始高阻态转变为低阻态)过程,从而有利于实际应用。电压先从0V开始扫描,器件阻值发生缓慢变化,约1.1V到达限流(为了防止器件被击穿而设置的最大电流值,这里设为0.01A),器件从高阻态转变为低阻态,此时电阻约为1.4×104Ω,这一电阻转变过程称为SET。然后对器件施加负向电压,器件从低阻态缓慢转变为高阻态,这一过程称为RESET。由图可见,器件表现出明显的整流特性。为了探究Ti/ZnO/AZO/Pt器件的导电机制,对SET和RESET过程的I-V曲线进行了双log坐标拟合,如图1(c)和(d)所示, SET的高低阻态以及RESET的高阻态I-V曲线和陷阱控制的空间电荷限制电流(SCLC)导电模型较为吻合[20-23]。SCLC机制的I-V特性曲线一般可以分成三个不同的区域:电流与电压成线性关系(I∝V),电流与电压的平方成正比(I∝V2),电流随电压迅速增大(I∝Vn,n>2)。当外加电场较低时,注入的电子较少,由于ZnO薄膜中缺陷的存在,注入的电子被陷阱俘获,薄膜中自由电子浓度较低,因此电流较小,器件处于高阻态;当外加电场逐渐增大,薄膜中的陷阱被全部填充时,注入的电子都可以成为自由载流子,因此使流经器件的电流急剧增大,器件由高阻态转变为低阻态。

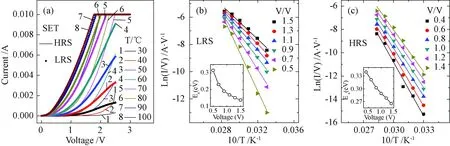

为了进一步研究Ti/ZnO/AZO/Pt忆阻器件的导电机理,测试了器件SET过程高低阻态电流随温度的变化关系,如图2(a)所示。由图可见,随着温度升高,器件的高低阻态电阻都减小,表现出典型的半导体导电特性,因此可以排除Ti/ZnO/AZO/Pt器件的阻变行为来源于导电细丝形成和断裂的可能性。

图1 (a) Ti/ZnO/AZO/Pt自整流忆阻器件线性坐标I-V特性曲线(图中数字表明电压扫描顺序,插图为器件的结构示意图); (b) 单对数坐标下的I-V特性曲线; (c) (d) 双对数坐标下SET和RESET过程Fig.1 (a) Typical I-V characteristics of Ti/ZnO/AZO/Pt devices in linear scale. The inset schematically illustrates the device structure. (b) The corresponding I-V curve in semilogarithmic scale. (c) (d) I-V curves of the SET and RESET processes replotted in double-logarithmic scale

为了获得ZnO薄膜中准确的缺陷能级,据图2(a)在30~80℃温度范围内的实验结果,按照阿伦尼乌斯公式(I=I0exp(Ea/RT),I为电流,I0为指前因子,Ea为激活能,R为摩尔气体常量,T为绝对温度)进行了拟合分析,结果见图2(b)、(c)。结合高阻态和低阻态的拟合结果,计算出薄膜中缺陷的激活能为0.12~0.34eV(图2(b)和(c))。通常认为,ZnO薄膜中施主缺陷主要为锌间隙(Zni)和氧空位(VO),Zni属于浅能级缺陷,而VO属于深能级缺陷,距离导带底>0.2eV[24]。因此,分析结果表明,在Ti/ZnO/AZO/Pt器件电阻转变过程中,ZnO薄膜中分布在导带底0.12~0.34eV范围内的Zni和氧空位VO施主缺陷俘获和释放电子,从而发生高低阻态之间的可逆变化。

图2 (a) Ti/ZnO/AZO/Pt器件SET过程高低阻态随温度变化曲线(温度范围为30~100℃); (b) (c) 根据阿伦尼乌斯公式分别拟合(a)中低阻态和高阻态电导(插图为激活能随电压的变化关系)Fig.2 (a) I-V curves of the high resistance state (HRS) and low resistance state (LRS) during the SET process of Ti/ZnO/AZO/Pt measured at temperatures in the range of 30~100℃. (b) (c) Arrhenius plots of the conductance of HRS and LRS calculated from (a). The insets show estimated activation energy versus voltage plots

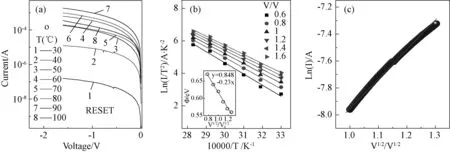

图3 (a) Ti/ZnO/AZO/Pt器件RESET过程低阻态电流和温度的关系; (b) Ln(I/T2)和1/T之间的变化关系,电压区间为0.6~1.6V,温度范围是30~80℃(插图为肖特基势垒(Φ)与电压的变化关系);(c) LnI和V1/2之间的变化关系Fig.3 (a) I-V curves of the LRS during the RESET process of Ti/ZnO/AZO/Pt measured at different temperatures. (b) Ln(I/T2) versus 1/T plots at voltages ranging from 0.6 to 1.6V. The inset shows the Schottky barrier height versus voltage plot. (c) LnI versus V1/2 plot

由图1(d)可知,Ti/ZnO/AZO/Pt 器件RESET过程低阻态并不符合SCLC机制。为了探究低阻态的导电机制,测试了不同温度下(30~100℃)的I-V曲线,如图3(a)所示。随着温度的升高,低阻态阻值逐渐减小,符合半导体导电特性。由于I-V曲线具有整流特性,很自然考虑采用肖特基发射公式来拟合低阻态不同电压下的I-V曲线[25]:I=A*sT2exp(-q(ΦB-(qV/4πdε0εr)1/2)/kT),其中A*为有效理查森常数,s是器件面积,T是绝对温度,q是电子电荷,ΦB是界面势垒高度,d是薄膜厚度,ε0是真空介电常数,εr是静态介电常数,k是玻尔兹曼常数。由上述肖特基发射公式推导可知,Ln(I/T2)和1/T呈现线性关系,这也是肖特基发射机制的重要判据。如图3(b)所示,在不同电压下,Ln(I/T2)和1/T均呈现明显的线性关系,表明低阻态电学行为符合肖特基发射机制。图3(b)插图为肖特基势垒高度随外加电压的变化情况,可以推导出零电压下Ti与ZnO界面处的肖特基势垒高度为0.848eV。此外,LnI和V1/2也呈现明显的线性关系,如图3(c)所示,进一步验证了RESET过程中低阻态导电符合肖特基发射机制。对于Ti/ZnO/AZO/Pt 器件自整流的形成,一般认为来自于Ti/ZnO界面的肖特基势垒[26]。AZO层的电阻率为10-3Ωcm量级,表现出半金属特性,ZnO/AZO及AZO/Pt界面形成欧姆或准欧姆接触,因此,AZO层的存在保证了器件整流特性的形成。

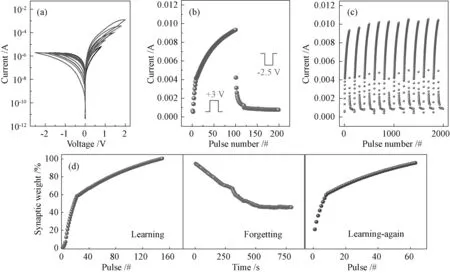

通常认为突触是大脑学习记忆的最小单元,而突触学习记忆的重要方式就是依赖其自身的可塑性。可塑性是指突触接收外界刺激后,可以调整自身形态的能力[27]。如图4(a)所示,先对Ti/ZnO/AZO/Pt器件施加连续增加的正向电压,器件的电阻逐渐减小,随后施加绝对值连续增加的负向电压,器件的电阻逐渐增大。电阻态的连续可调,表明器件可以用来模拟生物神经突触的功能,其电导可以看作是突触的权重。基于Ti/ZnO/AZO/Pt忆阻器,模拟了神经突触长程增强和抑制行为,如图4(b)所示,通过对忆阻器施加连续100个正向脉冲和100个负向脉冲,发现器件电流呈现连续增加和减小。图4(c)为突触器件长程增强和抑制行为的10次循环。图4(d)模拟了突触的学习-遗忘-再学习过程,开始的连续160个脉冲刺激可看做是人工神经突触的训练过程,训练后的突触权重值被看作是100%的记忆量,这类似于人脑的学习过程,撤去脉冲刺激后,器件的权重逐渐降低,即记忆量随时间衰减,这个变化曲线类似于人脑的遗忘过程。经过750秒后,记忆量的衰减变得非常缓慢,最终保持在初始记忆量的35%,表现出长程可塑性。当再次施加脉冲时,只需要较少脉冲数,约60个脉冲刺激,突触器件就可以到达之前100%记忆量,类似于人脑的再学习过程。这种学习-遗忘-再学习的过程可被用于未来人工神经网络的学习和识别功能中。

图4 (a) Ti/ZnO/AZO/Pt突触器件在不同电压扫描下的I-V曲线; (b) 施加连续正向和负向脉冲导致器件电流变化,正负脉冲幅值分别为3V和2.5V,宽度180ms,读脉冲幅值1.5V; (c) 100次正向脉冲和100次负向脉冲交替施加条件下器件电流变化;(d) 器件学习、遗忘、再学习行为,刺激和读脉冲幅值分别为3V和1.5VFig.4 (a) I-V characteristics of Ti/ZnO/AZO/Pt measured by a modified voltage sweep. (b) Positive and negative pulse induced current change. The amplitudes of positive and negative pulses are 3 and 2.5V, respectively. The pulse width is 180ms. The amplitude of the read pulse is 1.5V. (c) The current change induced by alternately applying 100 positive and 100 negative pulses. (d) The learning-forgetting-relearning process of Ti/ZnO/AZO/Pt synaptic devices

4 结 论

Ti/ZnO/AZO/Pt忆阻器件表现出无Forming、自整流、非易失的双极性电阻转变特性。I-V曲线的拟合以及变温测试结果表明,器件的导电行为来源于空间电荷限制电流或肖特基发射机理,属于纯电子忆阻行为。利用Ti/ZnO/AZO/Pt忆阻器件模拟了生物神经突触的长程可塑性以及学习-遗忘-再学习经验式行为。