基于FPGA快速中值滤波算法的硬件实现

2018-10-31赵亮刘鹏王晓曼刘美

赵亮,刘鹏,王晓曼,刘美

(长春理工大学 电子信息工程学院,长春 130022)

图像采集处理系统大部分均采用实时图像采集技术,图像采集的速度、质量直接影响到产品的整体效果[1]。图像信号处理类的低层信号处理运算主要面对图像像素操作[2],此类运算的特点是数据量大但运算简单。计算机很难实时处理视频图像数字化后带来的庞大数据量,然而FPGA技术因其众多的优点在图像处理方面有广泛的应用[3]。

中值滤波基于排序统计理论,其核心运算是以模板中的数据进行大小排序,利用亮点(暗点)的数值一般偏大(偏小)使得某个亮点(暗点)噪声经过排序后处在数据序列的两侧,从而达到滤除脉冲噪声的目的。传统的算法是对像素值进行比较和交换,经过几次比较和交换后求出中值,典型的算法有冒泡排序、插入排序等。但此类算法有个共同的缺点,就是当前的比较必须基于上一次比较的结果。如果使用通用的软件方法处理这种算法则需要大量的时间,特别是对于大窗口的中值滤波算法。对此,李轶博等人提出了一种基于FPGA的快速中值滤波器设计方法,利用行缓冲的方式实现了3×3模板矩阵,并采用3级流水操作提高了图像处理的速率和单位时间内处理数据量的吞吐能力[4]。侯法柱等人提出了基于FPGA的改进算法,其先对每行进行了排序并根据排序后的大小特点去除不可能的值,然后再对少量的值进行排序。最终需要16次比较可以找到9个元素的中值。其设计在刚开始时需要9个时钟生成3×3的滤波窗口,之后会每相隔3个时钟周期就会产生一个新的窗口[5]。韩团军提出了一种快速中值滤波算法,其对图像的二维阵列,先进行一次列排序运算,再进行一次行排序运算,最后再将对角线的像素去中值输出[6]。

本文提出了一种基于FPGA的快速中值滤波器设计方法。设计将窗口中每个数据独立运算,分别求出每个数的情况,结合中值在有序序列中处于中间位置这一特殊性,只需1个时钟周期便可以输出3×3窗口的中值。该设计提高了图像处理的效率和单位时间内的处理数据量的吞吐能力。设计方案已经成功应用于某新型零飞仪的视频采集系统,使用效果很好。

1 FPGA硬件实现

1.1 系统设计

本系统利用CMOS相机采集图像,并通过Camlink接口与采集板相连。由DS90CR288将LVDS信号转换为FPGA支持的TTL信号。经过中值滤波等预处理后送至DSP进行高层算法处理。为了观察实验结果,直接将数据送出显示。该系统主要分为三个部分:图像采集、图像处理、图像显示。系统整体框架如图1所示。

图1 系统整体框架

1.2 图像采集部分

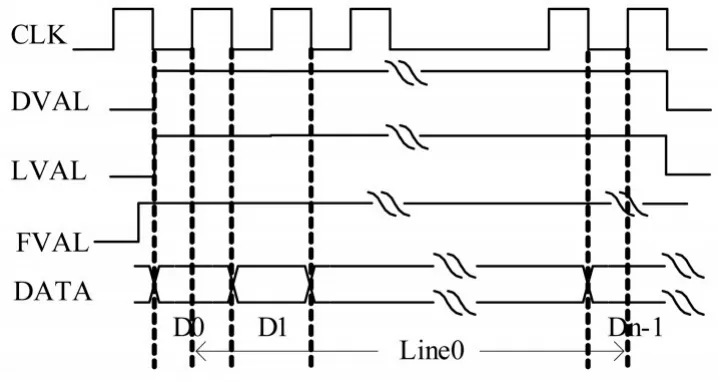

本系统通过mega128单片机配置相机,其主要需要配置的寄存器为通用模式寄存器和触发模式配置寄存器。配置成功的相机便可开始正常工作,相机的输出视频时序信号如图2所示。

图2 数字视频时序信号

相机的输出信号主要分成3类,像素时钟CLK、数据信号DATA以及控制信号FVAL、LVAL、DVAL。场有效信号FVAL在一帧图像数据传送期间为高电平,并且先于有效数据4个时钟周期到来。行有效信号LVAL为高后数据开始传送,并且数据在CLK上升沿到来时最稳定。其中FVAL、LVAL是设计3x3窗口模块、中值模块以及输出模块主要的时序参考。但相机采用的Camlink接口输出的信号均为差分信号,所以系统采用DS90CR287以及DS90LV019将LVDS信号转换为FPGA和单片机支持的TTL信号。

1.3 行列计数器

行列计数器模块的功能在于记录当前所在的行和列,以便各个模块区分边界非边界。

行列计数器的工作情况如下:

(1)在场有效信号FVAL上升沿到来时,行列计数器同时清零,准备接收下一帧图像的数据;

(2)行有效信号LVAL上升沿到来表示下一行数据到来,行计数器加1;

(3)当行有效信号LVAL为高时,每一个像素时钟CLK上升沿的到来,列计数器都会加1。直到LVAL为低时,列计数器被清零,以准备接收下一行的数据。

1.4 3x3窗口

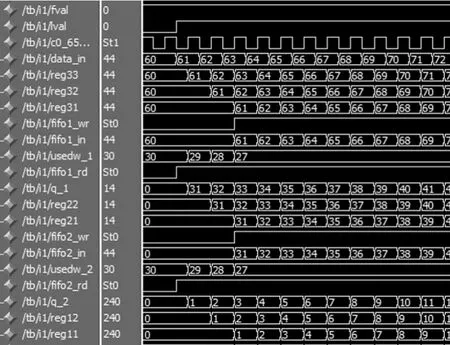

3x3的窗口用于产生滤波模块所需的9个数据。窗口由两个FIFO、7个移位寄存器以及两个2选 1多路选择器组成,分别是 fifo1、fifo2,reg33、reg32、reg32、reg22、reg21、reg12、reg11 以及两个Mux2,如图3所示。

图3 3x3滤波窗口的实现

图3中的R33、R32、R31、R23、R22、R21、R13、R12、R11则是3x3窗口的9个8位输出数据,用于送给中值模块求出中值。使用嵌入式存储器FIFO来实现移位寄存器块,它能节省逻辑单元LE和布线资源,提供了更加有效的实现方法[7]。由于图像数据data_in是以数据流的形式依次进入的,使用图3的结构就可以方便地取得9个窗口数据。同时,行有效期间,每个FIFO读出数据的同时下一行数据会更新此FIFO中的数据。每个FIFO中缓存一行图像数据。下面以30x10的分辨率为例分析。

窗口数据产生步骤如下:

(1)将第一行、第二行的数据直接存入FIFO。

当Row_cnt的值为1且FVAL、LVAL均为高时,fifo2的写使能,第一行数据直接存入fifo2。当Row_cnt的值为2且FVAL、LVAL均为高时,fifo1的写使能,第二行数据直接存入fifo1。即除第一二行是直接存入FIFO外,其余有效数据均是先经过FIFO前的移位寄存器缓存后进入FIFO的。

(2)第三行及以后每行的数据经过reg33、reg32、reg31后打拍后再存入fifo1。同时fifo1的数据经过reg22、reg21打拍后存入fifo2。

(3)通过图3的R33、R32...R11便可以产生9个窗口数据。

3x3窗口的设计重点在于对两个FIFO读写时序的控制,从而使得有效的图像数据存入FIFO中。同时,还需要将三行数据对齐,否则产生的窗口数据是无效的。

FIFO读写控制如下:

(1)FIFO读使能

本文在行有效信号LVAL到来的同时将FIFO读使能。这样,第一个时钟到来时reg33端口的值即为每行的第一个数据,两个FIFO的输出端口也是每行的第一个数据,这样三行数据便可对齐。

(2)FIFO写使能

什么时刻使能FIFO的写信号才能避免无效的数据写入FIFO。本文在行有效信号LVAL有效后的第三个时钟上升沿将两个FIFO的写使能,每行的第一个数据在下一个时钟就会存进FIFO,并且避免了无效的数据写入FIFO中。通过FIFO的epmty和wrusedw可以观察FIFO是否已经读写的情况。在FIFO写使能的下一个时钟,empty将会由高变低,同时wrusedw会由0变成1,说明已经写进一个数据。在写有效而读无效的情况下,每一个像素时钟的到来都会使wrusedw加1,直到写无效其值保持不变。通过观察wrusedw的值是否30而来判断是否成功将一行数据写入FIFO中。在读写同时使能时,3x3窗口数据生成并开始移动时,不断生成新的窗口数据。此时wrusedw的值会一直保持在27。

(3)关闭FIFO的读使能

在每行数据的末端,即FIFO读出每行的最后一个数据后,关闭读使能,窗口停止工作,不再移动。

(4)关闭FIFO的写使能

在关闭FIFO读使能后由于每行的最后两个数据还没有写进FIFO,所以wrreq在LVAL为低后的第三个像素时钟上升沿关闭,观察wrusedw会发现,值变为30,并且在行消隐期间值保持不变。即FIFO中存入了每行的30个有效数据。3×3窗口仿真的时序图如4所示。

图4 3x3窗口仿真图

1.5 中值模块

中值模块采用并行的9个模块将3x3窗口送来的9个数值比较求出中值,并在下一个像素时钟CLK的上升沿将中值输出。由排序理论可知,经过排序后的中值必然处在序列的中间位置。也就是说有序序列中间位置上的值必然为中值,如图5所示。

图5 中值位置显示

有序序列中值的几种不同情况:

(1)如果小于该数的数有4个,那么大于等于它的必然也是4个,此值为中间值;

(2)如果小于该数的数少于4个,但是加上等于此数的数后大于等于4个,此值为中间值。

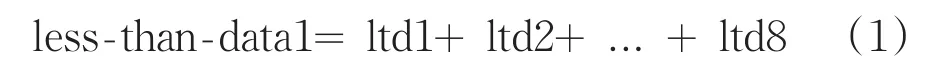

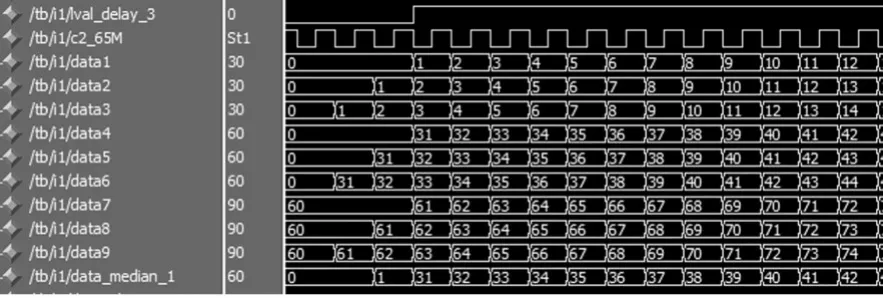

所以只需知道小于该数和等于该数的数有几个即可判断此数是否为中间值。并且在所有的9个数中,必然有且只有一个数满足上述两种情况的一种,即必定会通过计算出的值找出9个数中的中值。以3x3的窗口为例,首先将3x3窗口内各像素分别定义为 R1C1、R1C2、R1C3、R2C1、R2C2、R2C3、R3C1、R3C2、R3C3。各定义在窗口中的位置如表1所示。

设置less_than_data1、equal_to_data1两个寄存器存储小于和等于该数的个数,计算公式如下:

表1 3×3窗口像素位置定义

式(1)中,ltdn(1<=n<=8)表示该数是否大于另外8个数,如果R1C1代表的值大,则ltd1为1,否则为0。式(2)中etdn(1<=n<=8)表示该数与另外8个数是否相等,如果相等,则etd1为1,否则为0。如果less_than_data1为4,表示有且只有4个数比它小,即R1C1代表的值为中值;如果less_than_data1的值小于4,但less_than_data1与equal_to_data1之和大于等于4,那么R1C1代表的值也为中值。设计采用了组合逻辑实现less_than_data1和equal_to_data1的计算。但是为了避免组合逻辑以及走线带来的延迟的不同而导致错误中值的输出,在下一个时钟周期的上升沿时将稳定的中值输出。对于窗口中其他的8个数均可以采用相同的方式计算出less_than_datan(2<=n<=9)和 equal_to_datan(2<=n<=9)。由于窗口中9个数的计算相互之间不存在依赖关系,所以可以并行执行。而之前论文实现中值滤波方式的2级比较会依赖于1级比较的结果,3级比较会依赖于2级比较的结果,必然会增加所需的时钟周期数。所以此方法可以快速计算出中值,在下一个时钟将中值输出,如图6所示。在此仿真中第一个有效的中值为32,而31将会在输出时使用原值。并且输出时钟的上升沿均是数据的中心位置,保证采样时数据的稳定性。

图6 中值输出仿真图

1.6 输出模块

模拟输入数据的时序将滤波后的数据输出。行列计数器的值作为2选1多路选择器的通道选择控制信号,当行列计数器的值为边界时直接将像素点的原值输出,否则多路选择器选择中值输出。调用pll将像素时钟的相位延时180度,使输出时钟上升沿在输出数据中心位置出现。

2 硬件实验结果

实验终端调试及测试。采用文本的算法可以减少计算中值的时钟周期数,将时钟周期数由多个[4-8]缩减至1个时钟周期。本文设计的快速中值滤波器不需要先用SDRAM等外设来缓存一整幅图像,而是采用两个FIFO缓存两行数据,利用不断的更新FIFO中数据来完成对一幅图像的滤波处理。而此种方式可以实现的原因在于中值的连续输出(如图6)使得可以直接模拟相机的输出时序将处理完的数据直接送给终端显示并观察实验结果。系统在第三行数据到来时开始输出中值,并在每个行有效结束后,每个FIFO中的数据均被更新为下一行的数据,直到一幅图像处理结束。最后,对于先将图像存储到SDRAM的方式,例如系统时钟为65M,像素为720×576的图像,采用原来的中值滤波算法处理一整幅图像大概需要18ms,但采用本文的算法大概只需要三分之一的时间,即6ms。通常的视频帧频为25帧/秒,即一帧视频所需的时间为40ms,因此对于先缓存一整幅图像再处理的方式此中值滤波器设计方法也是完全能够满足实时性的要求的。

从实验结果可以看出,有噪声的图像通过此中值滤波系统后图像中的噪声得到了有效的滤除,测试结果如图7所示。

图7 滤波前后效果比较

3 结论

本文充分利用FPGA并行性的特点,采用了独立计算每个数据位置的方法,根据中值在有序序列中处于中间位置这一特性,以EP4CE55F23I7为核心处理器,搭建了中值滤波系统。该系统有效地实现了图像的去噪并且将计算中值所需的时钟周期数降至1个。设计采取了时序电路与组合电路相结合的方法,不仅避免了组合电路毛刺等问题,还可以快速的在像素到来的下一个时钟将上一行对应位置的中值稳定输出,达到了快速抑制噪声的目的。该设计对于的实时图像预处理具有一定的应用价值。