光传送网中ODU1到ODU0的解映射电路的设计与实现∗

2018-07-31韩美林乔成芳

韩美林 乔成芳

(商洛学院电子信息与电气工程学院 商洛 726000)

1 引言

OTN技术对已有的SDH和WDM的传统优势进行了更为有效的继承和组合,能最大程度上满足多业务、大颗粒、大容量、高可靠性的传送需求,相比以往的数字传送网,OTN技术包含了光层和电层的完整体系结构,同时具备了SDH的安全与调度和WDM大容量远距离传送的双重优势,同时可以为数据业务提供最低的时延抖动,更好地满足了目前的互联网需要[3~4]。

虽然OTN具有很多优点,但目前限制其快速发展的主要问题是交换问题。以往OTN采用的是面向连接的电路交换方式,其缺点是网络的带宽利用率低,电路交换时不同数据类型、不同规格、不同速率的终端很难相互进行通信,也难以在通信过程中进行差错控制[5]。因此基于市场和技术的需求本文设计了在OTN分组交换技术的解映射过程中采用一种基于同步时钟产生的均匀缺口时钟来实现解帧[6],将成帧后的一路16位ODU1信号通过异步映射方式去映射为两路8位的ODU0信号供下级电路处理。

2 功能分析

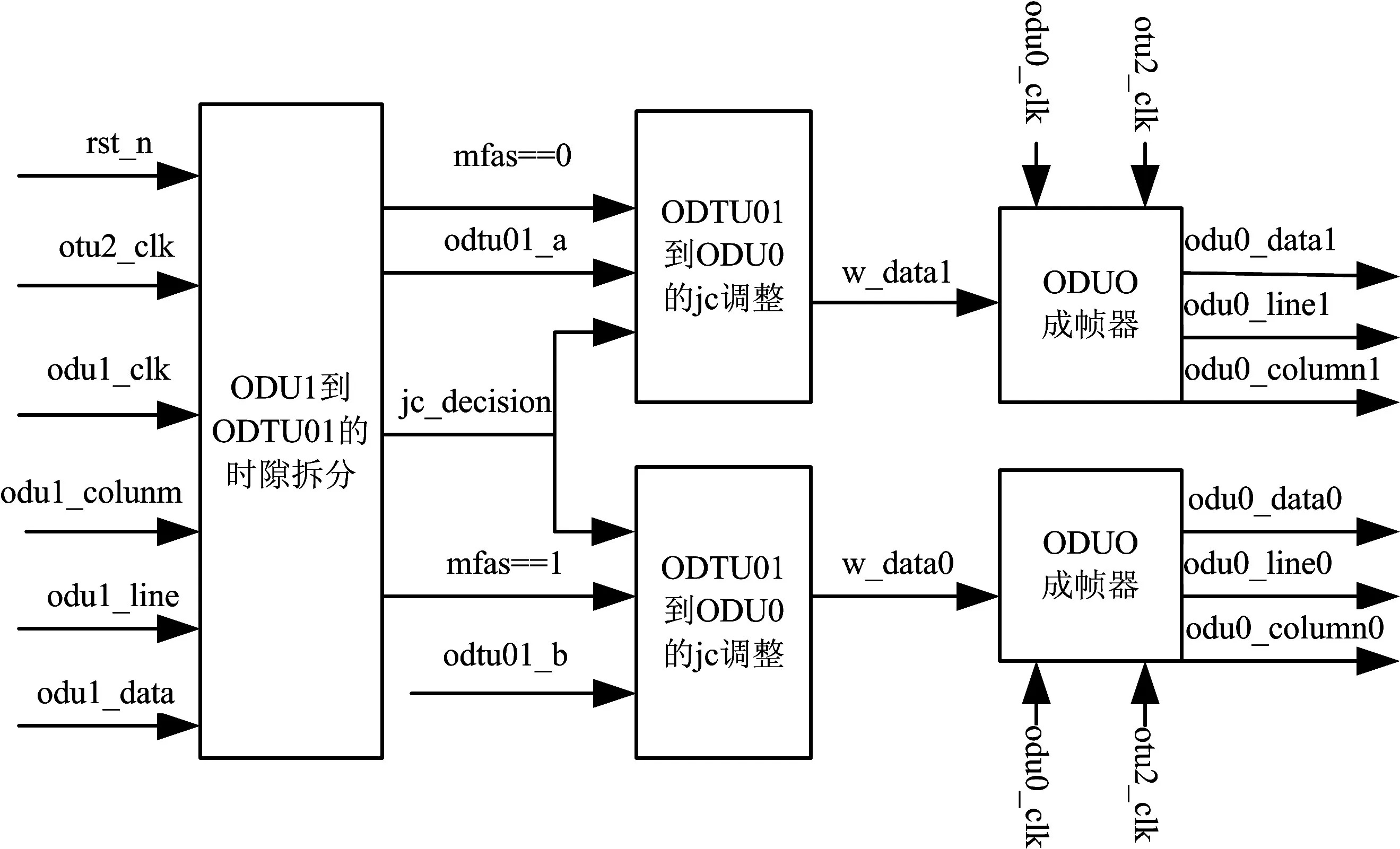

通过对ODU1 remux ODU0模块功能的分析,设计了图1所示的将ODU1信号通过异步映射方式去映射到ODU0信号的总体结构框图。

如图1所示,将ODU1 remux ODU0模块分为三个小模块,分别为一路ODU1到ODTU01的时隙拆分模块,两路ODTU01到ODU0的JC调整模块,两路ODU0的成帧器模块[7]。在输入端,其中otu2_clk和odu1_clk产生与odu1同频的虚拟时钟,odu1_line和odu1_columm是odu1的行列指示信号;od⁃tu01_a、odtu01_b是时隙拆分后支路的数据,mfas是复帧信号。jc_decision是当前帧中JC0到JC3多数判决结果的输出。在输出端,其中otu2_clk和odu0_clk产生与odu0同频的虚拟时钟[8];w_data0、w_data1是JC调整后时间上不均匀的两个支路的ODU0数据;odu0_data0、odu0_data1是odu0成帧后的数据,odu0_column和odu0_line是odu0成帧后的行列指示信号。

ODU0的成帧器模块与ODU1的成帧器模块相似,此处不再重复。ODU1 remux ODU0模块的接口定义及说明如表1所示。

图1 ODU1 remux ODU0模块的总体结构框图

3 ODU1 remux ODU0模块子模块设计

3.1 ODU1到ODTU01的时隙拆分模块设计

根据ODUk帧结构可知,ODU1和ODU0的帧格式相同,均是4×3824,前16列为开销部分,后3808列为净荷部分[9]。2路ODU0数据加上ODU1开销数据组成一路的ODU1数据,根据ODU1的帧结构和ODU1的行列指示去除ODU1的前16列开销数据后将剩余数据根据数据间插的方式拆分为两路8bit的ODTU01数据输出给下级电路使用[10]。并将ODU1的复帧MFAS输出,为JC调整模块做准备。

3.2 ODTU01到ODU0的JC调整模块设计

ODU1帧结构中,在前3行的第16列中存放着对调整字节进行解释的JC开销,G709中规定为了在异步映射中最大程度的减小对调整字节的解释错误[11],用3个JC开销采用多数判决的办法对调整的字节进行一到两个字节的正负调整,从而避免因调整字节的解释错误导致整个客户数据的传错。

ODTU01到ODU0采用3个寄存器JC1到JC3进行多数判决,由接收到的JC开销为高的个数情况进行判决[12]。在第4列时按照之前判决的结果和MFAS最后两位对应的数据进行JC的调整。ODTU01到ODU0的JC调整字节意义具体结构如表 2所示[13]。

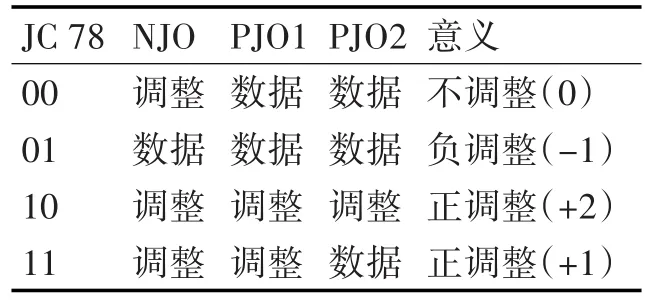

表2 字节调整信息意义

从表2可以看出:当三个JC中至少有两个为00时,判断为不调整,则NJO为开销数据,PJO1、PJO2均为客户数据;当三个JC中至少有两个为01时,判断为负调整,则NJO、PJO1、PJO2均为客户数据;当三个JC中至少有两个为10时,则判断为有两个正调整,则NJO、PJO1、PJO2均为开销数据;当三个JC中至少有两个为11时,则判断为有一个正调整,则NJO为开销数据,PJO1、PJO2均为无效数据[14]。

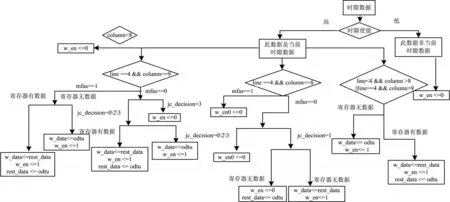

ODTU01到ODU0的JC调整模块具体设计为根据ODU1的行列指示判断是否为开销数据,是开销则直接送给开销模块进行开销的提取处理,然后判断复帧MFAS最后一位对应的数据是否为零,如果为零则将第一行的第八列的最低两位送给jc1、第二行的第八列的最低两位送给jc1、第三行的第八列的最低两位送给jc3。根据多数判决如果至少有两个相等则说明JC判决正确反之则错误[15]。如果jc1、jc2、jc3至少有两个等于0则为不调整,如果至少有两个等于1则为负调整,如果至少有两个为2则为两个正调整,如果至少有两个为3则为一个正调整。详细步骤根据图2所示完成相应的操作。其他一路设计步骤相同不再做说明。

图2 ODTU01到ODU0的一路JC调整模块详细流程图

4 仿真结果分析

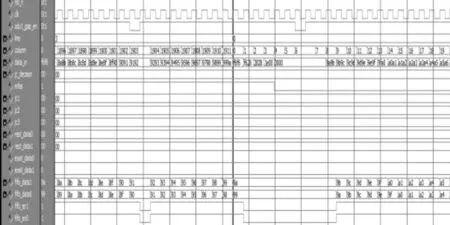

如图3所示为ODU1 remux ODU0模块的电路仿真结果图。odu1_gap_en为ODU1数据的使能信号,data_in为成帧后的ODU1数据流,line和column分别为ODU1数据流的行列指示,mfas为复帧值,jc_decision表示jc1、jc2、jc3调整多数判决的结果,fifo_data0、fifo_data1分别为解复用后没有成帧的ODU0数据流,fifo_en0、fifo_en1分别为ODU0数据流的使能信号。从图中可以看出mfas为00时表示调整第一路ODU0数据,jc多数判决结果为00表示不调整,则fifo_data0数据输出不调整。一路16bit的ODU1数据流去映射为两路8bit的ODU0数据流。

图3 ODU1 remux ODU0模块的电路仿真结果图

5 结语

本文设计并实现了光传送网中ODU1到ODU0的解复用映射电路。仿真表明,本设计能够实时、准确地完成ODU1到ODU0的数据传输,大大减少了锁相环的使用,时钟抖动也较少。同时设计中采用的是Verilog硬件语言,不仅可以有效地缩短设计周期,而且增加电路设计的可移植性。