基于双交叉耦合电容反馈的超低功耗高线性LNA

2018-07-24李相敏

李相敏,康 壮

(长江大学文理学院,湖北 荆州 434020)

0 引 言

反馈的基本作用是利用反馈路径上的线性有源器件,来纠正电路正向路径上的非线性有源器件产生的非线性。反馈是模拟和射频电路中的一种提高线性度的有效方法,然而,在射频领域,反馈可能引起谐波反馈分量,恶化电路的线性度。在低频领域,谐波反馈分量通常被高环路增益所抑制,然而,在射频领域,由于开环增益已经很低,较难取得高环路增益。例如,在共源电路结构中,采用源极退化电感实现的电压电流反馈技术,并不能提高输入三阶截止点IIP3性能,这是因为源极退化电感在放大晶体管的源端产生二次谐波分量,通过晶体管栅源间电容反馈回输入端口,与原始信号相混合转换成三阶交调分量IMD3,退化了电路的IIP3[1-5],在许多射频反馈电路中都存在此类现象[6-7]。

在本文中,首先在线性度改善方面讨论了射频反馈技术,并且提出在全差分共栅放大器中采用双电容反馈技术。第一个反馈环路用于增强电路的跨导gm,所采用的技术即是交叉耦合共栅(CCCG)结构,同时可实现高增益和低噪声。另一个反馈环路在晶体管的源漏两级之间采用CCCG技术实现电压电流反馈,尤其,第一个反馈环路在增强基波信号的同时,可以减弱二次谐波信号的放大,因而减小了影响IIP3性能的二次谐波信号,这就可以利用第二个反馈环路来实现IIP3的提高。

1 电路设计及理论分析

1.1 反馈和IIP3

反馈系统的三阶互调失真截止点AIP3cl为[8]:

(1)

式中,b1为闭环线性增益,b3为闭环三阶非线性系数,a1、a2和a3分别为开环线性增益、开环二阶非线性系数和开环三阶非线性系数,T为反馈环路增益。由上式可见,AIP3cl不仅与开环放大器的三阶非线性有关,还取决于开环放大器的二阶非线性。

在低频电路中,获得较高的环路增益并不困难,因此可以抑制二阶交调失真的影响,然而,在射频领域,较难取得高环路增益,结果导致即使采用了反馈技术,也较难取得较高的IIP3[9],因此,本文需要仔细研究二阶交调对IIP3的影响。

1.2 交叉耦合共栅结构

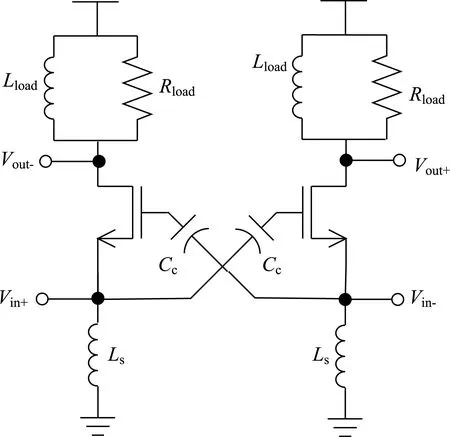

图1给出了一种传统的交叉耦合共栅(CCCG)拓扑结构,CCCG结构将漏极热噪声降低一半,并且通过提高跨导的方式使电路增益增加一倍[10-11],CCCG结构的另一个特性是通过交叉耦合的结构降低二阶交调量。

图1 传统交叉耦合共栅放大器电路图

图2 交叉耦合共栅电路的正向反馈原理

图2为CCCG结构中基波信号和二次谐波信号正向反馈机制的示意图,图中,基波信号的输出电流为:

ifund=gm(vin+A1vin)

(2)

二次谐波信号的输出电流为:

i2nd=gm2(vin-A1vin)2

(3)

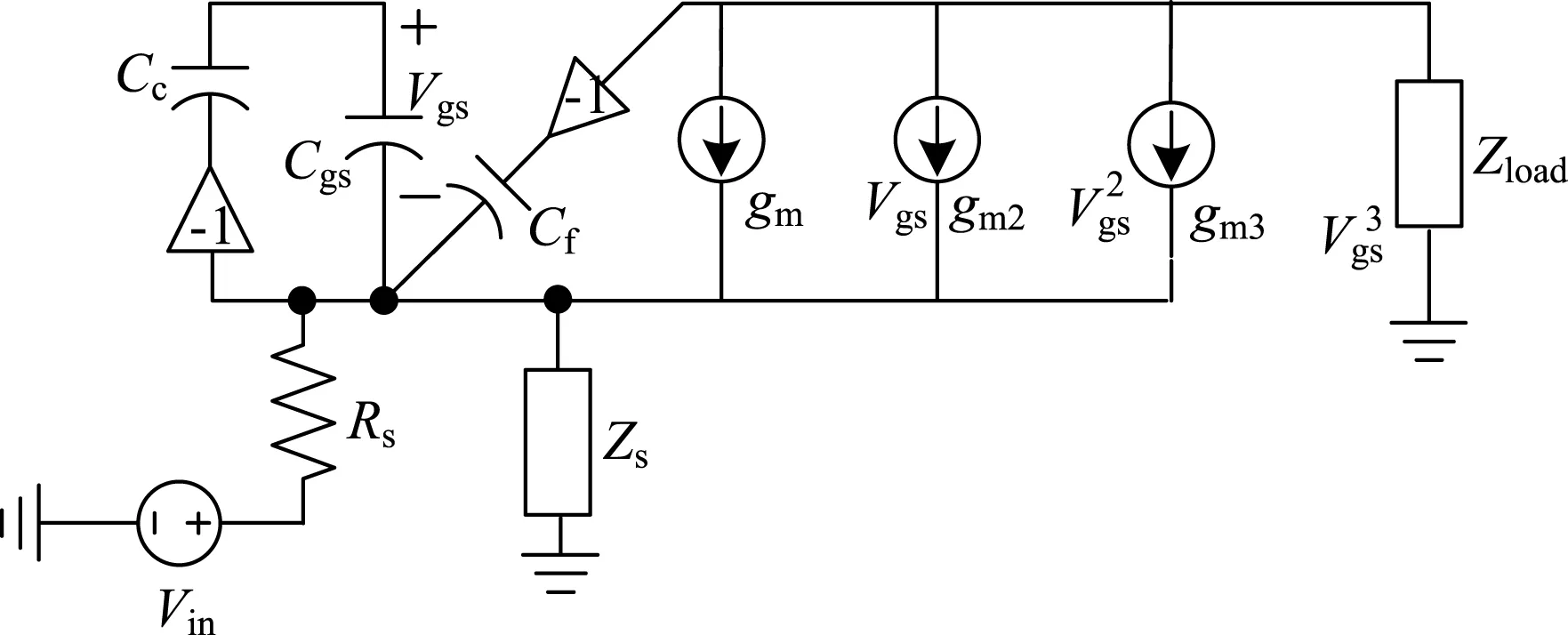

为了对CCCG结构中的非线性进行量化分析,我们采用图3所示的等效半边电路,推导出与CCCG结构相关的如下参数表达式,例如闭环增益b1CCCG,开环增益的一阶系数a1CCCG、三阶系数a3CCCG,环路增益TCCCG以及反馈系数FCCCG。

(4a)

(4b)

(4c)

(4d)

(4e)

其中,Rs为输入源阻抗;2Cc/(Cc+Cgs)为跨导增强系数,如果Cc远大于Cgs,跨导增强系数近似为2。

图3 交叉耦合共栅电路的等效半边电路

由式(1)和式(4)可得,CCCG拓扑结构的三阶互调失真截止点AIP3CCCG如下所示:

(5)

由式(4d)和式(5)可见,如果增加跨导gm,可以增大环路增益TCCCG,进而提高AIP3CCCG。然而,环路增益不仅只与gm有关,还取决于输入阻抗的函数值ZS,因而通过改变环路增益的方式提高线性度效果有限。

1.3 双交叉耦合共栅结构

本文为了克服上述缺陷,提出了在CCCG结构中加入另一个反馈环路来改善线性度,即双交叉耦合共栅(DCCG)结构,如图4所示。图5给出了双反馈环路的框图,其中A为开环放大器;f为反馈系数;Si为输入信号;So为输出信号;Se为Si与(f1So+f2So)之间的差值。

图4 提出的双交叉耦合共栅放大器的电路图

图5 双反馈系统原理框图

由图5可得输出信号So可表示为:

(6a)

其中:

Se=Si-f1So-f2So

(6b)

该双反馈系统具有如下的输入输出关系表达式:

(7a)

其中:

(7b)

(7c)

(7d)

式中,b1dual、b2dual和b3dual分别为闭环线性增益、二阶非线性系数以及三阶非线性系数,Tx为相应环路的反馈环路增益。

由式(1)、式(7b)和式(7d)可得,双反馈系统的三阶互调失真截止点AIP3dual如下所示:

(8)

由式(1)和式(8)可见,双反馈系统的环路增益为两个反馈系统环路增益之和,因而,DCCG结构可以通过增加总体环路增益的方式提高线性度,远优于CCCG结构。

图6给出了DCCG结构的等效半边电路,以用于计算反馈电路相关参数,DCCG结构的反馈电路相关参数如下所示:

(9a)

(9b)

(9c)

(9d)

(9e)

式中,b1DCCG为DCCG结构闭环增益;a1CCCG和a3CCCG分别为开环增益的一阶系数、三阶系数;TCCCG为环路增益;FCCCG为反馈系数;Cf为晶体管漏源间反馈电容。如果输入源阻抗Rs远小于1/jωCf,由式(9)可推得DCCG拓扑结构的三阶互调失真截止点AIP3DCCG可简化为:

AIP3DCCG≈

(10)

由式(5)和式(10)可见,由于DCCG结构将环路增益增高到(1+2jωCfZload)/ (1+jωCfZload)倍,因而将AIP3提高到[(1+2jωCfZload)/ (1+jωCfZload)]3/2倍,进一步改善了电路线性度。

图6 提出的DCCG放大器的等效半边电路

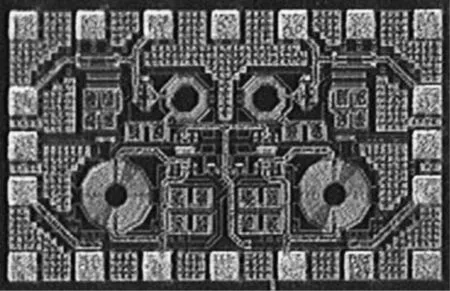

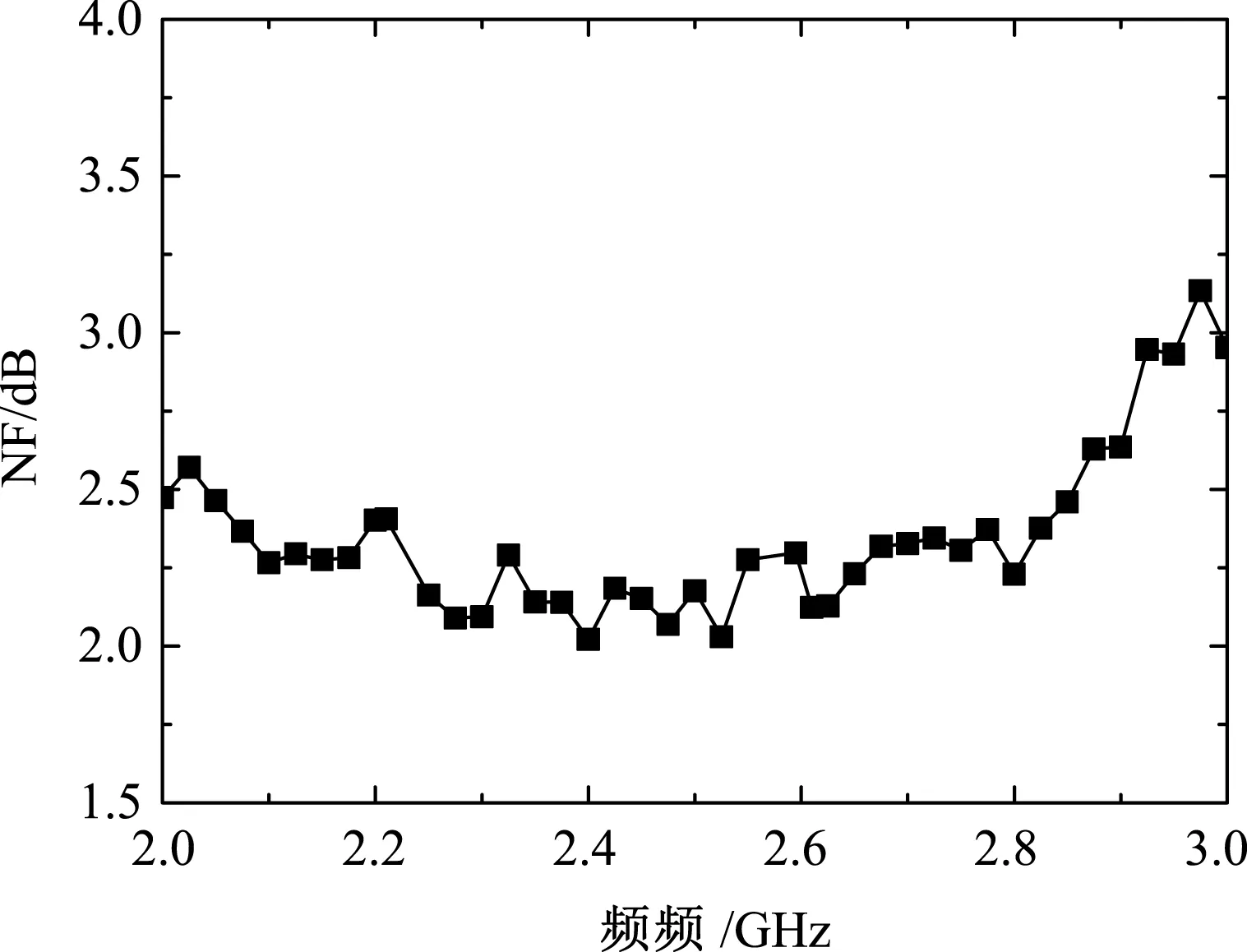

2 芯片实现与测试结果

基于SMIC 0.18 μm CMOS工艺,对本文所提出的LNA进行流片实现并测试验证。图7所示即为该LNA的芯片照片,电路核心大小为1.03 mm2,图8给出了增益S21、输入匹配参数S11和输出匹配参数S22的测试结果,在2.4 GHz工作频率下的增益为18 dB,输入输出匹配参数均低于-10 dB。图9给出了噪声系数NF的测试结果,在2.4 GHz频率下,NF为2.02 dB。图10所示为输入三阶截止点IIP3的测试结果,在2.4 GHz频率下,IIP3高达8.3 dBm,实现了较高的线性度,并且该芯片在1.1 V电压供电下功耗仅为2.5 mW。综合性能指标优于以往文献所报道的测试结果[9,12],文献[9]和[12]所设计电路取得的IIP3分别为-7.5 dBm和-0.5 dBm,与本文的8.3 dBm的高线性度相比相差甚远,LNA位于系统接收机的最前级,需要一个较高的线性度接收来自天线的射频信号,本文所设计的8.3 dBm的高线性度完全满足此需要,另外文献[9]和[12]所报道电路的噪声系数分别为6 dB和2.7 dB,也略逊于本文所取得的2.02 dB的低噪声系数,位于系统接收机最前端的LNA直接决定了整个接收机的噪声性能,因此LNA的噪声系数越小越好。

图7 LNA的芯片照片

图8 S21、S11和S22的测试结果

图9 噪声系数NF的测试结果

图10 输入三阶截止点IIP3的测试结果

3 结 语

本文提出的LNA在CCCG结构中采用基于电容反馈的双反馈环路,以在不影响其他性能的前提下,改善电路的线性度。CCCG结构不仅增强了基波频率的跨导,改善了增益和噪声性能,而且通过反馈方式抑制了二次谐波信号,改善了线性度,在此基础上引入DCCG结构,在晶体管源漏间引入电容反馈,进一步提高电路的线性度。

基于SMIC 0.18 μm CMOS工艺,对本文所提出的LNA进行流片实现并测试验证。测试频率为2.4 GHz,测试结果表明该LNA在较低功耗下实现了较优的性能,在仅消耗2.5 mW功耗的前提下,取得了18 dB的增益,2.02 dB的噪声系数,8.3 dBm的输入三阶截止点IIP3,同时输入输出匹配良好,综合性能指标达到国内外先进行列。