基于DDS+PLL混合频率合成技术及噪声分析

2018-07-19汪海燕

汪海燕

频率合成技术是雷达信号源中的关键技术之一,频率合成的主要方法:直接频率合成、数字直接频率合成(DDS)以及锁相频率合成(PLL).其中,DDS合成技术优点明显:分辨率高、转换时间快、输出相位噪声低.缺点也很明显:输出频率低、杂散性能较差,会对它的应用产生较大影响.PLL锁相频率合成,优点在于频谱质量好、锁定频率高、带宽宽等,不足之处有:置频时间长、分辨率较低等.因此,理论上阐述,可以把DDS与PLL综合在一起,取长补短,优势互补[1-2],那么频率合成可以在分辨率、相位噪声、信号建立时间、输出频率等方面有所突破,取得满意效果,非常有前景.相位噪声是衡量频率合成器短期频率稳定度的一个至关重要的参数,分析相噪及其影响因素,对合成器性能改善具有积极意义.

1 DDS+PLL组合系统

1.1 DDS直接数字频率合成技术

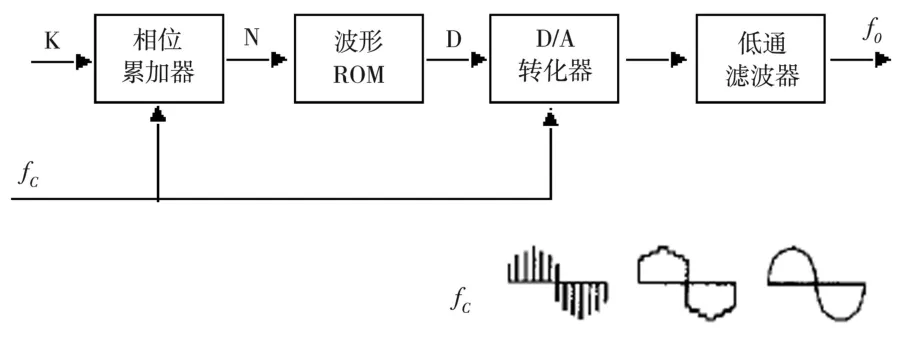

DDS直接数字式频率合成器基本原理框图如下图所示.由相位累加器、ROM、D/A和低通滤波器以及参考时钟构成.对每一个时钟脉冲,频率控制字决定相应相码,寻址ROM,得到不同幅度编码,送入D/A输出相应阶梯波,最终经低通滤波输出所需频率信号[3].即

图1DDS原理图

用DDS+PLL组成混合频率合成器,有三种设计方法,下面分别阐述之.

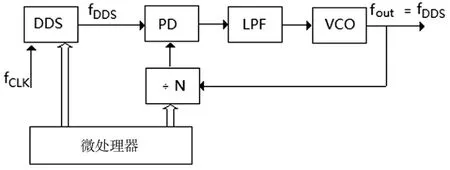

1.2 DDS激励PLL的频率合成器

该方案用DDS直接数字频率合成器输出端信号,作为PLL倍频的输入信号,原理如图2所示.

图2 DDS激励PLL的频率合成器

此种设计方法的优势就是,从理论互补角度考虑,利用鉴相频率高,增加PLL的转变速度,同时因为DDS的高频率分辨率,从而使得PLL输出分辨率不会降低.另外PLL带通滤波能够对DDS的带外杂散达到一定改善效果.从硬件角度考虑,此设计方法电路构架简洁,成本不高,控制简单.因为PLL用于倍频,则DDS输出信号中,不论杂散部分,还是相位噪声部分,都会出现成倍增加.因此N一般设定较小,比如取N<10,来达到系统的噪声性能的要求[4].

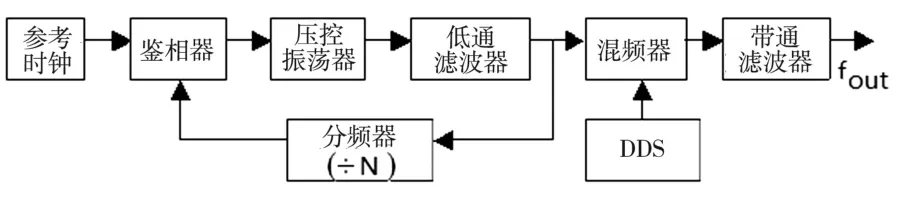

1.3 环外混频式频率合成器

原理框架图如图3所示,此设计方法是把PLL输出与DDS输出混频后,经过滤波最终输出频率信号.

图3 环外混频式频率合成器

信号频率:

此设计方法中,DDS频率分辨率高、跳变快,而且PLL能够确保系统的工作频率和带宽.另外需要考虑带宽频率,使满足:BWDDS≥fCLK.此系统设计中,转换频率在BWDDS范围内,转换时间通过DDS得到.反之,超出BWDDS范围,则由PLL得到,所以在此设计方法中可以达到频率转换时间短、鉴相频率高的效果,PLL与DDS输出信号

的相位噪声控制得较理想.

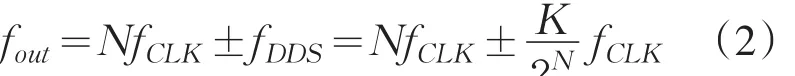

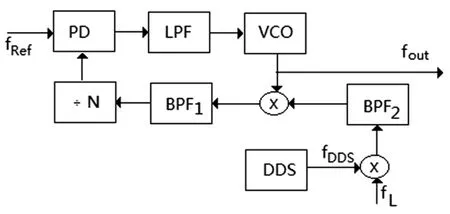

1.4 PLL内插DDS的频率合成器

此种设计方案如图4所示,输出频率:fout=NfRef+fDDS,且fRef≤BWDDS.

在此设计中,因DDS频率分辨率高,因而PLL能够提升鉴相频率fRef,加快PLL的频率转换时间.由于DDS的输出频率与PLL倍频直接混频,因此此设计相位噪声优良.设计中将本振fL与DDS混频,提高DDS输出频率,也达到减小BPF2的设计难度的目的.同时因为增加了混频环节,那么额外提升了硬件复杂度,同时由于寄生分量的存在也增加了调试结果的不确定性.

图4 PLL内插DDS的频率合成器

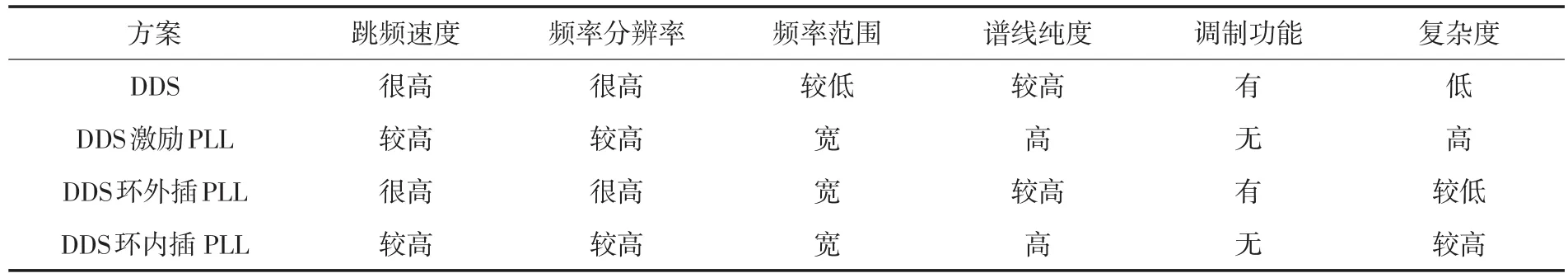

最后,表1给出了直接数字频率合成技术及混合频率合成技术的性能比较.不同频率合成器在性能方面各有特色,在实际设计使用中,应用于不同具体情况[5].

2 锁相环相位噪声分析

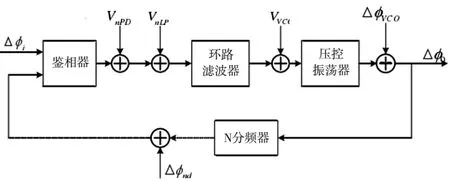

典型锁相环路相位模型如图5所示.

图5 锁相环相位噪声模型

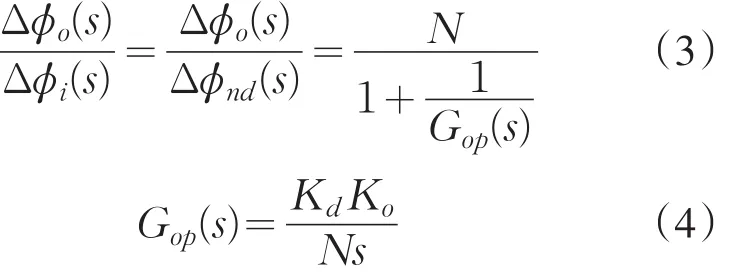

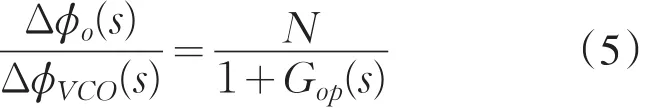

Δϕi(s)和Δϕnd(s),都受到鉴相器的输入相位噪声影响,因此,两者与输出相位噪声Δϕo(s)之比具有相同的传输函数:

表1 各频率合成器的性能比较

其中Gop(s)环路开环增益,Kd为鉴相器的增益,Ko为VCO的增益.

因此,在确保Δϕi(s)、Δϕnd(s)小于VCO噪声的前提下,环路带宽最大.同时尽量提高参考频率 fREF,以达到降低分频次数的目的.

VC O的相位噪声如下:

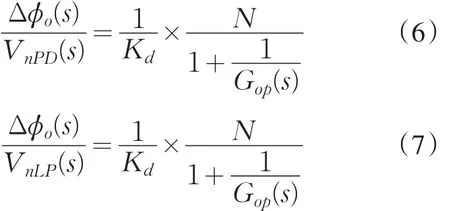

鉴相器和环路滤波器的噪声电压,在鉴相器之后的噪声电压VnPD(S)与VnLP(S)同时降低至1/Kd,因此两者对输出Δϕo(s)之比传输函数有以下表达式:

除了上述要求,使其在输出端的影响有限,还要确保鉴相增益Kd尽量大,这与对1/Gop(s)的要求有悖.考虑到系统中参数相互影响、关联,当遇到实际具体情况时,综合考虑系统参数,总体分析给出折衷方案[6].

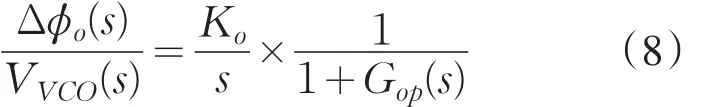

VCO噪声电压VVCO(s)在VCO的输入端和带宽给定前提下,VVCO(s)正比于Ko,传输函数:

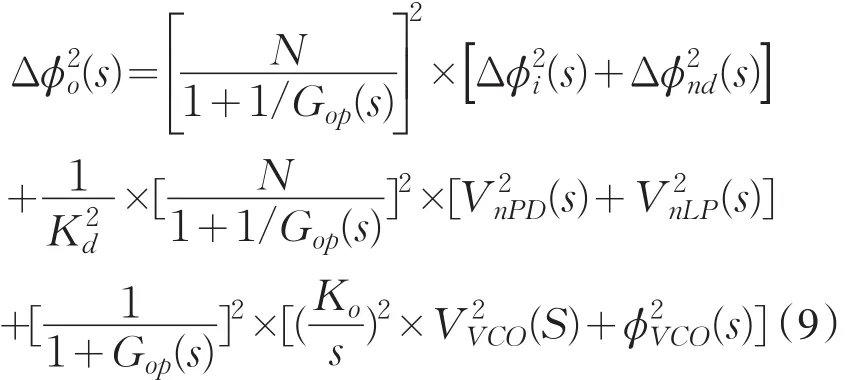

在阐述完不同噪声的影响下,总输出噪声即

式(9)考虑了各个噪声源的影响,其中主体影响因素有:鉴相器的输入噪声,鉴相增益Kd,VCO噪声和增益Ko[6].

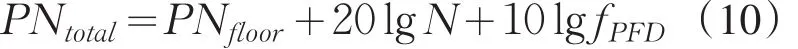

综上,锁相环系统中对输出频率的制约因素涉及很多,估算带内总相位噪声表达式如下.

其中PNtotal为总相位噪声,PNfloor为相位噪声基底,由电路本身参数所决定,锁相环和参考频率不变的情况,其为常数.其余两项分别与反馈分频比和鉴相频率有关.

3 结束语

本文介绍了DDS+PLL混合频率合成技术的特点,给出三种混合频率合成器的组合方案,并与直接数字频率合成技术(DDS)等一并进行特点比较,指出其不同适用场合.对PLL相位噪声进行分析得出以下结果:

(1)增大环路带宽提高参考频率 fREF,以达到降低分频次数.

(2)环路总输出噪声,影响因素很多,但主要影响因素有:鉴相器的输入噪声,鉴相增益Kd,VCO噪声和增益Ko.

(3)估算锁相环系统的带内总相位噪声表达式:PNtotal=PNfloor+20lgN+10lgfPFD.