一种选择单粒子瞬态脉冲敏感结点的方法

2018-06-22宋依青严佳倩

宋依青,严佳倩

(常州工学院计算机信息工程学院,江苏 常州 213032)

0 引言

随着电子工艺尺寸的逐步缩小,产生单粒子瞬态(single event transient,SET)脉冲错误所需的电荷量减小。当前,电路的操作频率也愈来愈高。由于这些因素,组合逻辑电路的软错误率(soft error rate,SER)可能超过单粒子翻转(single event upset, SEU)错误[1-3]。由于组合逻辑电路具有不规则性,因此提高该类电路抗SET错误的性能存在较大困难。大多数方法只针对其中一个因素来降低整体电路的软错误率。例如,最常见的三模冗余(triple modular redundancy, TMR)加固技术通过逻辑掩蔽消除SET脉冲。另外,有些方法选择性地加固电路中的某些路径以实现逻辑掩蔽[4-6],但可能严重削弱电路性能。这些方法在功耗和面积上的开销很大。因此,亟待开发既能有效加固组合逻辑电路又能减小开销的技术。

由于集成电路中有上百万个门,面积和功耗是组合逻辑电路的重要设计参数,因此设计出对面积和功耗都敏感的加固方法很重要。本文提出一种新的加固组合逻辑电路的方法,该方法关注三个影响软错误率的因素中的两个:电气屏蔽(electrical masking)和锁窗掩蔽(latching-window masking)。

最敏感的结点可以通过一种模式独立的概率论方法来确定。通过改变这些敏感结点的晶体管尺寸,受撞击结点发生SET时的脉宽会减小,从而实现加固敏感结点的目的。我们提出的这种方法在电路面积和功耗上的开销远比之前的大多数方案小得多。

1 结点加固

先前的方法多针对一个结点或者一段电路进行加固,通过增大结点电容实现。对于一个电容为C的结点,晶体管输出端储存的电荷是电容C和该结点电压Udd的乘积。当被撞击的结点积聚了比输出端更多的电荷时,电路中会产生一个轨对轨瞬态脉冲(rail-to-rail transient pulse)。如果该结点电容值增大(主要通过增大下一个门的输入电容),产生一个SET脉冲所需的电荷也会增加,从而达到加固电路结点的目的[7]。在以前的制备工艺中一个结点储存的电荷值远高于沉积电荷,因此这种方法对于以前的制备工艺奏效,但对于先进集成电路工艺而言,这种加固方法并不奏效。

对组合逻辑电路而言,受撞击结点总是会回到产生SET时的初始结点电压。通常来说,与一个结点相连的截止晶体管(off-transistor)被高能粒子撞击后会积聚电荷,而与该结点连接的导通晶体管(on-transistor)会移除积聚的电荷。如果是截止的NMOS管的敏感漏极(drain)被撞击,则称作n-hit;如果是截止的PMOS管的敏感漏极被撞击,则称作p-hit。对于CMOS技术而言,如果受撞击晶体管是NMOS管,那么恢复晶体管就是PMOS管。SET脉宽是由沉积电荷数和恢复晶体管的驱动能力所决定的。沉积电荷数通常是一个由工艺等综合技术决定的参数,设计者几乎不能改变(除非改变双极晶体管大小)。综上,恢复晶体管尺寸是唯一可控的影响SET脉宽的参数。图1展示了SET脉宽与储存的电荷和恢复晶体管尺寸的关系。显然,增大晶体管尺寸能很大程度地减小SET脉宽。

本文中所提出的方法能分辨出最敏感的或者最易受到单粒子效应影响(同时考虑产生和传播等因素)的结点,并且仅通过增大恢复晶体管尺寸来加固它们。以前的方法只是通过观察逻辑掩蔽效应来辨认最敏感的结点。一个结点如果存在多输入矢量(input vector)且与输出间存在逻辑路径,则该结点被认为是敏感结点。但是,我们必须考虑到截止晶体管受高能粒子撞击(这是产生SET的原因)的可能性。本文所提出的方法已将上述决定结点敏感度的因素全部考虑在内。将结点根据敏感度排序,设计者就可以选择需要加固的结点来最大程度地减小软错误率。

图1 SET脉宽与储存的电荷和恢复晶体管尺寸的关系

2 结点敏感度评估

2.1 选择电路中敏感结点的原则

给定一个电路,对于大部分的输入向量而言,门的状态都是高电平或者低电平。如果门的输出是高电平,考虑到输入的可能性,那么由n-hit产生SET的概率比p-hit大得多。反之亦然。另外,n-hit或者p-hit引起的SET脉宽与受击结点的恢复晶体管的驱动电流成反比。假设其他参数不变,恢复电流增大也会导致电气屏蔽或者锁窗掩蔽的概率减小,而且电路的开销较小。因此,主要目标是筛选出那些能产生SET且最有可能传递到输出端的结点。

2.2 结点的加固优先级算法

信号为逻辑1(0)的概率在本文中被定义为Phigh(Plow)。Phigh(Plow)可以作为结点概率值来提供关于逻辑掩蔽的信息。如果门输入信号的概率Phigh大于0.5,则该门输出“1”的概率大于输出“0”的概率。Phigh值相对较大的门输出会更有可能因为n-hit产生SET。假设由这些门输出的瞬态有更大的可能性传播到电路的输出端,那么这些门就被认为是敏感的结点,并作为加固的目标。对于这些结点,因为p-hit发生的可能性相对较小,所以NMOS管不需要加固。而n-hit导致的SET脉宽与上拉PMOS管的恢复电流驱动直接相关,PMOS管尺寸增大会导致这些结点的SET脉宽减小。相反,Phigh值比较小的结点更有可能因为p-hit产生SET,增大NMOS管的电流驱动能减小SET脉宽。

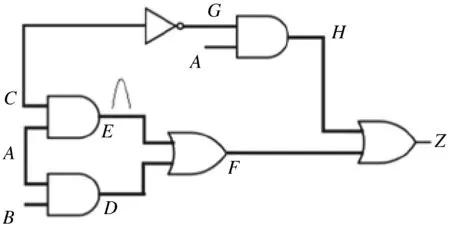

下面使用图2所示电路进行理论计算。

图2 用于计算结点信号概率的参考电路

结点信号概率的计算在参考文献[8—9]中已有表述。假设系统的输入是不相关的,如果P1和P2(代表Phigh)是一个与门的输入信号概率,则该与门输出信号为逻辑1的概率是P1·P2。如果是或门,那么输出信号为逻辑1的概率就是P1+P2-P1·P2。对于一个反相器,输出信号为逻辑0的概率是1-P1。综合考虑信号相关(signal correlations)和扇出重汇聚(reconvergent fan-outs)影响[10],重复的乘积项只算一次。即在一个逻辑门可能产生的方程中,如果项P1在乘积中重复,那么只算一次。例如P1·P1=P1。另外,Phigh+Plow=1,并且反相信号的概率乘积是0。例如,P1(1-P1)=0。

对图2所示电路,结点F的Phigh值为

P(F)=P(A·B)+P(A·C)-

P(A·B)P(A·C)

(1)

因为输入之间互不相关,

P(A·B)=P(A)·P(B)

(2)

并且

P(A·C)=P(A)·P(C)

(3)

不重复计算(1)中第三项的P(A),我们得到

P(F)=P(A)P(B)+P(A)P(C)-

P(A)P(B)P(C)

(4)

对于结点Z,

P(Z)=P(A·C′)+P(F)-P(A·C′)P(F)=

P(A)P(C′)+P(A)P(B)+

P(A)P(C)-P(A)P(B)P(C)-

P(A)P(B)P(C′)

(5)

以上算法中,C与C′反相。

每个结点的Phigh值见表1。

表1 各结点的逻辑掩蔽指数及加固指数

尽管电路会产生SET脉冲,但该脉冲未必传播到电路的输出结点。对某一结点而言,如果因为强的逻辑屏蔽效应导致该脉冲不能到达电路的输出端,加固该结点并不会显著降低单粒子软错误率。那些最有可能产生SET并传播至电路输出端的结点应当作为电路高效加固的对象。对于电路中一组给定的输入,每个结点的Phigh值可以用来计算该点的瞬态传播到电路输出端的概率。一个信号从门的输出端传播到电路输出端的概率定义为逻辑掩蔽指数(logic masking metric,LMM)。

(6)

式中,Pk是第j门的输入使能ek的概率,LMM不取决于该门输入到输出的路径。一个给定输入产生的瞬态能传播到电路输出端,取决于输入(使能)值。对于与门、与非门和同或门来说,这个(使能)值是1。对于或门、或非门和异或门来说,这个值是0。假设图2电路中结点E有个瞬态要传播到输出端Z,则E的逻辑掩蔽指数

LMM(E)=(1-P(D))(1-P(H))

(7)

图2中每个结点的LMM值列在表1中。对于那些从门输出端到电路输出端有多条路径的大电路而言,本文仅考虑掩蔽可能性最小的那条路径。

筛选出最有可能产生瞬态脉冲的门后,还需要考虑信号传播概率,并将其做比较。这可以通过将LMM和Phigh相乘来完成,对Plow值也做同样的操作。对于一个给定的结点来说,LMM值对n-hit和p-hit都是相同的。因此,加固指数HM(hardening metric)指出了那些比其他门更有可能产生某种瞬态并有最高传播概率的门。

(8)

对于门的加固指数,把它们按降序排列依次考虑加固。应当指出,把晶体管尺寸加大会增大击中的概率,但是对于一个给定结点来说,一个高的HM值表示恢复晶体管处于截止状态的概率较低。因此,对于恢复晶体管来说,敏感区域的任何增大对整体错误率的影响微乎其微。

3 仿真结果

基于上面的分析,我们对ISCAS基准电路[10]的信号概率通过PERL脚本计算得出,并使用电路的VREILOG语言进行仿真。

ISCAS基准电路是使用了某 45-nm PDK综合得出的,增加的面积和功耗是使用Synopsis Design compiler计算出来的。

对大多数逻辑电路,我们都可以假设输入信号互不相关且输入为高电平的概率为0.5(即Phigh=0.5)。当然,如果设计者需要根据给定电路采用其他合理的概率值,那么也可以通过模拟输入负载来实现。对于ISCAS电路,结点数按Phigh分配在表2中给出。

表2给出了电路中的结点总数和处于Phigh的各个等级的结点数。显然,只有一小部分的门处于高电平或者低电平(即接近1或0的值)。对于每个电路,HM值排名前10%、20%、30%的结点通过增大恢复晶体管尺寸至原来2倍来加固。如图1所示,一个尺寸放大2倍的恢复晶体管会使SET脉宽平均减小55%。因为电路SER与SET脉宽的锁存概率直接相关,所以加固最敏感的结点会大幅减小SER。表3比较了为达到改进效果需要增加的面积和功耗开销。图3给出了算法伪代码。

表2 不同基准电路结点信号概率分布

表3 加固不同基准电路需要增加的面积和功耗 %

图3 算法伪代码

4 结论

某些结点受到n-hit或者p-hit的影响产生单粒子瞬态脉冲,并且有较大可能将瞬态传播到电路输出端。综合考虑这些结点的信号传播概率和逻辑掩蔽概率,提出一种高效的结点选择算法,以实现电路的选择性加固。因为电路SER很大程度上依赖于结点瞬态的产生和传播概率,加固这些结点能有效减小电路SER。ISCAS基准电路的仿真结果表示,当加固30%的结点时,需要增加的面积为12%~27%,增加的功耗在8%至14%之间。因此,该技术对于加固面积、功耗和延时约束较大的电路是非常有效的。

[参考文献]

[1]DODD P E,SHANEYFELT M R,SCHWANK J R,et al.Cur-rent and future challenges in radiation effects on CMOS electro-nics[J].IEEE Transactions on Nuclear Science,2010,57(4):1747-1763

[2]NAKAGAWA S,TAGUCHI M,KIMURA A et al.Let and dose rate effect on radiation-induced copolymerization in physical gel[J].Nuclear Instruments and Methods in Physics Research Section B:Beam Interactions with Materials and Atoms,2014(334):64-68.

[3]CHEN Rongmei,MAHATME N N,DIGGINS Zachary,et al.Impact of temporal masking of flip-flop upsets on soft error rates of sequential circuits[J].IEEE Transactions on Nuclear Science,2017,61(4):1902-1908.

[4]AVAINEN A,FERLET-CAVROIS V,BOSSER A,et al.SEGR in SiO2-Si3N4stacks[J].European Conference on Radiation and Its Effects on Components and Systems,2014,61(4):1-5.

[5]VAZQUEZ-LUQE A,MARIN J,TERRON J A,et al.Neutron induced single event upset dependence on bias voltage for CMOS SRAM with BPSG[J].IEEE Transactions on Nuclear Science,2013,60(6):4692-4696.

[6]HUANG PengCheng,CHEN ShuMing,CHEN JianJun,et al.Novel N-hit single event transient mitigation technique via open guard transistor in 65 nm bulk CMOS process[J].Science China Technological Sciences,2013,56(2):271-279.

[7]KELLY A T,ALLES M L,BALL D R,et al.Mitigation of single-event charge sharing in a commercial FPGA architecture[J].IEEE Transactions on Nuclear Science,2014,61(4):1635-1642.

[8]CHEN C H,KNAG P,ZHANG Z.Characterization of heavy-ion-induced single-event effects in 65 nm bulk CMOS ASIC test chips[J].IEEE Transactions on Nuclear Science,2014,61(5):2694-2701.

[9]QIN J,CHEN S,LIANG B,et al.Voltage dependency of propagating singleevent transient pulsewidths in 90-nm CMOS technology[J].IEEE Transactions on Device and Materials Reliabi-lity,2014,14(1):139-145.

[10]HANSEN M C,YALCIN H,HAYES J P.Unveiling the ISCAS-85 benchmarks:a case study in reverse engineering[J].IEEE Design and Test of Computers,1999,16(3):72-80.