电路级模拟技术在SRAM型FPGA总剂量效应敏感性预测中的应用

2018-05-30郭红霞丁李利范如玉姚志斌罗尹虹张凤祁张科营

郭红霞, 丁李利, 范如玉, 姚志斌,罗尹虹, 张凤祁, 张科营, 赵 雯

(西北核技术研究所, 西安 710024; 强脉冲辐射环境与效应国家重点实验室, 西安 710024)

任何一个复杂系统总是由相对简单的子系统组成的,全系统的功能是由这些子系统的功能来保证的,子系统的功能又是由组成子系统的单元器件的性能来实现的[1]。各个子系统的电离辐射响应范围不一样,导致整个系统受限于最薄弱单元电路的失效水平,本文通过数值模拟和试验,分析研究了不同敏感单元电路的偏置及工作模式,预测了整个电子系统的抗电离辐射效应能力。

FPGA具有可靠性高、灵活性好、研制周期短等独特的技术优势,广泛地应用在卫星系统中。同时,由于FPGA内部资源丰富、结构复杂、造价昂贵,单纯通过实验室模拟手段难以全面评估其抗辐射性能。FPGA的抗辐射性能预测技术已成为器件生产厂家与应用单位急需解决的关键技术。预测技术是通过一种方法和数值模拟软件,依据FPGA的材料与结构工艺参数及辐射效应原理和损伤规律,根据少量的样本试验,以较高的科学置信度给出在已知辐射环境中FPGA的抗辐射能力。将一个FPGA芯片分解成若干个功能块,每个功能块又分解成若干个基本单元。研究这些基本单元的抗辐射性能和它们在整个电路中的作用,是预测技术研究的基础。

针对总剂量效应,应用线性系统在辐照环境中性能裕度变窄的概念开展工作。首先对FPGA进行全面测试,找出最可能的失效模式,检测出易损功能模块;然后从FPGA中分离出该功能模块进行隔离测试与分析,基于一定样本量的单管总剂量试验,对器件的损伤过程建立物理模型进行准确描述[2-3];最后在已知模块电路工作过程中各个子模块相互关系的基础上,自下而上分析电路功能随累积吸收剂量的变化[4]。

通过研究,可以为器件的用户方提供在一定辐射环境下的FPGA器件抗辐射能力阈值、裕量和不确定度。同时,通过模拟实验和数值模拟相结合的手段,给器件研制方提供辐射损伤的薄弱环节以及敏感单元和路径,提出加固措施,改善器件的抗辐射能力。研究工作的开展将对大规模集成电路抗辐射加固能力评估有很好的推动作用。

1 SRAM型FPGA总剂量效应实验研究

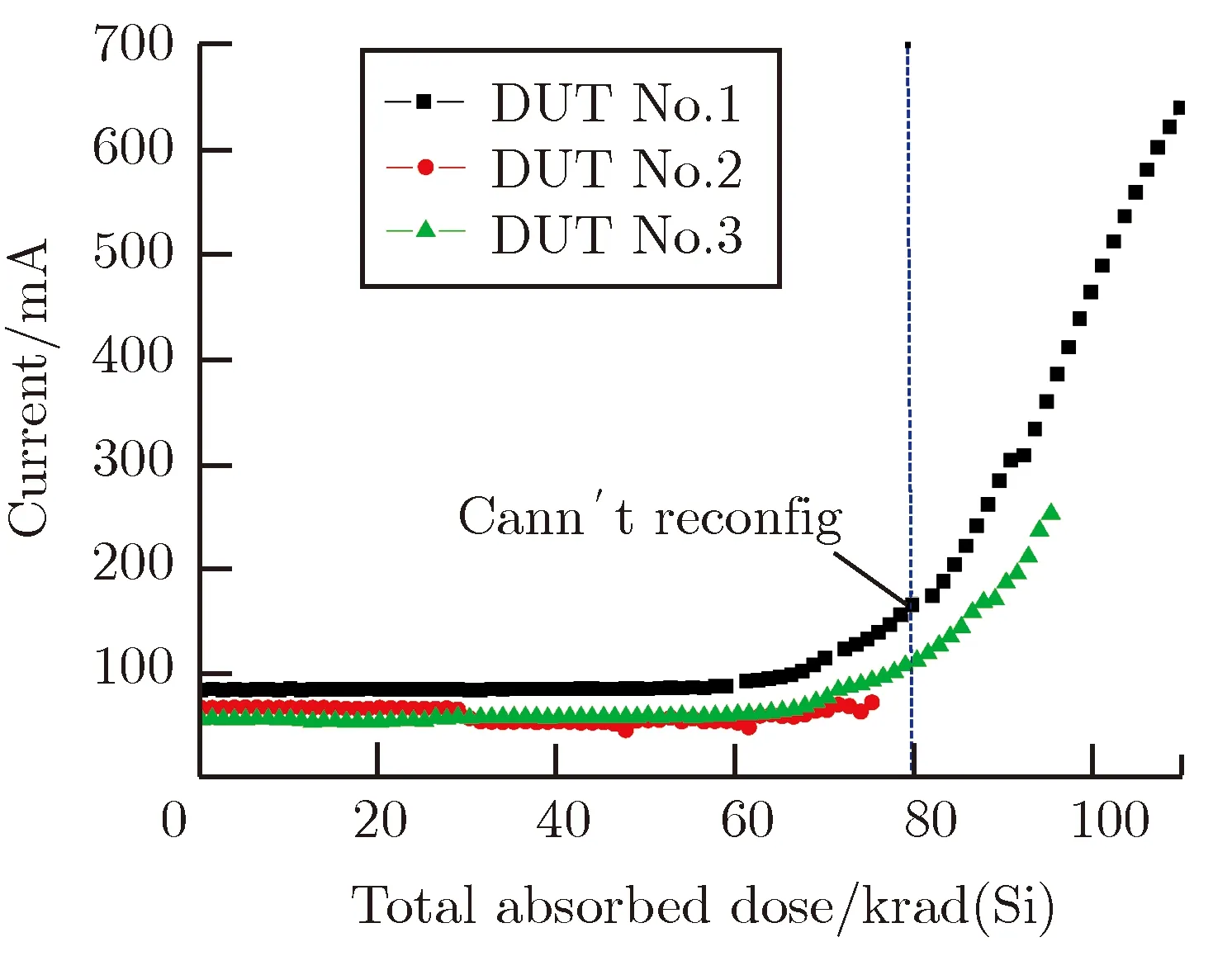

对特征工艺尺寸为0.25 μm的30万门SRAM型国产FPGA开展了总剂量试验。辐照过程中,实时采集器件内核及I/O端口的电源电流。辐照到5×104rad(Si)后,每隔一定吸收剂量对器件进行重新写入,验证器件是否能正常配置,如图1所示,配置失效的阈值<1×105rad(Si),约为7×104~8×104rad(Si)[5]。

(a) Current of core power supply

(b) Current of I/O power supply 图1 FPGA电源电流随吸收总剂量的变化情况Fig.1 Operating current of FPGA vs. total absorbed dose

器件在累积吸收剂量不断增加的辐射环境中工作时,随着工作时间的增加,器件受到的吸收剂量水平不断增加,辐射损伤就逐渐地显现出来,导致器件性能的特征参数改变,从而改变了器件乃至系统电路的工作状态。当这种改变超过了允许的范围时,器件或系统电路就无法正常工作,这体现为自下而上的制约关系。

该部分工作也可以描述为建立连接辐射环境下器件敏感参数变化与电路功能退化之间的性能通道。即首先构建引入吸收剂量与偏置条件的单管器件总剂量效应损伤模型,接下来代入待分析电路的网表中进行电路分析计算,通过电路仿真研究各个子电路模块对总剂量效应的响应情况,最后利用仿真的结果就可以判定各个子模块的总剂量效应敏感性,解析得到易损功能模块的损伤机制。

通过分析全芯片总剂量辐照测试的结果与现象,可得到SRAM型FPGA最可能的失效模式及最敏感模块电路。从实测结果可以看出,FPGA在总剂量效应作用下最易出现的失效表征是不能重新配置和无法完成上电初始化操作,而在上述功能失效发生时, FPGA中配置存储器的数据存储、读出和编程所实现配置电路的输出功能却均保持正常。因此,FPGA上电启动和配置过程的相关操作与所涉及电路是待分析的重点[6]。

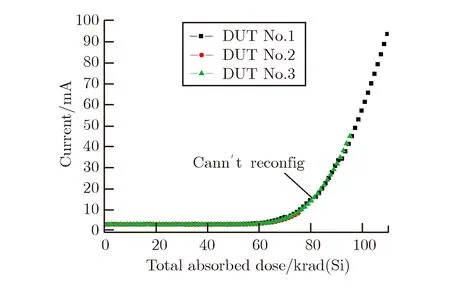

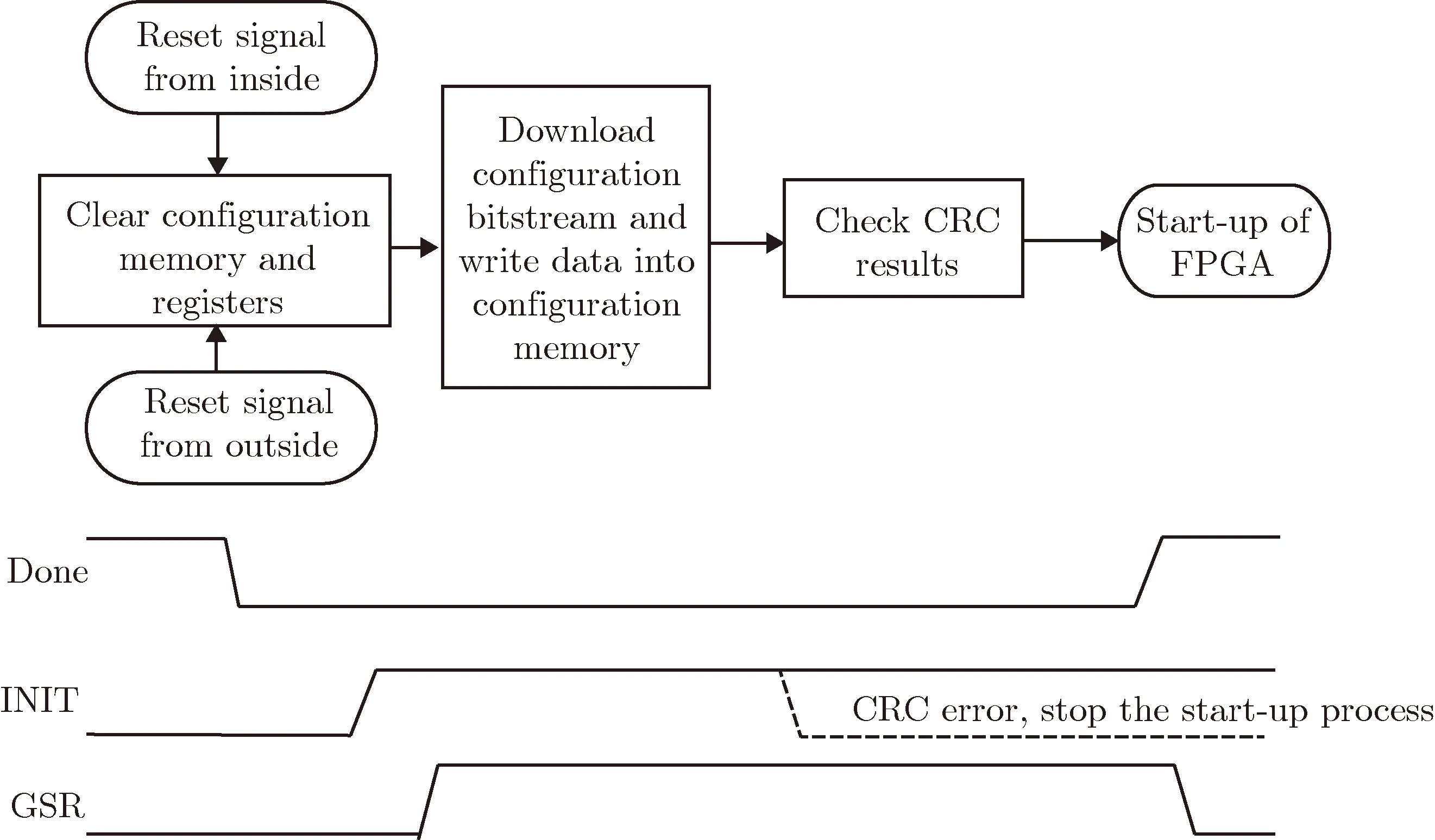

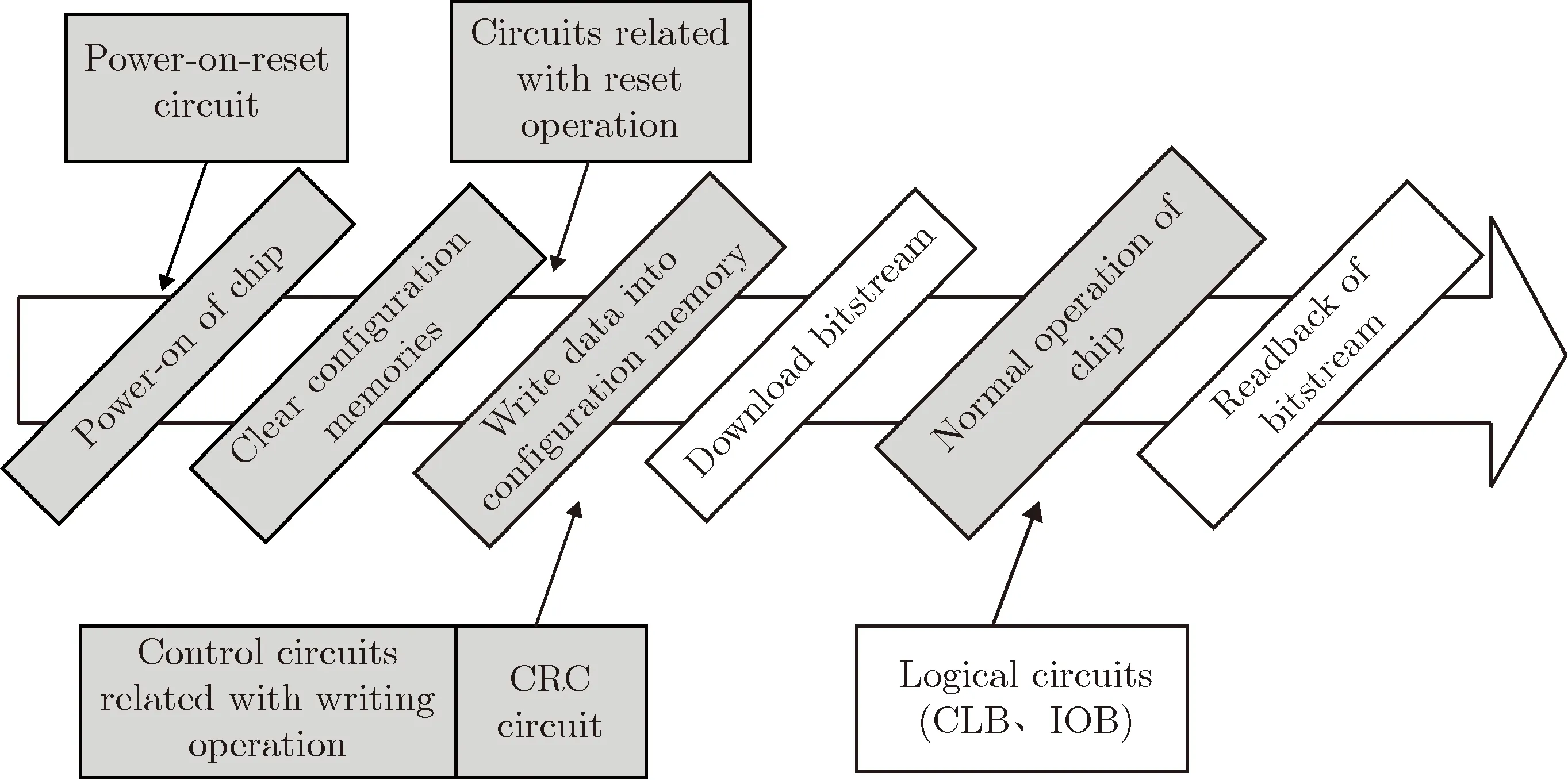

图2所示为待研究国产FPGA的上电启动和配置流程图。可以将整个流程划分为4部分:1)上电复位或外部提供复位信号,清空配置存储器和全局寄存器;2)下载码流并写入各配置存储器,完成编程过程;3)判断CRC校验结果是否正常;4)启动FPGA。各部分操作的正确与否可以通过查看状态信号的变化加以判定,状态信号包括INIT、GSR和Done信号。INIT信号在过程1)结束时被置高,而在过程3)出错的情况下被重新置低;GSR为内部触发器的全局复位信号,在整个过程2)被执行时有效;Done信号用于表征整个重新配置过程的完成。总之,INIT信号出错说明清空配置存储器、全局寄存器的操作失败或者CRC校验出现错误,INIT信号正常而Done信号出错则说明对内部触发器进行全局复位时出现错误。

总之,FPGA不能重新配置的失效原因可以确定为对配置存储器与全局寄存器进行复位时出现错误,对内部触发器进行复位时出现错误或CRC校验出现错误。与此相关的电路包括上电复位电路、全局寄存器复位操作相关电路、内部触发器复位操作相关电路、CRC计算电路及CRC寄存器等。

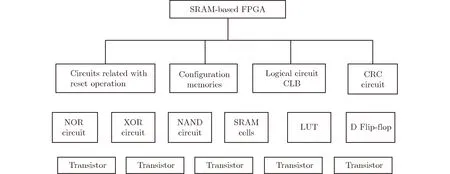

根据全局芯片的总剂量辐照实验已经筛选出了最可能失效的模块电路,如图3中用深色标注所示。下文将着重分析这些相关电路的正常工作表征和基本组成。

全局复位操作相关电路的正常工作表征是能够产生上电复位信号,且对应的瞬时电流脉冲低于限值。其底层子电路包括POR上电复位电路、全局寄存器和配置存储器。CRC校验电路的正常工作表征是校验最终结果全为 “0”,其底层子电路包括异或门、D触发器、或非门和与非门等。逻辑单元电路CLB的正常工作表征是能够实现运算并按照正常时序写入输出存储值,其底层子电路包括LUT、D触发器和传输管。配置存储器读写电路的正常工作表征是能够向特定地址SRAM单元写入“0”、“1”值,并能够从特定地址SRAM单元中读取之前写入的值,其底层子电路包含SRAM单元、译码器所需逻辑门、灵敏放大器和数据端输入输出转换等。

最终得到的芯片系统层次划分结果如图4所示,共分为4个层次,模块电路与组成模块电路的子电路将是进一步分层计算评价时的重点研究对象。

图2 SRAM型FPGA的上电启动和配置流程图Fig.2 Startup and configration of SRAM-based FPGA

图3 SRAM型FPGA的工作流程及相关模块电路Fig.3 Working procedure and related block circuits of SRAM-based FPGA

图4 结合全局总剂量辐照实验前期简化后得到的芯片系统层次划分结果Fig.4 Simplified hierarchical results of the chip system regarding to the early experiment of total dose irradiation

2 总剂量器件模型的构建

在生产了与FPGA相同工艺、具有不同宽长比的一定样本量的nMOS与pMOS管的基础之上,开展总剂量实验并详细测试特性曲线的变化。测试方案必须涵盖器件模型的提取所要求的各种偏置条件,即在MOS晶体管的栅极、漏极、源极与衬底接触间添加的是扫描式覆盖型偏压,这与常规总剂量实验不同,大大增加了测试的复杂性。单管实验得到的数据将用于构建总剂量辐射效应模型。

器件尺寸减小后,简单地调整阈值电压并不能表征单管的总剂量效应,厚的场氧隔离层(STI)俘获过剩载流子产生的氧化层陷阱电荷和界面态陷阱后,引发明显的漏电流增大现象,关断电流大大增加,甚至可从原来的1×10-10A增加至1×10-5A。

图5为Vds=0.1 V时,不同吸收剂量下的Ids-Vgs特性曲线的变化情况。

图5 不同吸收剂量下的Ids-Vgs特性曲线Fig.5 Evolution of Ids-Vgs characteristics at various absorbed doses

可以看出,吸收剂量累积一定值后,器件的电学特性已经不再符合单个晶体管特性,nMOS管的泄漏电流值明显增大[5]。所以,单纯地修改阈值电压并不能反映总剂量引入的影响。根据仿真结果,参考相关文献资料,该部分采取在晶体管主电流通道上并联一个随偏置情况不同而变化的电流源,实现对泄漏电流的描述[6-7],而阈值电压和其他器件参数的变化,则通过模型提取软件重新提取器件模型的方式获取。

3 性能通道的构建

通过构建性能通道,可确定前期确定的各类可能失效模式的功能参数能够在正常工作的范围之内,当各个功能参数严格位于性能通道内部时,就可以判定系统工作正常。

数字电路可能的失效类型包括3种,分别是:1) 逻辑功能失效。逻辑“0”输出低电平值VOL过大,导致后级电路将其甄别为逻辑“1”;逻辑“1”输出高电平值VOH过小,导致后级电路将其甄别为逻辑“0”。2) 时序失效。针对时序电路而言,由于节点电容带来时序延迟导致波形畸变,最终导致俘获了错误的逻辑电平值。3) 电流失效。电路的功耗电流持续增大,超出了设定的限值。从总剂量辐照测试结果可以看出,当电路发生功能失效时,其功耗电流增长并不是非常明显,所以可以排除电流失效的可能性。不管是逻辑功能失效还是时序失效,最终的失效表征都是俘获了输出错误的逻辑电平值。失效阈值的选取主要考虑的是后级电路的接受能力。

根据设定的阈值,首先确定子电路的正常工作范围,包括:1) SRAM单元:能够存储高低电平(存储静态噪声容限>0.1 V),能够正确读出高低电平(读出静态噪声容限>0.05 V);2) 异或门:最劣辐照与测试偏置下(辐照双端输入分别为0,1,测试双端输入分别为1,0)能够正常输出高电平>1.04 V;3) 与非门:最劣辐照与测试偏置下(辐照双端输入全为高电平,测试双端输入全为低电平)能够正常输出高电平>1.04 V;4) LUT:最劣辐照与测试偏置下输出高电平>1.04 V;5) 或非门:最劣辐照与测试偏置下(辐照双端输入全为高电平,测试双端输入全为低电平)能够正常输出高电平>1.04 V;

其次确定模块电路的正常工作范围,包括:1) 全局复位操作相关电路:上电复位信号能够正常输出(转变点电压<2.5 V);全局复位时电流脉冲峰值<1 A;2) CRC校验电路:CRC计算寄存器输出至CRC寄存器后比较得到的高电平>1.04 V 。3) 逻辑单元电路CLB:最劣辐照与测试偏置下(测试时选中待输出的CSRAM与辐照时不同)LUT输出高电平>1.04 V;4) 配置存储器电路:SRAM单元的读出静态噪声容限值>0.1 V。

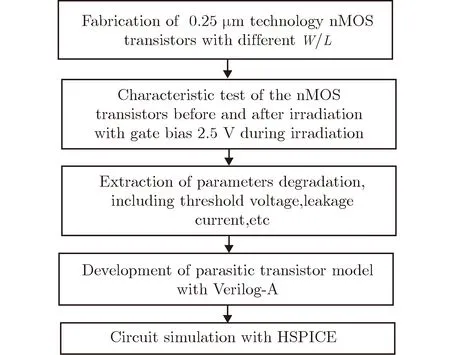

4 分层次仿真计算

通过电路仿真定量判断各个子系统的性能参数是否位于所有定义的通道内,构建考虑总剂量效应的器件模型和完备的总剂量效应电路模拟方法[8],见图6。根据已经构建的考虑总剂量效应的单管模型,在已知单管模型中总剂量效应敏感参数分布形式的基础上,获取各电路系统的输出功能参数值所对应的分布形式。首先在累积吸收剂量已设定的情况下,对器件的具体敏感参数进行MC抽样,利用电路模拟工具定量计算每次抽样下对应的电路功能参数输出值,并且对n次抽样得到的数值求取均值及其不确定度。

图6 引入总剂量效应后的电路仿真示意图Fig.6 Schematic of circuit simulation after introduction of total ionizing dose effects

5 X射线微束实验

常用于器件辐射效应研究的地面微束模拟源可以分为重离子微束、激光微束和X射线微束。其中重离子微束和激光微束与单粒子效应研究相关,X射线微束与总剂量效应研究相关,X射线微束应用于集成电路总剂量效应研究越来越广泛,原因在于待研究芯片中常常包含多种电路类型和不同的组成部分,全局辐照能够得到的失效信息非常有限,不利于进一步开展损伤机制分析、敏感单元甄别和针对性的加固设计等研究。

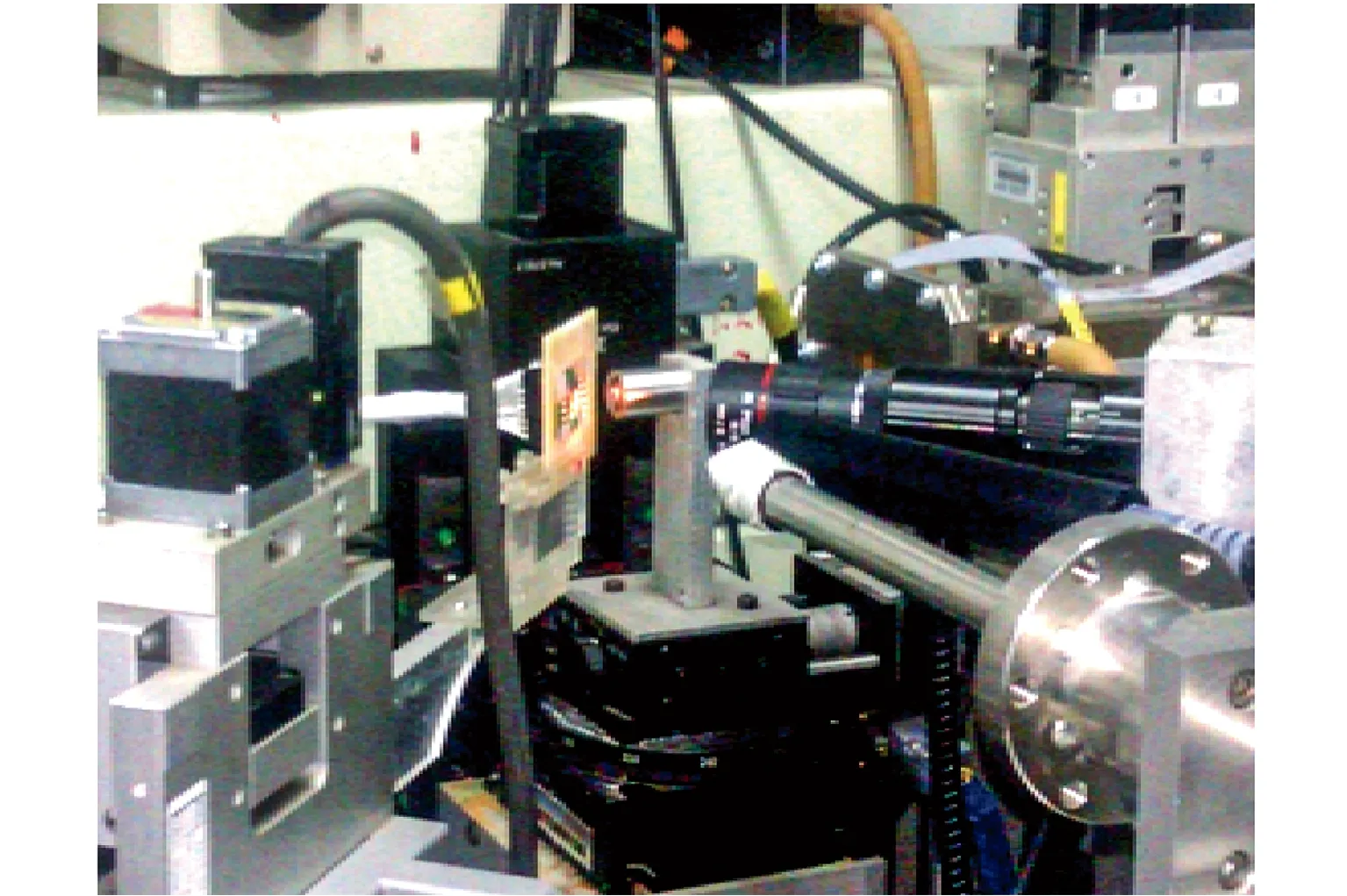

微束试验在北京同步辐射装置----北京高能物理所正负电子对撞机产生的同步辐射光源上的X射线荧光分析实验站进行,辐照环境为装置提供的聚焦X射线束,束斑尺寸为20 μm×20 μm,光子能量为15 keV。辐照过程中可通过铝箔屏蔽的方式调整束流强度。X射线经过铝箔、束流监测用探测器(电离室)、聚焦毛细管后入射到芯片表面,见图7。

图7 微束试验平台Fig.7 Setup of the X-ray microbeam test setup

依据全局辐照的测试结果可以看出,FPGA在总剂量效应作用下最易出现的失效表征是不能重新配置和无法完成上电初始化操作,上电启动和配置过程的相关操作与所涉及的电路是待分析的重点。通过微束辐照手段,针对CLB、BRAM、IOB、POR和DLL进行了区域辐照,测试发现,POR模块电路的部分区域受到辐照后,整个芯片发生了类似于全局辐照下SRAM型FPGA的总剂量效应的失效现象,由此可以推断,POR模块电路是整个芯片的总剂量效应的薄弱环节,在加固设计中需要进行重点防护。

利用X射线微束辐照测试方法,通过对SRAM型FPGA的不同模块电路进行分区域辐照,发现国产FPGA最易发生的总剂量效应失效模式是进行全局操作时对应的电流失效,引发失效的位置为POR模块电路。该结论解释了全局辐照失效现象中的不能重新配置和无法上电复位两类失效表征。

6 结论

以SRAM型FPGA的总剂量效应为例,建立了大规模集成电路抗辐射性能预测技术。编制了针对单管和单元电路的总剂量效应模拟计算程序,实现了对SRAM型FPGA从单管到功能模块的总剂量效应辐射损伤数值模拟。基于对辐射损伤机理的认识与对辐射损伤模型的分析,建立了单管总剂量效应损伤敏感参数的提取方法,利用辐照实验对模型进行了验证和确认。构建了SRAM型FPGA的总剂量效应敏感参数性能通道,给出了各个功能模块在不同累积吸收剂量下,敏感参数的阈值、裕量及其不确定度分布。

[1]赖祖武. 抗辐射电子学: 辐射效应及加固原理[M]. 北京: 国防工业出版社, 1998: 48-56. (LAI Zu-wu. Anti-Radiation Electronics: The Principle of Radiation and Hardening[M]. Beijing: National Denfense Industry Press, 1998: 48-56.)

[2]赵雯, 郭红霞, 何宝平, 等. 运算放大器总剂量辐射效应的PSPICE模拟计算[J]. 核电子与探测技术, 2010, 30(10): 1 296-1 301.(ZHAO Wen, GUO Hong-xia, HE Bao-ping, et al. Simulation by PSPICE for the total radiation dose effects of operational amplifiers[J]. Nuclear Electronics & Detection Technology, 2010, 30(10): 1 296-1 301.)

[3]孟志琴, 郝跃, 唐瑜, 等. 深亚微米 nMOSFET 器件的总剂量电离辐射效应[J]. 半导体学报, 2007, 28(2): 241-245. (MENG Zhi-qin, HAO Yue, TANG Yu, et al. Total ionizing dose effects of deep submicron nMOSFET devices[J]. Chinese Journal of Semiconductors, 2007, 28(2): 241-245.)

[4]吕荫学, 刘梦新, 罗家俊, 等. 辐照加固的500 MHz锁相环设计[J]. 半导体技术, 2011, 36(1): 49-54.( LYU Yin-xue, LIU Meng-xin, LUO Jia-jun, et al. Design of radiaiton hardened 500 MHz phase-locked loop [J]. Semiconductor Technology, 2011, 36(1): 49-54.)

[5]DING L L, GUO H X, CHEN W, et al. Development of TID-aware MOSFET model and its application[C]// RADECS, 2010.

[6]MIKKOLA E O, VERMEIRE B, PARKS H G. VHDL-AMS modeling of total ionizing dose radiation effects on CMOS mixed signal circuits[J]. IEEE Trans Nucl Sci, 2007, 54(4): 929-934.

[7]BROTHERS C P, PUGH R D. Simulating total-dose and dose-rate effects on digital microelectronics timing delays using VHDL[J]. IEEE Trans Nucl Sci, 1995, 42 (6): 1 628-1 635.

[8]TU R, LUM G, PAVAN P, et al. Simulating total-dose radiation effects on circuit behavior[C]// IEEE 32nd International Reliability Physics Symposium, 1994: 344-350.