基于EDA技术的汽车速度表设计

2018-05-19陈初侠曾奥运蒋光好

陈初侠 袁 涛 曾奥运 蒋光好

(巢湖学院机械与电子工程学院 安徽巢湖 238000)

近些年来,随着我国国民经济的不断发展,人民的消费水平不断提高,汽车数量也是逐年增长,随之带来的汽车安全问题也越受到人民的关注。速度作为汽车行驶过程中重要的指标参数,因此汽车速度表的设计也被要求更精确,更快速,更灵敏。

传统的汽车速度表是利用变速器或分动器的输出轴带动仪表中指针显示汽车速度,这种机械结构方式显示出的速度会有较大的误差。基于EDA技术设计的汽车速度表,以其价格便宜、安全可靠、使用方便等优点,而受到人们的普遍关注[1-3]。本文以现场可编程逻辑器件(FPGA)为设计载体,以硬件描述语言(VHDL)为主要表达方式,以QuartusⅡ开发软件和ZY11EDA13BE开发系统为设计工具设计的汽车速度表[1-3],能够实现速度的精确显示和超速报警功能,完全满足汽车速度表的设计要求。

一、汽车速度表的功能和整体结构

(一)汽车速度表的主要功能。这里所设计的汽车速度表具有以下功能:1.能显示汽车的速度,单位是km/h;2.速度用数码管显示,且要精确到小数点后两位;3.显示的最高时速为360km/h,超过此速度会出现报警;4.速度采样周期为10秒。

为了设计简化,在设计过程中,假设车轮每转一圈,有一传感脉冲,每转一圈代表1m的距离。

(二)汽车速度表的整体结构。汽车速度表的整体结构如图1所示,其中虚线框内部是需要设计的部分,它包括分频器模块、计数器模块、单位转换模块、译码显示器模块。

图1 汽车速度表的整体结构图

二、汽车速度表的设计

汽车速度表的设计是采用层次化的设计方法来进行,分底层各模块电路的设计和顶层电路的设计。

(一)底层电路的设计。底层电路有四个电路模块,分别是分频器电路模块、计数器电路模块、单位转换电路模块和数码管译码显示电路模块,他们都通过VHDL语言进行设计。

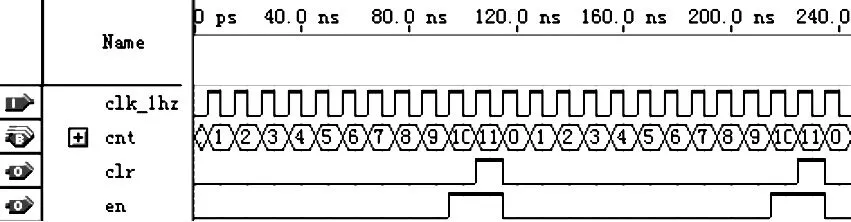

1.分频器电路模块。该模块的功能是由基准时钟分频出两个周期信号,其仿真波形如图2所示。clk_1hz为频率为1hz的基准时钟,clr和en为被分频出的周期为12秒的信号,他们的占空比不一致,都为后面的计数器电路模块服务。

图2 分频器电路模块仿真波形

2.计数器电路模块。该模块的功能是对输入的车轮脉冲个数进行计数,其仿真波形如图3所示。clk为传感器感应的车轮脉冲信号;count为10秒钟内对车轮脉冲个数的计数结果;speak为脉冲计数超过一定值时(比如1000)的报警信号,高电平有效。

图3 计数器电路模块仿真波形

当en=“0”时,计数器进行计数工作;当en为上升沿时,计数结束并把计数结果传输给输出信号count。由图2可知en的周期为12秒,处于“0”的时间刚好为10秒,所以计数是在10秒钟内对车轮的脉冲个数进行计数。当clr=“1”时,对计数结果进行清零操作;当clr=“1”时,不对计数结果进行清零。

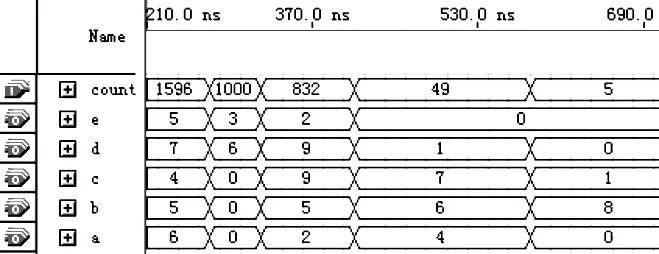

3.单位转换电路模块。该模块的功能是进行单位转换,把m/s转换成km/h,其仿真波形如图4所示。例如,当在10秒钟内的计数结果为832时(一个脉冲为1m),即10秒钟内车轮跑了832m,速度为83.2m/s。转换为km/h后其数值应为83.2×3.6=299.52,从波形图可以看出,理论值与实验结果刚好吻合。

图4 单位转换电路模块仿真波形

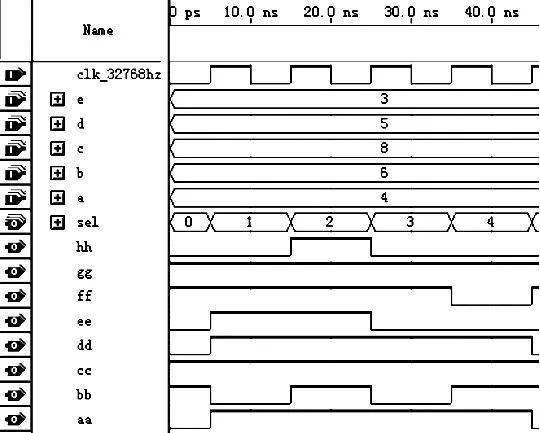

4.数码管译码显示电路模块。该模块的功能是把转换为km/h的速度值通过数码管显示出来,其仿真波形如图5所示。这里采用动态的方式进行显示,数码管是“共阴极”结构。

输入信号clk_32768hz是频率为32768hz的扫描信号,即每秒钟数码管依次亮灭32768次。由于扫描频率过高,人的视觉有暂留现象,所以看上去所有的数码管都是一直亮着的。信号 e、d、c、b、a为速度值,图示值为 358.64km/h。

输出信号sel为数码管扫描片选信号,当sel=“0”时,最右边的数码管点亮,此时应显示“4”,以此类推,当 sel=“4”时,最左边的数码管点亮,此时应显示“3”。gg、ff、ee、dd、cc、bb、aa为数码管的 7段,hh为小数点。例如,要显示“8.”,则片选信号 sel应等于“2”,hh、gg、ff、ee、dd、cc、bb、aa全部为高电平,由图5可以看出,与实验结果刚好吻合。

图5 数码管译码显示电路模块仿真波形

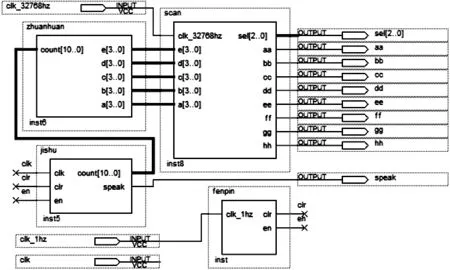

(二)顶层电路的设计。顶层电路设计采用原理图输入方式,通过调用生成的各底层电路模块符号,并将他们做适当连接以实现顶层文件的设计[4],电路如图6所示。

图6 汽车速度

图6中,clk_1hz为基准时钟、clk为车轮脉冲信号、clk_32768hz为数码管扫描时钟信号;speak为超速报警信号,sel为数码管扫描片选信号,aa、bb、cc、dd、ee、ff、gg、hh 为数码管显示输出。

三、汽车速度表的硬件验证

本设计选用湖北众友科技实业股份有限公司生产的ZY11EDA13BE实验箱作为硬件验证平台,同时选用Altera公司的EP1K30QC208-2作为主控芯片。该芯片是一种基于查找表结构的现场可编程逻辑器件,它的基本逻辑单元是可编程的查找表,能够实现组合逻辑运算,并可用可编程寄存器实现时序逻辑运算[1-3]。因此,只要对汽车速度表顶层文件的输入输出引脚进行锁定,然后重新编译和下载,就可以进行汽车速度表的硬件验证。

硬件验证结果如图 7 所示,图(a)、(b)、(c)、(d)显示的速度分别为 7.20km/h、57.60km/h、230.40km/h、460.80km/h,其中显示速度为460.80km/h时,右下方出现一个红色报警。实验表明:所设计的汽车速度表精度到达小数点后两位,并且当速度高于360km/h时会出现报警,基本实现了汽车速度表的全部功能。

图7 汽车速度表的硬件实现

四、结语

本文采用EDA技术“自上而下”层次化设计方法设计汽车速度表,即从汽车速度表整体系统功能出发,将系统分解为各功能模块,每个功能模块分别由VHDL语言进行设计并通过仿真测试,生成元件符号以实现底层电路设计[4];顶层电路采用原理图输入方式进行,通过调用各底层电路模块符号元件,并将他们做适当连接以实现顶层文件的设计。最终将设计好的顶层电路下载到EDA实验箱上进行验证,结果表明,本设计能够实现所要求的全部功能。同时,底层电路采用VHDL语言进行设计,提高了系统可移植性,维护和升级也比较方便。另外核心芯片内部设计电路,减少器件使用数量缩减了系统体积,避免高密度复杂连线,提高了系统稳定性[4]。

参考文献:

[1]刘凯,王红航.出租车计费器的EDA设计与实现[J].电子元器件应用,2010(7):69-71.

[2]王红航,张华斌.电子密码锁的EDA设计与实现[J].电子元器件应用,2009(6):35-37.

[3]刘凯,王红航.电子抢答器的EDA设计与实现[J].电子元器件应用,2010(8):54-57.

[4]李响,何东钢,李昕欣,等.出租车计价装置分层次设计的优化研究[J].实验室科学,2016,19(1):62-65.