一种LRM结构的高速采集设计

2018-05-04张卫清中国电子科技集团公司第三十八研究所安徽合肥230088

陈 勇,张卫清(中国电子科技集团公司第三十八研究所,安徽 合肥 230088)

0 引 言

在线可更换模块(LRM)结构有着非常明显的特点和独特的优势。在电讯方面其模块功能独立化, 在结构方面要求模块具有尺寸互换性, 连接配合等部分的几何参数独立化, 必须能通用、互换或兼容。要满足该要求, 首先电讯设计上要高度集成化;其次在结构上也一改原来在线可更换模块(LRU) 的结构形式, 以新的结构模块及各种模块技术来使结构设计达到新的水平, 以实现与国外先进的模块技术同步发展。该结构已在联合标准化航电系统架构协会(ASAAC)广泛采用。

1 高速采集简介

数据采集技术是一种流行且实用的电子技术。它广泛应用于电子对抗、雷达探测、信号处理、仪器仪表等领域[1]。近年来, 随着数字化技术的不断发展, 数据采集技术也呈现出速度更高、通道更多、数据量更大的发展态势。要设计先进的多通道高速数据采集电路, 必须有效解决高速采集、高速处理和高速数据传输三大难题[2]。本文以一个典型的采集电路为例, 介绍电子战领域中一款高速数据采集电路的设计。

2 硬件设计

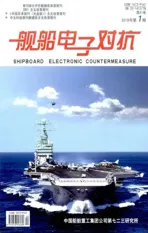

这里的八通道高速采集板主要由4片模数转换器(ADC)(8个通道)、1个高性能现场可编程门阵列(FPGA)、2个多通道光纤模块和1个二代LRM连接器组成。其功能框图如图1所示。

图1 数字板卡组成框图

2.1 LRM连接器

LRM连接器被广泛运用于ASAAC标准的模块中。具体选用哪款货架连接器或定制满足特定要求的连接器,须综合考虑满足射频、光口、控制口等需求。根据系统的特点,本模块设计方案选用LRM的二代产品:型号LRMS2-A135G2-B72T12-T2,其主要的电气性能指标如下:

传输射频信号部分,特性阻抗为50 Ω;高速差分数字信号最大传输速率6.25 Gbps;单芯额定工作电流1 A,耐电压100 V;MT光纤盲配接头部分插入损耗≤1.5 dB。

连接器被分为A、B 2个腔。具体A腔有135芯Φ0.4差分接触件,2个光纤MT模块;B腔包含72芯Φ0.4差分接触件;12芯射频接触件RF(F)-12J3506E,适配射频线缆为Gore CXN3506,内导体直径为0.5 mm,外导体直径为2.0 mm。

连接器端接方式为差分接触件弯式焊接印制板,光纤接触件甩线,射频接触件焊线。其结构图如图2所示。

图2 LRM连接器结构尺寸图

2.2 高速ADC

高速采集板的核心器件就是高速ADC芯片,这里选择ADI公司的AD9680。该芯片为二通道1.0 Gsps的ADC,分辨率14 bit,每通道功耗1.65 W,输入峰峰值1.46 Vp-p到1.94Vp-p,其输出接口为JESD204B (Subclass 1)协议标准[3]。JESD204B相比较早的LVDS接口有线上速率高、接口线少等优点,极大地简化了布局布线要求[4]。

2.3 高性能FPGA

高速采集中的FPGA负责ADC数据的接收、比特译码和解串降速,运用软件无线电思想作一定的信号预处理,并把形成的包含信号幅度和相位信息的基带IQ数据通过高速光纤接口送给处理系统[5]。一般雷达和电子对抗在ADC后需做数字下变频(DDC)运算,特别是在针对宽带信号作DDC等处理时,需要大量乘法器资源[6]。根据资源的使用情况,这里选择XILINX 的第7代28 nm工艺的高性能现场可编程门阵列(FPGA)VC7VX690T-2FFG1927I[7]。其主要资源如表1所示。

表1 FPGA资源列表

2.4 数据传输分析

数据传输带宽也是数据采集板的重要指标。特别是宽带采集系统,其待传数据量巨大。本模块最大传输数据量估算如下:8(通道)×2(I/Q)×0.5 GHz(采样率)×16 bits(位宽)×1.25(8B/10B)=160 Gbps。如果使用24个tranceiverip进行传输,每个ip核工作的线率需大于6.7 Gbps。板上的2个十二合一高速光模块实现海量数据传输支持。

2.5 孔径抖动分析

ADC的性能与采样时钟质量密切相关。采样时钟的抖动会导致AD的信噪比下降。因此设计时钟电路时要特别注意时钟信号的完整性,减小时钟的附加抖动,并尽可能采样无源电路给ADC供时钟。受孔径抖动的影响,最大信噪比公式为:

(1)

如果考虑量化噪声和抖动,则信噪比为:

(2)

式中:Q=A/2N-1,N为ADC位数;A为常数。

理想信噪比和模拟输入频率及抖动的关系如图3所示。

图3 理想信噪比和模拟输入频率及抖动的关系

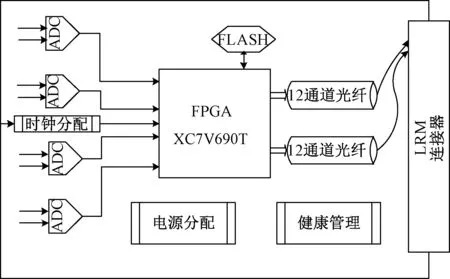

2.6 热仿真分析

考虑高速采集模块的热量大且元件数量多及分布式排布使用的特点,采用传导冷却散热,模块内部产生的热量均通过模块两端的肋片经机架冷板导出。

本高速采集模块热控技术要满足如下要求: 模块的主要热控设计对象为多个发热元件;元器件壳体温度≯100 ℃;环境温度≯55 ℃。

本高速采集模块经专业热分析软件热分析计算表明,安装冷板的温度设定为定温度边界,温度为54 ℃,模块与导冷插箱的接触热阻取为0.6 ℃/W时,发热元件最高温度为81 ℃,低于各元件允许的工作温度上限,满足设计要求。

发热器件温度分布云图如图4所示。

图4 发热器件温度分布云图

3 软件设计

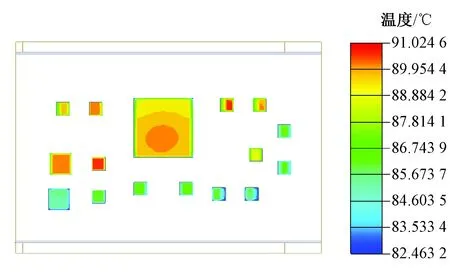

对于数字化接收,目前广泛采用基于软件无线电设计思想的数字化接收机技术实现数字正交解调,用于实现解调的电路被称为DDC,具有数控振荡器(NCO)及可编程高效数字滤波器,因此在采样时钟确定的情况下,可在较宽范围内实现多种带宽信号的解调和匹配滤波。基本实现框图如图5所示[8]。

图5 数字I/Q正交解调实现原理框图

ADC采样后的中频数字信号通过JE204B总线协议送给FPGA。FPGA首先需要从高速串行信号中恢复并降为低速的并行ADC数据信号,这样便于内部处理。然后经过并行宽带数字下变频处理,得到包含原始信号幅度和相位信息的基带IQ信号,再经过光纤送给信号处理系统[9]。并且需要做好定时控制,保证多路ADC之间保持同步处理。FPGA软件处理流程如图6所示。

图6 FPGA软件处理流程图

4 指标测试与高速PCB注意事项

4.1 指标测试

ADC在实际运用中,一般最关注信噪比(有效位)这个指标,即便对于同一个ADC芯片,信噪比指标跟采样率、输入信号频率、采样时钟的质量等也密切相关。信噪比越高,接收机的瞬时动态范围就越大。这里ADC工作在最高采样率1 Gbps,输入信号最高频率为950 MHz,测得的信噪比优于52 dB。测试指标对比如表2所示。

表2 测试指标对比

4.2 制电路板(PCB)设计注意事项

高速PCB上的工作频率已越来越高,如果走线布局处理不当,将会降低信号完整性,导致PCB设计失败。设计PCB时需要考虑如下准则:从电磁兼容和抗干扰的角度来优化器件的布局;电源走线考虑到电流容量,尽量画电源平面;高速模拟信号、高速差分信号走线要经过阻抗计算;考虑大功率器件散热问题;时钟线、模拟信号线、差分线、JTAG链等关键走线需重点关注;电源模块散热焊盘需打散热密孔;模拟信号走线附近最好不要有数字信号过孔等。

5 结束语

在目前和不远的将来,雷达与电子战装备工作的瞬时带宽会越来越宽,特别是在超宽带合成孔径雷达(SAR)技术和超宽带电子战接收机中,已经对提高采样率的需求越来越迫切。随着半导体工艺的不断发展,高速ADC芯片技术的发展也是日新月异,高速采集的瞬时带宽及处理能力将会得到进一步提高。本文给出的基于LRM结构的八通道高速采集模块采用模块化、标准化设计,可以在一定程度上满足通用化需求。通过对板卡的实测指标及其在实际装备上的应用情况可以得出,本模块的设计是可靠的、有效的。

[1] 沈兰荪.高速数据采集系统的原理与应用[M].北京:人民邮电出版社,1995.

[2] 杨胜华.基于FPGA的1GHz高速采样处理平台设计[J].电讯技术,2007,47(6):163-166.

[3] JOHNSON H,GRAHAM M.高速数字设计[M].沈立,朱来文,陈宏伟,等译.北京:电子工业出版社,2006.

[4] 周润景,袁伟亭.Cadence高速电路板设计与仿真[M].北京:电子工业出版社,2006.

[5] 洪萌,耿相铭.基于FPGA高速并行采样技术的研究[J].现代电子技术,2011,34(5):91-95.

[6] 田耘,徐文波.XilinxFPGA开发实用教程[M].北京:清华大学出版社,2008.

[7] 褚振勇,翁木云.FPGA设计及应用[M].西安:西安电子科技大学出版社,2002.

[8] 吕影影,徐强,催志强.一种基于多项滤波的高速信号处理算法[J].雷达科学与技术,2014,12(2):161-165.

[9] 吴兵,张飞,伍小保.宽带数字波形产生中的广义多项滤波[J].雷达科学与技术,2016,14(4):376-400.