基于stm 32f407的精确时钟同步协议的实现

2018-04-16张端阳付忠敏

张端阳 肖 力 付忠敏

(华中科技大学自动化学院 武汉 430074)

1 引言

工业现场的数据采集变得越来越模块化,但当需要测量多个外部的数据时,可能需要多个模块。将这些由传感器采集的数据通过网络上传的时候,由于没有时间信息,远程上位机不能很好将采集数据融合处理,一般只能独立的对采集上来的数据处理。为了实现对采集数据的时钟同步,需要对数据采集模块间进行时钟同步。

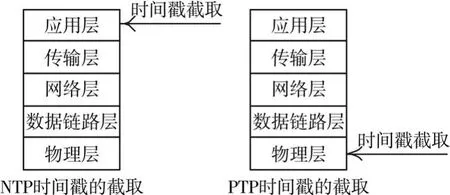

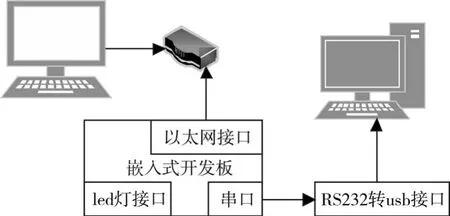

当前几种比较流行的时间同步协议有NTP(Network Time Protocol)[1]和 PTP(Precision Time Protocol)[2],两者的原理类似,都是实现主时钟节点和从时钟节点间的时间同步,其中PTP协议是网络测量和控制系统时钟同步协议(IEEE1588协议)的简称,具体的差异如图1所示。从图中可以看出,NTP和PTP时间戳的截取的位置不同。NTP获取的时间戳的位置是应用层,而PTP时间戳的截取的位置是在物理层。正是由于获取时间戳的位置不同,这样PTP可以有效地去除运行操作系统和TCP/IP协议栈时间抖动对时钟同步的影响。但是由于PTP获取时间戳位置的在物理层,所以需要特殊的硬件支持,即在具体的应用中硬件需要支持PTP,这个实际的硬件设计带来了一定的成本,但是NTP不需要硬件支持。获取时间戳的位置的差异促使PTP的同步时钟精度是NTP同步时钟精度的10000倍。PTP的同步时钟精度是亚微秒级(100ns)。在该精度下可以满足大多数时间同步的精度要求,比如PTP可用于高速铁路地震预警系统采集设备[3]。

图1 时间戳截取的位置

由于上述的对硬件特殊要求[4~9],这使 PTP 的实用性远没有NTP简单。为了实现高精度的同步并且去掉对硬件时间戳的依赖,由图1可知捕获时间戳的位置越接近物理层时间精度越高,故本文实现在数据链路层上捕获时间戳。这样既可以去掉对硬件时间戳的依赖同时提高时钟同步精度。

2 时间同步的原理

PTP时钟同步的基本原理是通过消息传递机制使控制网络中的时钟节点与最精确的时钟节点间保持同步。最精确的时钟节点被称为主时钟,其它的时钟节点被称为从时钟。当有时钟加入到控制网络中,该时钟节点通过最佳主时钟算法确定该控制网络中主时钟,进而使用PTP协议中的相关算法与该主时钟同步。

2.1 时钟同步的基本原理

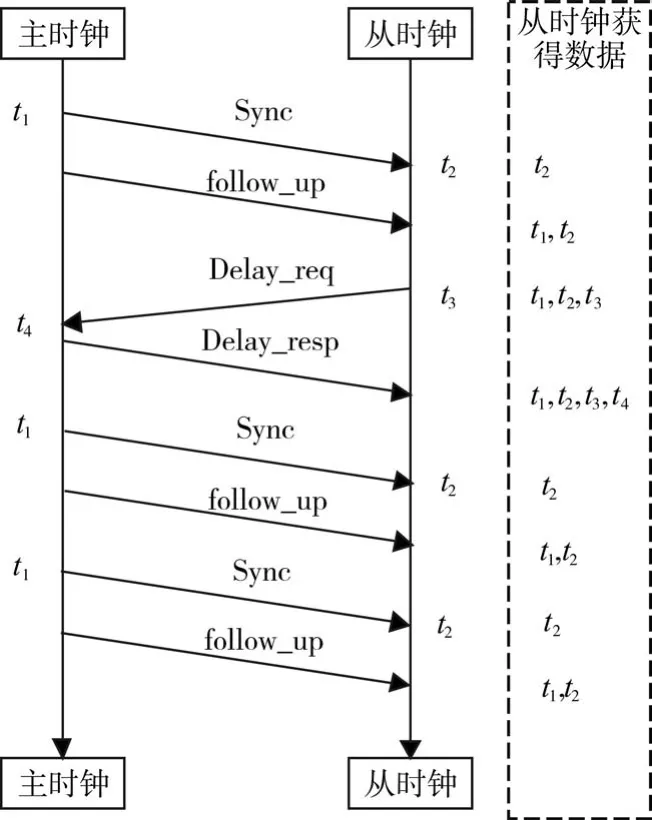

PTP时钟同步的基本原理如图2所示,其基本实现可以分为下面基本步骤:

第一步,主时钟首先广播一个Sync(同步)报文,此时从时钟记录接收到的Sync报文的本地时间戳t2。

第二步,紧接第一步主时钟发送一个follow_up(跟进)报文,此报文记录的Sync报文发送时主时钟的时间戳t1。当从时钟接收follow_up报文时,从时钟记录此时的报文中的时间戳t1。

第三步,从时钟发送一个Delay_req(延时请求)报文,并记录下此时的本地发送时间戳t3。

第四步,主时钟接收到Delay_req报文时,记录此时接收到的主时钟本身的时间戳t4,然后主时钟发送一个Delay_resp(延时响应)报文,该报文记录时间戳t4。当从时钟接收到Delay_resp报文时,从中提取时间戳t4。

图2 PTP时钟同步的基本原理

经过上面的四步后,从时钟拥有了时间戳t1,t2,t3和t4。通过上面的四个时间戳我们可以计算出此时报文的网络传输延时时间和从时钟相对于主时钟的时偏移量。这样完成了主从时钟节点间的同步。

主从时钟间网路延时计算:

式(1)成立的条件是报文在主从时钟节点间传输延时的时间是相等的,同一局域网或者子网中上面的假设是成立的。当计算出上面的时钟偏移量和主从时钟节点间的网络传输延时,也就完成了主从时钟节点间的同步。

为了保持主从时钟节点间的精确同步,主时钟节点周期性的发送Sync和follow_up报文,从时钟节点接收的报文后,对报文处理并更新时间。同时从时钟节点周期性的发送Delay_req报文,主时钟节点记录接收报文的时间戳,并将时间戳记录在Delay_resp中并发给从时钟节点,从时钟节点接收到延时请求的响应报文,处理后重新计算网络的传输延时。

注意上面的时间同步的原理成为两步通信原理。如果直接将发送Sync报文的时间戳直接记录在Sync报文中,此时不发送Follow_up报文,则实现的是一步通信原理。

2.2 最佳主时钟算法

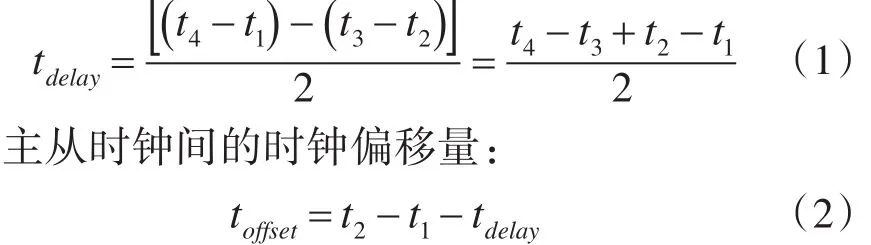

IEEE1588协议规定在一个PTP同步系统中只能存在一个主时钟,最佳主时钟算法在多个潜在的主时钟中决定哪一个会成为PTP同步系统的主时钟节点。

最佳主算法[2]的步骤:

首先比较两个时钟节点的优先级,如果优先级相同则比较两个时钟节点的时钟类型,如果时钟类型相同则继续比较两个时钟节点的时钟精度,如果两个时钟的精度还相同,继续比较两个时钟节点的时钟稳定性,如果时钟稳定性也相同,就比较两个时钟节点的时钟ID,选择两个时钟的ID数字较小者为最优主时钟。这样可以从两个潜在主时钟中选出一个最优的主时钟,而且系统内所有时钟的最佳主时钟算法相同,同一个时钟同步系统中每个时钟计算得到的最佳主时钟相同。最佳主时钟算法的流程图如图3所示。

图3 最佳主时钟算法

通过上面的最佳主时钟算法,可以从同步的控制系统中挑选出最佳的主时钟。这样系统中所有其他的从时钟同步于系统中的当前的主时钟。

2.3 PTP中报文格式

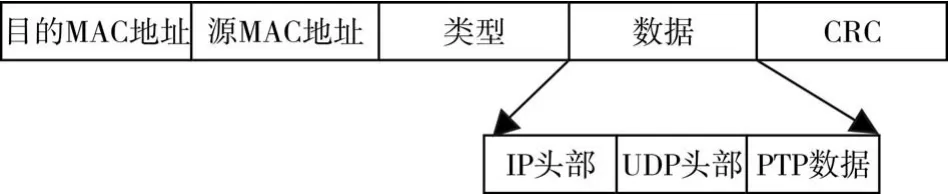

1)PTP封装的格式

PTP的报文可以在封装在多种以太网[4]的报文中例如UDP/IP,UDP/IP6,IEEE802.3/Ethernet,DeviceNET等等。在本文中,将PTP封装在以太网的帧中,使用了UDP/IP,其具体的封装的格式如图4所示。

图4 PTP数据包的封装

2)PTP数据包的头部

所有的PTP数据包都包含一个头部信息,其具体的封装的格式如图5所示。

图5 PTP报文头部

(1)传输协议(半字节):如果PTP协议建立在UDP/IPv4协议的基础上,则此处值为0x01。

(2)报文类型(半字节):用整数表示报文的类型,0表示Sync报文,1表示Delay_req报文,4~7是保留,8表示Follow_up报文,9表示Delay_resp报文,B表示Announce报文。

(3)PTP协议版本:IEEE1588v2版本报文,此值设置为2。

(4)报文长度:PTP报文中的所有字节数包括PTP报文中的头部。字节数从报文的头部到PTP报文结尾。

(5)域号:指定报文所处的域号。

(6)报文标志域:标志域中每一个二进制位表示报文的一种属性。主要指示出报文是单播通讯还是两步通讯。本文实现的是两步通讯。

(7)修正域:修正域中的值由透明时钟指定。指示了报文在透明时钟中的驻留时间。在本次实现中没有用到。

(8)发送报文时钟ID:包含时钟ID和端口号。

(9)报文序列号:指定报文发送的序号,由上面同步的基本原理的讲解可知,Follow_up报文序号与Sync报文序号相同,Delay_resp报文序号与Delay_req报文序号相同。

(10)控制域:控制域指明PTP报文是哪种报文,0x00表示Sync报文,0x01表示Delay_req报文,0x02表示Follow_up报文,0x03表示的是Delay_resp报文。

(11)报文发送时间间隔:表示相应报文发出的时间间隔,可以表示Announce,Sync等报文的发送时间间隔。

3)Announce报文

Announce报文主要用于确定时钟同步系统中的最佳主时钟。当系统上电后潜在的主时钟节点发送Announce报文,其他的节点(包括此时潜在的主时钟本身)接收到Announce报文后,运行最佳主时钟算法从时钟同步系统挑选出最佳主时钟。Announce报文的格式如图6所示,各字节解释如下:

(1)时间戳:该值设置为0或者本地时钟的估计值,误差在±1s,本文的实现没有使用该时间戳,直接置为0。

(2)UTC时钟偏移量:该值表示PTP标准时钟相对于UTC(协调世界时)的偏移量,该值是一个量,设置为33。

图6 Announce报文格式

(3)超主时钟优先级1和超主时钟优先级2:主时钟的优先级1和主时钟优先级2的级别。

(4)超主时钟时钟性能:主时钟的时钟性能包括时钟类型,时钟精度等。

(5)超主时钟ID:主时钟的时钟标识号。

(6)超主时钟通信级数:本地时钟距离主时钟的传输路径的距离,该值越小表示本地时钟距离超主时钟越近。默认的情况下设置为零。

(7)时钟源:表示超主时钟的时钟源。时钟源包括原子时,GPS时钟,陆地无线电,PTP时钟源,NTP时钟源,其他时钟源或者内部振荡器时钟源。默认的情况下是内部振荡器时钟源。

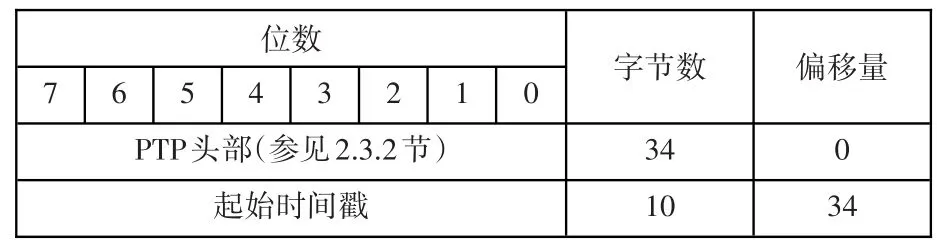

4)Sync和Delay_req报文

Sync和Delay_req报文的封装格式相同,只是标识位的设置不同,其报文封装如图7所示。

图7 Sync和Delay_req报文格式

起始时间戳:记录报文携带的时间戳。

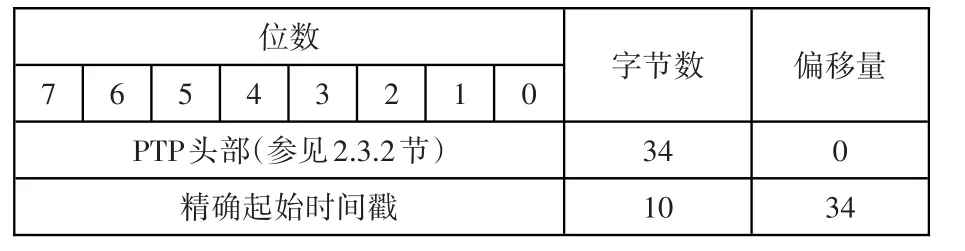

5)Follow_up报文

Follow_up报文的封装格式如图8所示。

图8 Follow_up报文格式

精确起始时间戳:记录的是发送Sync的精确的起始时间戳。

6)Delay_resp报文

Delay_resp报文是对Delay_req报文的回复,该报文是由主时钟发送。报文的封装的格式如图9所示。

图9 Delay_resp报文格式

(1)接收时间戳:主时钟接收到Delay_req报文的时间时间戳。

(2)请求端口号:Delay_req报文发送的从时钟的端口号。

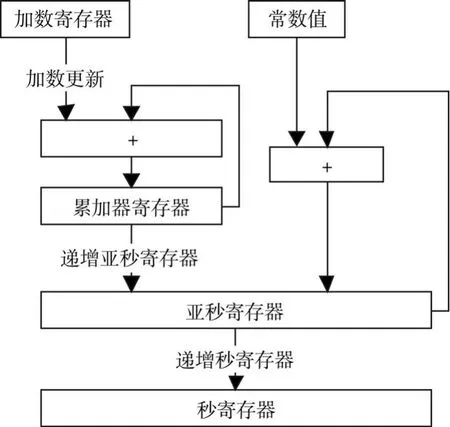

2.4 从时钟频率的调整

由于主时钟节点和从时钟节点时钟频率的不一致性,以及从时钟的外部晶振源的频率随着周围温度和湿度的变化而发生漂移。基于以上的原因,本文中加入了从时钟的时钟频率的调整算法,来补偿频率的变化。由于本文的实现是基于stm32系列的arm芯片,其提供的寄存器完成精密校准方法更新系统时间方框图如图10所示。

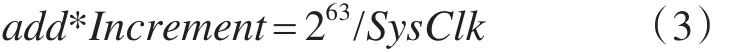

图中加数寄存器的值与常数值是直接相关的。在每一个系统时钟周期中加数寄存器中的值累加到累加器寄存器中。当累加器寄存器中值溢出时,将常数值加到亚秒寄存器中。当亚秒寄存器中的值超过109时,秒寄存器中的值加1。这样就可以很精确地控制系统的时间。累加器寄存器和亚秒寄存器是两个32位的寄存器,由上面的寄存器联动,我们可以将上述两寄存器看做一个64位的寄存器,则stm32的系统时钟频率,寄存器位数,加数寄存器和常数值间的关系如下

图10 精密校准更新系统的时间

其中add表示加数寄存器的值,Increment是亚秒寄存器递增常数值,SysClk是系统时钟。ptp时钟周期和亚秒寄存器递增的常数值间的关系如下

其中 ptptick是ptp时钟周期,Increment是亚秒寄存器递增常数值。

由式(3)和式(4)可知,当ptp时钟周期是20ns,并且系统时钟频率SysClk=168MHz,此时Increment为43,加数寄存器add值为0x4C19EF00。

为了对从时钟的频率进行精密的校准,软件必须使用主时钟发送的Sync报文对从时钟频率偏移进行计算,并更新加数寄存器以来调整从时钟时钟频率。实现该算法的步骤如下

1)使用0x4C19EF00初始化加数寄存器,并使用43初始化亚秒递增寄存器的常数值。分别记为FCV0和Inc0。

2)主时钟第n次发送Sync报文到从时钟的时间戳记为Mst(n)(master sync time)。从时钟在其本地时钟在Sct(n)(slave clock time)时刻接收到该同步报文,使用如下公式计算Mct(n)(master clock time):

其中Mtsd(n)表示是主时钟到从时钟网络延时(master to slave delay)。

3)当前同步周期的主时钟计数Mcc(n)(master clock count)的计算公式如下其中主时钟到从时钟网路延时在n时刻与n-1时刻认为相等的。

4)当前同步周期的从时钟计数Scc(n)(slave clock count)的计算公式如下

5)当前同步周期的主从时钟差值Cdc(n)(clock Differentcount)的计算公式:

6)从时钟的分频系数Fc(fn)(Freq Scale Factor)的计算公式如下:

7)加数寄存器的频率补偿值 Fcv(n)(Freq Compensation Value)的计算公式如下:

上述的算法可以在一个同步周期内对时钟频率补偿值进行修正,但是由于网络传输的影响可能需要多个周期来对频率补偿值进行修正。

3 时间同步协议的实现

3.1 主时钟的实现

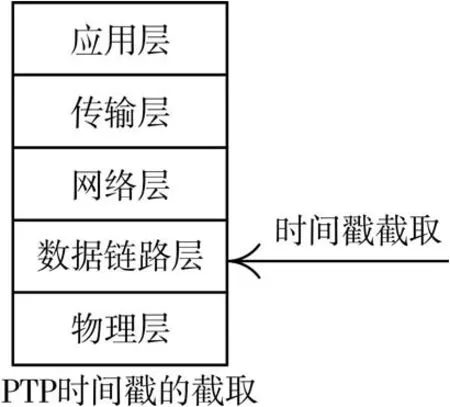

主时钟选择的是本地的主机,在该主机上实现的ptp的主时钟。所用的软件是linuxptp。这样上位机和自己开发的嵌入式的开发板之间就可以构成ptp的主从时钟。测试所用到的网络结构如图11所示。

图11 测试网络结构

3.2 从时钟的实现

在本文中,实现了以stm32f407为微控制器核心的嵌入式操作系统。为了使后期编程的方便,在stm32f407中移植了嵌入式操作系统。由于通讯需求,需要在stm32f407上移植TCP/IP协议栈。为了移植简便,本文选择的嵌入式TCP/IP协议栈是Lw IP(轻型IP协议栈)。主要实验选定的PHY是dp83848。虽然该PHY不支持IEEE1588的硬件时间戳,但是由于为了使实现的ptp更加的通用,捕获时间戳的位置有原来的物理层提升到数据链层,如图12所示。

图12 本实验中时间戳捕获的位置

在数据链路层捕获PTP时间戳使PTP精度有一定的下降,但是由于去掉了物理层的硬件特殊要求并且该时钟精度也可以满足大部分的应用的场合,所以实验中实现的在数据链路层捕获时间戳。在Lw IP移植的过程中,主要完成对PHY驱动配置函数编写,Lw IP的底层接收和发送的函数,Lw IP初始函数等。除了上述函数外,为了使Lw IP协议栈与嵌入式操作系统匹配,需要编写操作系统与Lw IP协议栈之间的接口函数即操作系统的模拟层。这些函数实现的功能是线程的创建函数,信号量创建、释放、等待和释放信号量内存函数,互斥信号量的创建、锁定、解锁和释放互斥信号量内存函数,消息邮箱的创建、释放、等待和消息邮箱内存释放函数。

完成上面的函数后,可以在上位机即PC机ping嵌入式的开发板,可以检测上位机与开发板间的连接是否正常。测试的命令:

ping 192.168.1.16-i0.001

其中ping是网络测试的命令,192.168.1.16是嵌入式开发板的ip地址,-i0.001表示发送ICMP报文的时间间隔。测试的结果如表1所示。

其中min是rtt最小值,avg是rtt的均值,max是rtt的最大值,mdev是rtt的标准差该值越小表示网络越稳定。测试中一共发送了1645个数据包,测试的过程中没有丢失数据包。

在上面移植的基础上,本文对Lw IP中的pbuf数据接收进行了修改加入表示时间的两个32位int类型的数据,用于存储接收和发送以太网数据的本地时间戳,具体结构如下

structpbuf{

……

#ifdef LWIP_PTP

int time_sec;

int time_nsec;

#endif

};

其中time_sec用于存储秒数,time_nsec用于存储纳秒数。定义上面的与ptp有关的数据结构,实现相关的函数。

综上所述从时钟节点的软件框架如图13所示。

图13 从时钟节点软件架构

3.3 测试结果

在上位机的命令窗口中敲入相应的命令行:

ptp4l-ienp8s0-m-S

其中enp8s0是主机的网口的名字,-m表示打印相关的信息-S表示使用的软件时间戳。

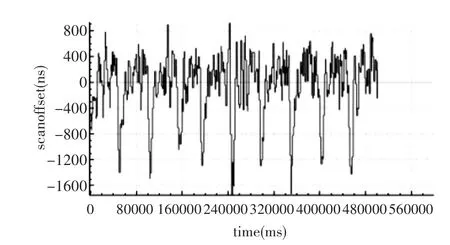

测试的到的数据结果如图14所示:

图14 同步时间测试的图形

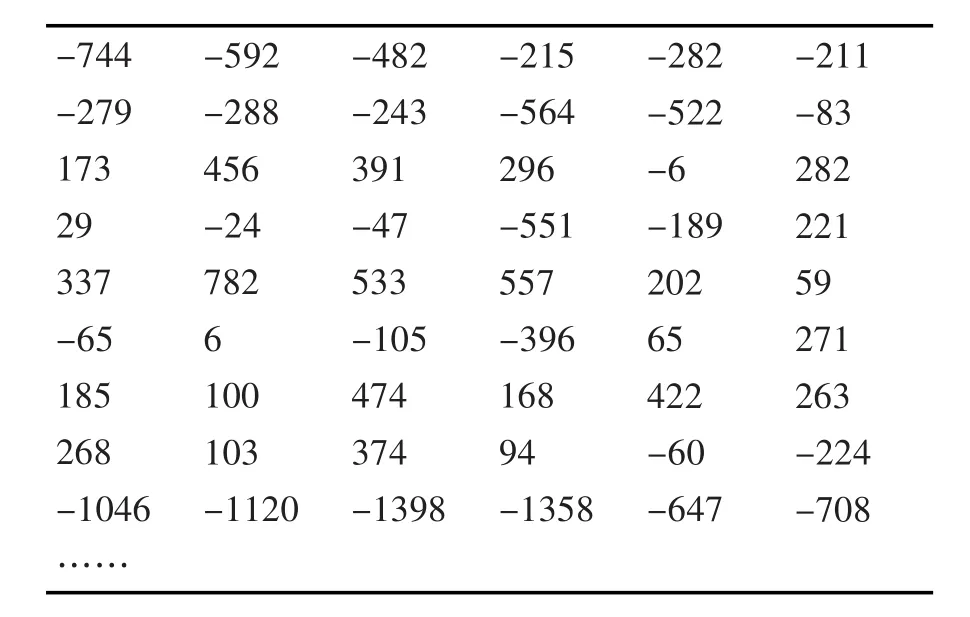

由上图的可知,主从时钟间的偏差在2us内,这是满足设计的要求。将上述收集到的数据制成表格的形式如表2所示。

表2 时钟同步时间偏移(单位:ns)

本实验中一共采集了515组数据,每组数据间的时间间隔为1s,即一共采集数据的时间为515s。计算采集到数据的均值是-53和标准差为489.617,可知实验中的时间同步可以满足实际的需求,同步的时间偏差绝大部分处于±500ns内。

由于实验中采用了精密的从时钟的频率的校准,可以进一步地提高时钟同步的精度,可以有效地抑制由温度,湿度等造成的频率的漂移。

使用wireshark对网卡的数据包进行抓取,可以得到网络中的主要是Sync报文和Follow_up报文,主时钟发送这两种报文的周期是1s,并且每隔一段固定的时间从时钟将发送Delay_req报文,主时钟节点对该报文进行回复。由此算出主从时钟节点间网络传输的延时。

在多模块的测试中,从时钟采用了相同的硬件和软件的设计,只是多个模块的IP地址不同,得到了相同的实验结果,实验验证了在同一局域网中多模块的精密的时钟同步。

4 结语

本文提出了一种基于软件时间戳的ptp(精密时间协议)的实现。在没有硬件的支持的硬件时间戳的支持下,也可以实现主从时钟节点间的高精度的时间同步。实验中主从时钟节点间的同步偏移量在2μs内即精度在2μs内,并且主从时钟节点间时钟同步所需要的时间是半分钟左右,而NTP时钟精度虽然可以在几次报文交互中达到秒级,但是需要较长的时间才能将同步的精度达到1ms。NTP时钟同步时间过长不满足工业现场的使用,并且时钟精度只能达到1ms,这也不满足工业现场的要求。

[1]Aavikko P.Network Time Protocol[J].2010.

[2]Eidson J,Kang L.IEEE Standard for a Precision Clock Synchronization Protocol for Networked Measu-rement and ControlSystems[J].2008,11(2):1-269.

[3]谭超,苏超,胡诗俊,等.基于IEEE-1588的高精度时钟同步系统设计[J].电子器件,2016,39(5):1103-1107.TANChao,SUChao,HU Shijun,etal.Design ofHigh Precision Clock Synchronization System Based on IEEE-1588[J].Electronic Devices,2016,39(5):1103-1107.

[4]W.R.Stevens,范建华.TCP/IP详解卷1:协议[M].北京:机械工业出版社,2000.107-141.W.R.Stevens,Fan Jianhua.TCP/IP Detailed Explanations Volume 1:Protocol[M].Beijing:Mechanical Industry Press,2000.107-141

[5]邹崎.IEEE1588协议分析与实现研究[D].武汉:华中科技大学,2009.ZOU Qi.Study on IEEE1588 protocol analysis and implementation[D].Wuhan:Huazhong University of Science and Technology,2009.

[6]谭敏禛.基于IEEE1588协议的时间服务器授时精度研究[D].南京:南京大学,2012.Tan Minzhen.Research on Timing Accuracy of Time Server Based on IEEE1588 Protocol[D].Nanjing:Nanjing University,2012

[7]唐雪松.基于STM32F407的IEEE1588从时钟设计与实现[D].大连:大连理工大学,2014.TANG Xuesong.Design and Realization of IEEE1588 Slave Clock Based on STM32F407[D].Dalian:Dalian University of Technology,2014.

[8]王飞雪,王平,谢昊飞.IEEE1588时间同步协议在Linux下的分析与实现[J].微计算机信息,2006(34):283-285.WANGFeixue,WANGPing,XIEHaofei.Analysisand implementation of IEEE1588 time synchronization protocol in Linux[J].Microcomputer Information,2006(34):283-285.

[9]张文丽.基于IEEE1588的通信设备时间同步系统设计[D].成都:成都理工大学,2010.ZHANG Wenli.Design of Time Synchronization System for Communication Equipment Based on IEEE 1588[D].Chengdu:Chengdu University of Technology,2010.