C波段宽带高速跳频频率源的设计与实现

2018-03-21潘阳卉程龙宝

潘阳卉,程龙宝,杨 振

(上海航天电子技术研究所,上海 201109)

0 引言

跳频通信中载波频率受到伪随机码的控制而进行跳变,与其他通信方式相比,具有更好的保密性和抗干扰性,其中高速跳频抗干扰能力极强,基本认为不可破解,广泛应用于军事通信领域。频率源是跳频通信中的关键部分,在传统频率合成方式中有直接频率合成(DS)、直接数字频率合成(DDS)和间接频率合成(PLL)[1]。直接频率合成法结构复杂,虽然跳频时间和相位噪声等指标都较好,但是往往设计的成品体积较大,难以满足现代通信系统的要求。DDS跳频时间短、频率分辨率高,但输出杂散较多,而PLL输出杂散好、结构简单,但是跳频时间相对较长,因此这2种方案常常被结合使用[2]。乒乓式锁相环结构能够缩短一半的锁相时间,常常被用于高速跳频系统中[3],本研究采用乒乓式锁相结构结合DDS技术,实现了跳频时间小于1 μs高速跳频频率源的设计,并在设计中创新性地采用2路DDS基准时钟来保证整个系统的杂散指标。

1 系统总体设计

DDS[4]跳频时间非常快,基本在ns级,但是其输出频率受到奈奎斯特定理的限制,实际最高频率输出较低,因此本文设计在低频段使用DDS。而PLL法,即利用锁相环电路进行频率合成,结构简单且得到的相位噪声和杂散等指标都较好,本文设计采用锁相环倍频电路将DDS得到的低频段频点进行12倍频得到最终输出频率,因系统需要较高的跳频时间指标,最终采用乒乓式锁相倍频电路,系统总体结构如图1所示。

图1 高速跳频频率源系统组成

系统主要由FPGA控制模块、乒乓式锁相倍频模块和DDS模块组成,设计时首先需要对系统频率进行规划,结合系统杂散和跳频时间等指标选择乒乓式锁相倍频电路的鉴相频率。FPGA控制模块是整个系统的骨架,具有对外通信,对内整机控制的功能。乒乓式倍频锁相环决定了跳频时间等系统的主要指标,选定芯片后需要重点对环路滤波器进行设计。针对DDS的输出杂散严重的问题,对杂散来源进行分析,并结合实测结果设计2路基准时钟为不同频点提供不同的时钟频率来保证杂散指标。

2 系统频率规划

系统输出频率为6.38~7.38 GHz,乒乓式锁相环采用超低相位噪声指标的鉴相器件HMC440QS16G,其最大VCO输入频率为2.8 GHz。

(1)

式中,Int函数表示取整,则环路至少需要外加一个三分频器,本方案选用四分频器HMC365G8。鉴相芯片HMC440QS16G的最大鉴相频率为1 300 MHz(小于DDS最大输出频率1 400 MHz),需调节鉴相芯片的N分频为二分频及以上。因此可选的鉴相频率为797.5~922.5 MHz、532~615 MHz、398.75~461.25 MHz等。

经测试,频段797.5~922.5 MHz的输出杂散比较严重,舍弃。

由于鉴相频率决定了鉴相器的比较速度,鉴相频率越大,电荷泵[5]对环路滤波器的充放电到达预制电压的时间越短,因此跳频时间越短。同时鉴相频率的增大也会优化相位噪声指标[6],最终选择鉴相频率为532~615 MHz。

3 DDS杂散的分析

DDS的杂散抑制度是一个重要的指标[7],其杂散来源主要有相位截断、幅度量化和DAC的非线性3个方面。本方案中DDS杂散对系统杂散指标影响很大,并且系统的快速跳频特性使乒乓式锁相环电路的环路带宽较大,对通过滤波器的DDS杂散抑制性能较差,因此需要在设计时保证一定的DDS杂散输出指标。DDS原理图如图2所示。

图2 DDS原理

3.1 DDS理想输出频谱

理想DDS相当于一个采样—保持电路[4],相位累加器组合波形存储ROM就是一个采样电路,而后面的数模转换电路为保持电路。设DDS输出频率为fo,基准时钟为fc,频率控制字为k,相位累加器字长为N。

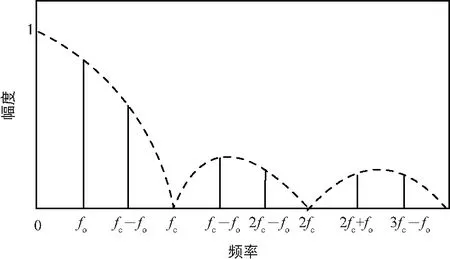

其输出谱线是由无数根位于nfc±fo的点频组成,而且这些频点的幅度满足Sa函数的形状,频率越低幅度越大,如图3所示。fc比fo大得多,幅度最大的杂散也离输出信号较远,因此容易被后级滤波器滤除,本系统中采用的滤波器中心频率572.5 MHz,带宽85 MHz。

图3 理想DDS频谱

3.2 相位截断引起的杂散

前面分析理想DDS的频谱时,假设相位累加器有N位字长,ROM的容量为2N,输出频率fo满足:

(2)

N越大DDS的频率分辨率也就越大,但是当N取得很大的时候,ROM的容量2N必然也会很大,由于成本和体积的限制,不希望ROM的容量过大,因此在实际使用时只取相位累加器的高M位取ROM寻址,此时ROM的容量就只有2M,这就是相位截断。在相位截断后,DDS的频率分辨率不变,因为相位累加器的字长还是N位,当K=1时,完成一次采样需要的时间为2N·Tc。则信号频率为fo=1/(2N·Tc),即DDS频率分辨率依旧为fc/2N,相位截断实际是将采样后的输出波形的可输出点数减少了。

设因相位截断舍去B位,mod表示取模运算,Gcd表示取最大公约数。

b=kmod 2B,

(3)

(4)

(5)

相位截断带来的杂散信号的频谱分量为:

f=lfc±fo±fn,

(6)

设:δ=-l+n·a/λ,则

各频率分量对应的杂散幅度为:

(7)

相位累加器有效寻址位数每增加一位,杂散性能就提高6.02 dB[8]。N=9,B=3,K=3时相位截断带来的杂散如图4所示。

图4 相位截断带来的杂散

3.3 幅度量化引起的杂散

相比之下幅度量化带来的杂散一般比较小,而且幅度量化带来的杂散频率与相位截断和理想DDS输出杂散是重合的,即没有带入新的杂散,只是增大了杂散的幅度[9]。

3.4 DAC的非线性引起的杂散

DAC的非线性带来的杂散分布:

f=αfc+βfo,

(8)

式中,α,β为任意整数。其杂散的幅度特性根据不同DAC的特性会有不同的表现[10]。

本次设计在理论分析的基础上需经过实验得出每个频点的在不同基准频率下杂散电平特性,为每个频点选择合适的基准时钟来使不同频点的强杂散都尽量分布在环路带宽外,2个基准时钟下杂散都无法满足要求的频点舍去。

因此本方案需要2个锁相环为2路DDS产生基准时钟,采用单一的基准时钟输入难以满足杂散要求。

4 乒乓式倍频锁相环的设计

4.1 环路滤波器的设计

本方案采用的鉴相芯片没有电荷泵电路[11],输出电压无法直接驱动VCO,需要采用双端输入有源滤波器。有源环路滤波器的设计,需合理选择滤波器阶数,确定合理的环路带宽和相位余量[12]。

一般工程上都选用3阶及以下的环路滤波器,低阶环路滤波器基本能满足需要,并且使用高阶环路滤波器的锁相环系统难以稳定。本系统采用3阶有源环路滤波器,此时环路滤波器不仅起到将输入电压进行积分的作用[13],还可以滤除鉴相器输出杂波和放大器自激杂波。

设环路的频率特性为H(jw),环路带宽BL定义为:

(9)

环路带宽参数与系统相位噪声和锁定时间等指标有关[14]。环路带宽越大,所需锁定时间越小。系统的相位噪声来源于混入输入信号的热噪声和由环路部件如鉴相器、环路滤波器、VCO引起的环内噪声。环路对输入相位而言是一个低通滤波器[15],输入相位噪声是分布很广的高斯噪声,因此环路带宽越小输入,输入信号的热噪声引起的相位噪声越小。环内噪声主要包括调频白噪声、闪变噪声、叠加噪声,除叠加噪声外其余噪声主要影响带外相噪随环路带宽的增加而减少。

相位余量说明了锁相环系统的稳定程度[16],过小可能会引起锁相环系统震荡,而过大会导致锁定时间增加等问题,一般工程应用中相位余量选用范围45°~48°。

本方案设计的环路滤波器如图5所示,其中环路带宽设为3.5 MHz,相位余量为45°。

图5 环路滤波器

4.2 跳频时间预算

整个系统的最小跳频时间由DDS鉴相频率产生时间、锁相环跳频时间和开关切换时间3部分组成。HMC23 2LP4开关切换时间为6 ns忽略不计。

AD9914采用并行编程模式时,鉴相频率的产生可分为数据写入、等待UPDATA信号和频点产生3个步骤。FPGA将FTW数据传入后,只有UPDATE信号上升沿被SYNC_CLK采集到时DDS才会输出频点。

若基准时钟为3 GHz,

T频点产生≈320·SYNC_CLK≈107 ns。

(10)

UPDATA信号由外部输入,其更新周期不可小于锁相环锁定时间,锁相环锁定时间远大于数据写入时间,所以TDDS唯一决定于产生频点时间,约为107 ns。

锁相环锁定需要的时间为频率牵引时间加上快捕时间,高增益二阶环的频率牵引时间Tp(从初始频差牵引到快捕的边沿需要的时间)[9]为:

(11)

快捕时间,一般在2π/wn量级,较难计算。设ftol为频率锁定误差容限,fjump为频率跳变量,工程上一般用经验公式(12)预估跳频时间:

(12)

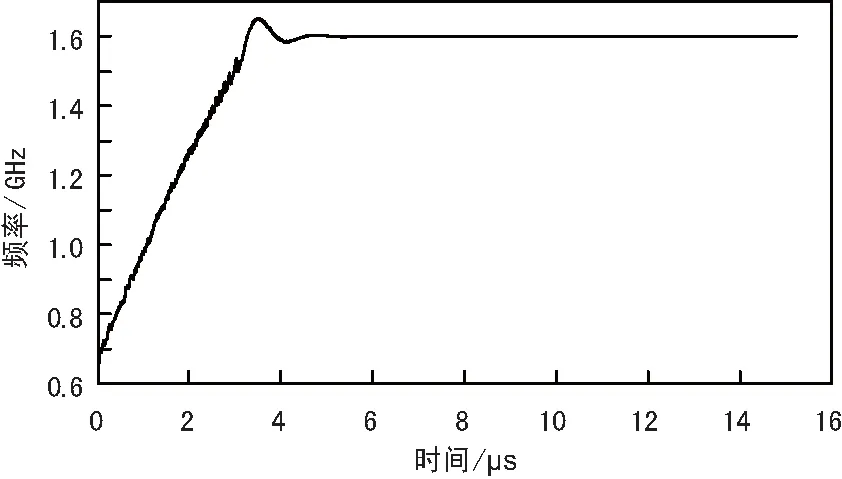

经过ADIsimPLL仿真得到PLL的跳频时间如图6所示。

图6 跳频时间仿真结果

通过仿真可知设计的锁相环的跳频时间的量级,但是与实际的结果还是有较大差距的。因此需要对锁相环路不断地进行调整和测试,得到最佳的结果。

4.3 相位噪声的预算

晶振OXLN202B-S-GT-R@100 MHz的相位噪声[11]为-160 dBc/Hz/10 kHz,HMC440QS16G的噪声基底为-153 dBc/Hz/10 kHz@100 MHz,限制整个频率源的相位噪声,所以DDS基准时钟的相噪为:

PN=PNfloor+20lgN+10lgfPFD=

-123 dBc/Hz/10 kHz。

(13)

经过DDS后相位噪声约优化20lg5,为-137 dBc/Hz/10 kHz。这时输入噪声已经成为主要影响因素,因此经过乒乓式倍频锁相环后的相位噪声为:

-137 dBc/Hz/10 kHz+20lg12=-115 dBc/Hz/10 kHz,

(14)

理论上满足设计要求。

5 系统测试结果

对于杂散指标使用中电集团的AV4036频谱仪进行测量,输出频点6.38 GHz时最大杂散为-63.48 dBc,如图7所示。经测试工作带宽内的所有频点杂散满足-60 dBc。

图7 系统杂散实测结果

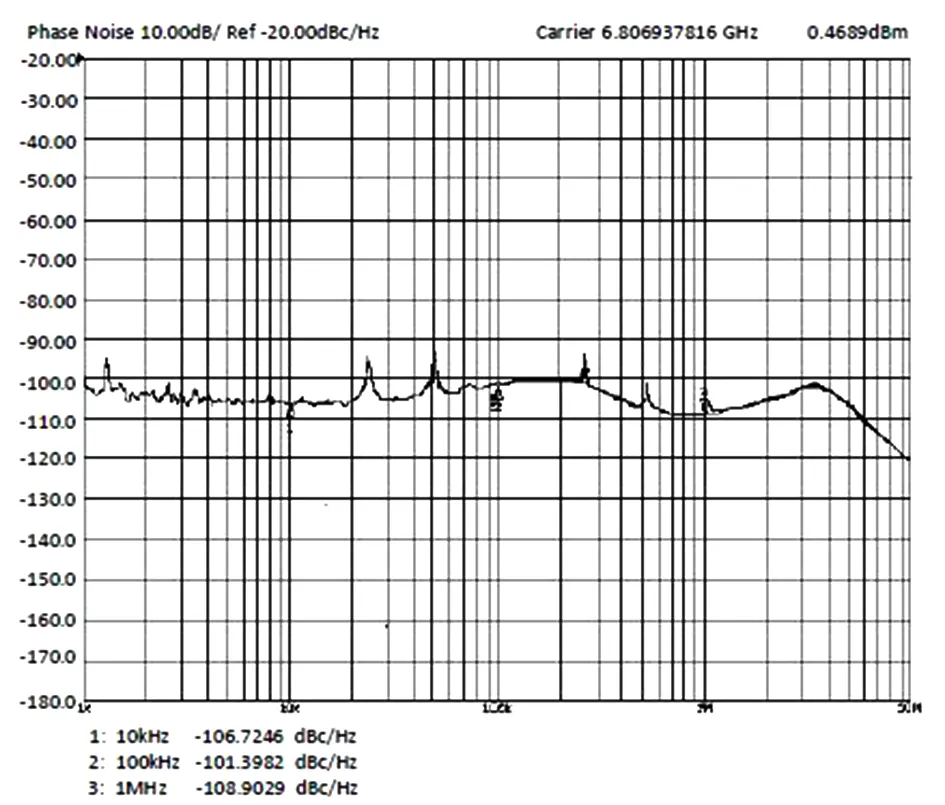

相位噪声指标用Agilent公司的E5052B相噪仪进行测量,在输出频点6.8 GHz时相噪达到-106.725 dBc/Hz/10 kHz,-101.498 dBc/Hz/100 kHz,-108.903 dBc/Hz/ 1 MHz,如图8所示。经测试工作带宽内的所有频点相位噪声满足实际使用需求。

图8 系统相位噪声实测结果

乒乓式锁相倍频电路单环最大跳频时间(6.38~7.38 GHz)为1.76 μs,如图9所示。实测系统最大跳频时间小于1 μs。

图9 单环锁相环跳频时间实测结果

对比国内频率源的研究现状,本文设计的C波段频率源最大的优势在于其跳频时间参数,1 μs的最大跳频时间能满足大部分快跳体制通信系统的要求。

6 结束语

尽可能快的跳频时间是近年来快跳体制通信系统的发展趋势,本文针对此特性设计了一款宽带跳频源。与其他方案相比,本文设计中充分考虑了杂散和跳频时间性能,经测试证明该系统具有跳频时间极小、杂散抑制好、相位噪声低、体积小、控制简单和成本低等优点,可以为跳频通信系统提供高性能的频率源,具有广阔的应用前景。

[1] 克罗帕.频率合成理论.设计与应用[M].北京:国防工业出版社,1979.

[2] SHIVASHANKAR,PALANDE A D,APOORVA A,et al.Development of Agile Frequency Synthesizer[C]∥IEEE International Conference on Recent Trends in Electronics,Information & Communication Technology,IEEE,2016:1943-1945.

[3] 白剑,张伟,孙厚军,等.X波段快速跳频频率综合器的设计与实现[J].微波学报,2012(s2):210-213.

[4] 白居宪.直接数字频率合成[M].西安:西安交通大学出版社,2007.

[5] 张丽,王洪魁,张瑞智.三阶电荷泵锁相环锁定时间的研究[J].固体电子学研究与进展,2004,24(2):196-199.

[6] 远坂俊昭.锁相环 (PLL) 电路设计与应用[M].北京:科学出版社,2006.

[7] 徐守时.信号与系统[M].北京:清华大学出版社,2016.

[8] 张玉兴,彭清泉.相位舍位对DDS 谱分析的影响[J].电子科技大学学报,1997,26(2):137-142.

[9] 孟明.DDS相位杂散抑制技术的研究[D].西安:西安电子科技大学,2012.

[10] KROUPA V F,CIZEK V,STURSA J,et al.Spurious Signals in Direct Digital Frequency Synthesizers Due to the Phase Truncation[J].IEEE Transactions on Ultrasonics Ferroelectrics & Frequency Control,2000,47(5):1166-1172.

[11] 张澄.高频电子电路[M].北京:人民邮电出版社,2006.

[12] 刘颖.锁相环中鉴相器和环路滤波器的设计[D].西安:西安电子科技大学,2013.

[13] 童诗白,华成英.模拟电子技术基础(第3版)[M].北京:高等教育出版社,2001.

[14] 张涛,陈亮.电荷泵锁相环环路滤波器参数设计与分析[J].现代电子技术,2008,31(9):87-90.

[15] 杨士中.锁相技术基础[M].北京:人民邮电出版社,1978.

[16] 李剑宏.13GHz VCO及锁相环设计[D].江苏:东南大学,2016.

[17] 张大鹤.环路滤波器中运放参数对锁相环性能影响分析[J].无线电工程,2016,46(7):64-66.

[18] Bruce Carter.运算放大器权威指南[M].北京:人民邮电出版社,2014.

[19] 白居宪.低噪声频率合成[M].西安:西安交通大学出版社,1995.