基于Schottky管安装电路环境三维模型的W波段全波段三倍频器

2018-02-08窦江玲徐金平徐梦苑

窦江玲 徐金平 徐梦苑

(东南大学毫米波国家重点实验室, 南京 210096)

肖特基二极管精确建模是设计高性能微波毫米波倍频器的重要基础.对于毫米波及THz倍频器的分析设计,近年来国内外很多研究人员投入了大量精力研究包含封装寄生效应的二极管精确模型[1-4].目前较为有效的方法是,对二极管的整体模型进行分区建模,将二极管封装材料部分作为线性区域,肖特基结管芯作为非线性区,分别采用三维电磁仿真软件HFSS和路仿真软件ADS进行建模仿真.HFSS三维电磁模型能够精确模拟封装材料的寄生效应,它与ADS中二极管的非线性SPICE参数模型构成了二极管的精确模型.这种方法所建立的二极管本身模型的精确性已经得到业界的认同,并成功地应用于多种毫米波及THz频段倍频电路的设计.在应用这种模型进行实际倍频电路的设计过程中,通常采用的步骤是:① 采用去嵌入方法提取二极管的输入输出阻抗(参考面一般选在肖特基结所在位置或者芯片两端所在截面);② 根据所提取的二极管阻抗进行外围匹配电路的优化设计.这种方法存在的不足是,由于参考面以外一定范围内的电路不连续性仍然很强,高次模分量很大,故在进行匹配网络设计时,基于参考面以外主模条件的假定会影响仿真设计精度.另外,这种提取方法不便于精确计算安装二极管的微带端线(焊盘)尺寸以及焊盘之间的间距对于等效阻抗的影响,这一点在超宽带倍频器匹配电路设计中也是一个明显的不足.

文献[5]中的W波段全波段Schottky管三倍频器以及文献[6-8]中的倍频器都采用了相同的二极管,它们都存在高频段的输出功率明显下降的问题.分析其原因,一方面是所使用的肖特基二极管本身截止频率有限,导致其高频端非线性性能下降;另一方面,以往的设计中没有专门针对焊盘尺寸等紧邻二极管的安装电路参数进行分析优化,从而对寄生参量效应考虑不足,对倍频器高频端性能影响更为严重.

本文在现有相关研究工作的基础上[5],改进了二极管附近区域等效阻抗参数提取方法,将二极管、焊盘及邻近的腔体空间作为一个子区域进行三维建模分析,深入研究了二极管安装电路环境所引入的附加寄生效应,包括焊盘的长度和宽度、2个端线之间的间距、二极管与微带端线之间导电胶的厚度以及微带电路屏蔽腔体的高度等因素的影响,总结了其变化规律.这些因素与倍频电路匹配网络的优化设计直接相关.通过场路结合的分析设计过程,优化设计了W波段全波段三倍频器的电路尺寸,制作了倍频器的试验样品,实测结果表明,所设计的W波段三倍频器在75~110 GHz的频率范围内的输出功率平坦,无谐振点,实现了优良的宽带特性.

1 肖特基二极管精确模型

DBES105a二极管的整体精确模型由其封装结构三维模型和Schottky结非线性SPICE参数2部分组成.其中,三维封装模型能够模拟二极管封装材料引入的寄生效应,管芯的SPICE参数模型主要模拟二极管的非线性特性.图1给出了DBES105a二极管的电子显微镜照片以及三维封装模型.

(a) 二极管电子显微镜照片 (b) 三维电磁模型图1 DBES105a二极管电子显微镜照片以及三维电磁模型

本课题组对UMS公司的DBES105a二极管的建模方法进行了多年的研究[4-5,9], 并应用到了G波段.图2给出了由场路结合方法所建立的DBES105a二极管三维封装线性区和肖特基结非线性区组合模型示意图,其中A1,A2两个节点分别表示封装无源三维模型中2个Schottky结的阳极连接点,它们是HFSS场仿真和ADS路仿真的结合点.2个肖特基结之间的串联关系已经体现在HFSS的模型中,所以在ADS软件中,二极管的阴极模型接“地”,从而将二极管的非线性部分看成阻抗相同的非线性负载.这个模型充分考虑了二极管的封装寄生效应以及二极管的非线性特性.但是,应用该模型进行W波段等短毫米波宽带倍频器的设计还需要考虑很多因素,如安置二极管的微带端线(焊盘)尺寸和间距等.

2 W波段三倍频器电路设计

2.1 三倍频器电路方案

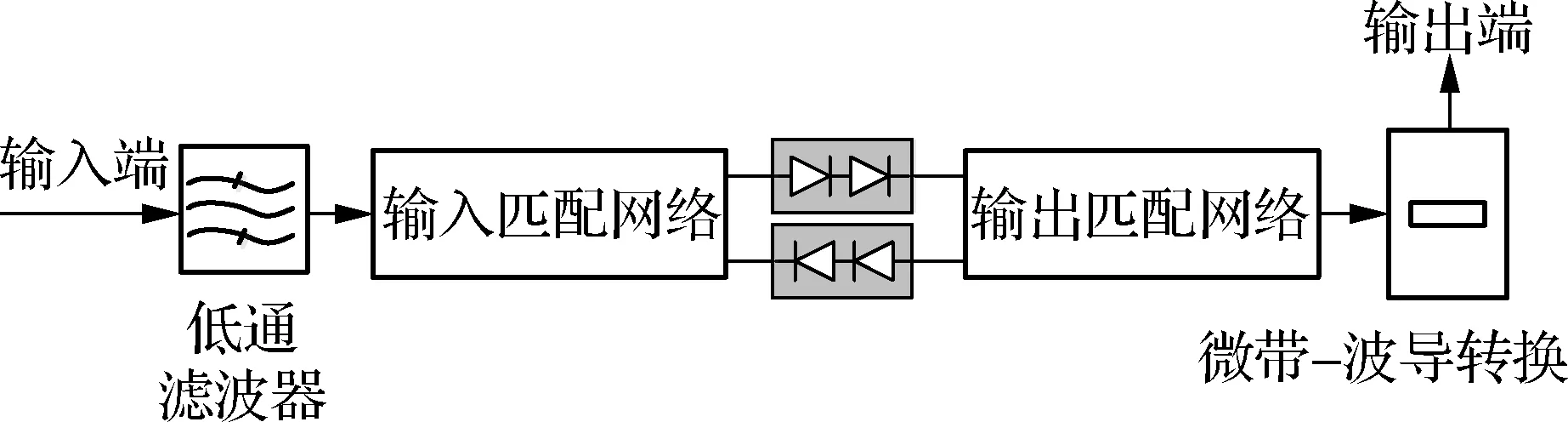

图3是本文所采用的W波段三倍频器的基本构成框图.倍频器的输出端采用标准的WR10波导微带探针结构,它对输入信号频率分量截止,起到了高通滤波器的作用.与鳍线过渡相比,可以较大程度地改善100 GHz以上高频端的插入损耗.输入端采用了高低阻抗线低通滤波器,在通过低频激励信号的同时,能抑制高次谐波信号通过,避免三次谐波反射回输入端.

图3 W波段三倍频器基本构成框图

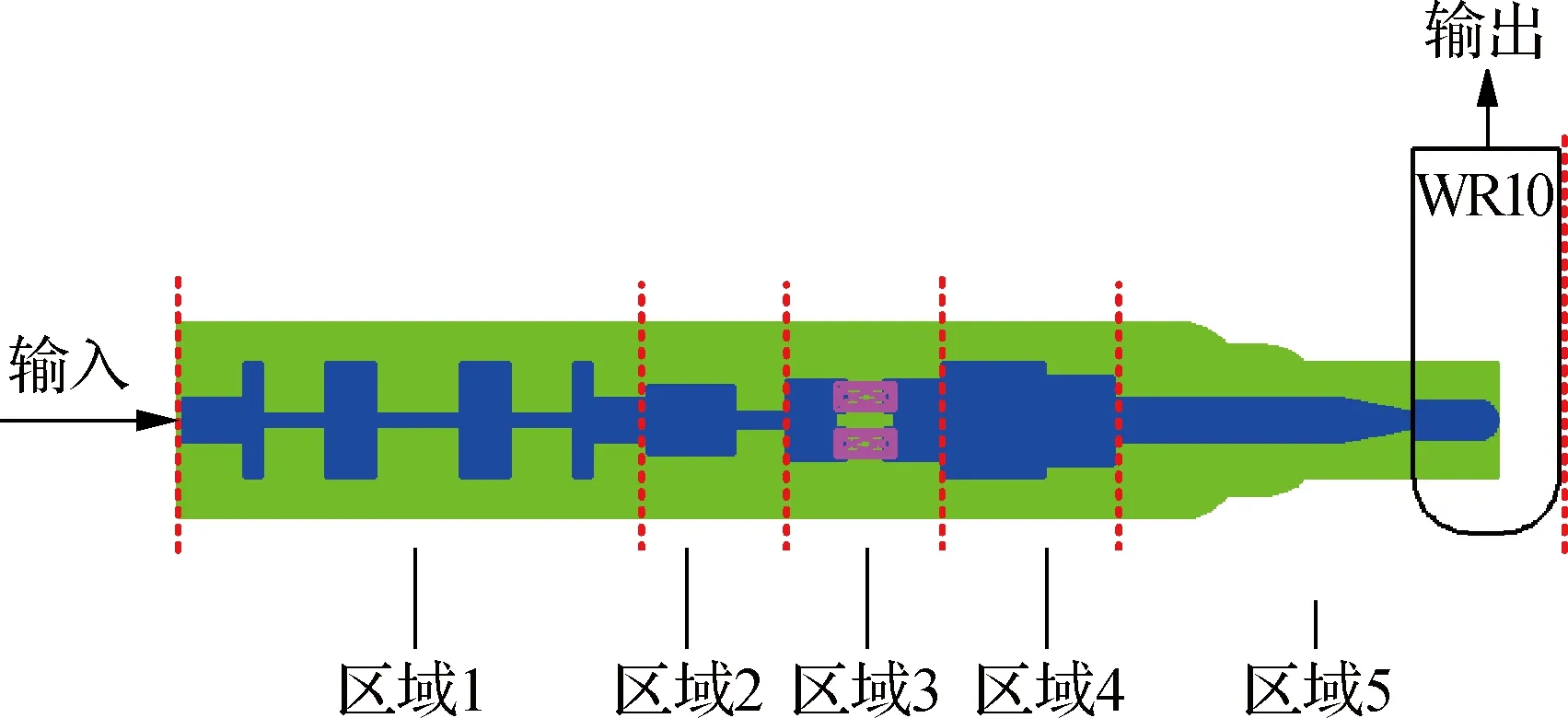

2.2 W波段三倍频器分区建模

将倍频器电路分为5个相对独立的子区域,如图4所示.区域1为输入低通滤波器;区域2为输入匹配网络;区域3为二极管、焊盘及邻近腔体区域;区域4为输出匹配网络;区域5为微带-探针-波导过渡输出区域.首先对区域1和区域5分别进行建模分析与优化,这2个子区域都是常规的线性电路区域,其仿真设计方法已经非常成熟.本文重点研究区域3,把它作为一个独立的整体,分析其输入输出阻抗,重点研究内部焊盘尺寸、间距等参数对超宽带范围内频响特性影响的规律,为设计整个倍频器电路的匹配网络做准备.

图4 W波段三倍频器区域划分示意图

2.3 二极管安装区域宽带阻抗特性分析

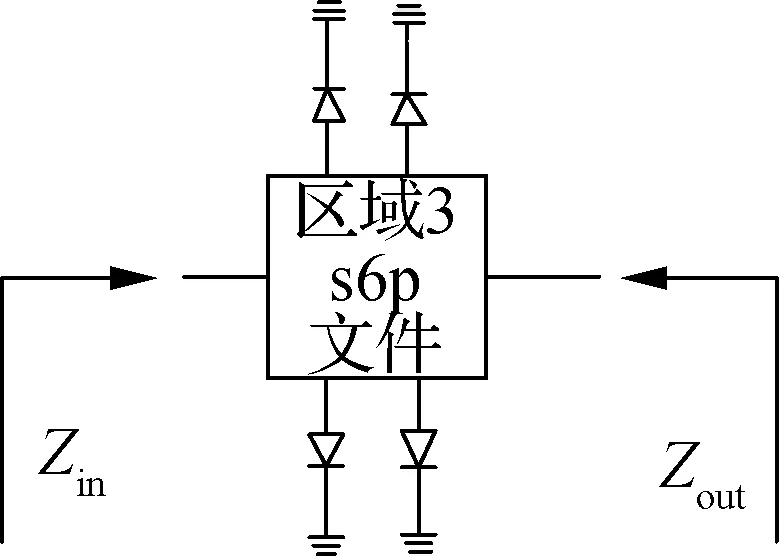

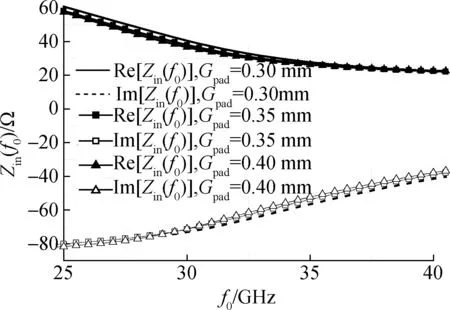

图5给出了用HFSS建立的区域3三维仿真模型及其等效网络示意图.图5(a)中,Lpad,Wpad,Gpad分别为微带端线的长度、宽度以及间距,Ddiode为2个二极管边缘之间的距离.用HFSS软件仿真计算区域3电磁模型,然后将得到的s6p文件导入到ADS软件中(见图5(b)),计算区域3的输入输出阻抗.考虑到计算量的问题,本文选取了几个典型的离散值,图6~图9给出了这几个变量对区域3输入输出阻抗的影响曲线.

(a) 三维模型

(b) S参数包及阻抗定义

由图6~图9可见,为了减小二极管阻抗在宽带范围内的变化幅度,就要求安装二极管的微带端线宽度大、长度短以及间距大,同时反向并联二极管对的间距尺寸要小,但是这些尺寸也受到多方面因素的限制,如为了减少高次模的产生,腔体的宽度不能太宽,这就限制了微带端线的宽度;为了保证足够的安装空间,微带端线的长度不能太小;同时,微带端线的间距要小于二极管的长度.另外为了便于匹配网络的实现,二极管所在区域的输入输出阻抗的虚部不能太大.综合考虑后,选取Lpad=0.5 mm,Wpad=0.7 mm,Gpad=0.4 mm,Ddiode=0.17 mm.在这个尺寸下区域3的输入输出阻抗在输入基波和三次谐波下变化较为平缓,保证了宽带匹配的可实现性.在基破中心频率f0=30.8 GHz处,区域3的输入阻抗为Zf0=36.3-j69.9 Ω,在3f0=92.4 GHz频点处,区域3的输出阻抗为Z3f0=34.0+j5.4 Ω.

(a) 输入阻抗

(b) 输出阻抗

(a) 输入阻抗

(b) 输出阻抗

(a) 输入阻抗

(b) 输出阻抗

2.4 三倍频器完整电路的优化设计

为了快速提取匹配电路尺寸的初值,应用HFSS三维仿真软件,将计算得到的区域1中低通滤波器的网络参数和区域5中微带-探针-波导过渡段的s2p参数,以及二极管区域的s6p文件导入到ADS中,建立用于计算高低阻抗线匹配网络初始值的电路模型(见图10),并利用此模型提取了由高低阻抗线构成的输入输出匹配网络的参数初值.

(a) 输入阻抗

(b) 输出阻抗

图10 ADS中匹配网络初值计算模型

由于分区仿真方法并未考虑分区域模型之间的耦合效应以及仿真不连续性等因素,为了获取精确的匹配网络尺寸,还需要进一步在HFSS软件中建立倍频器的全尺寸模型,计算出整个电路中无源部分所对应的s6p参数,并将其导入到ADS中进行谐波平衡分析,计算模型如图11(a)所示.基于该模型,以减小倍频损耗为目标,计算得出最优的匹配网络尺寸.

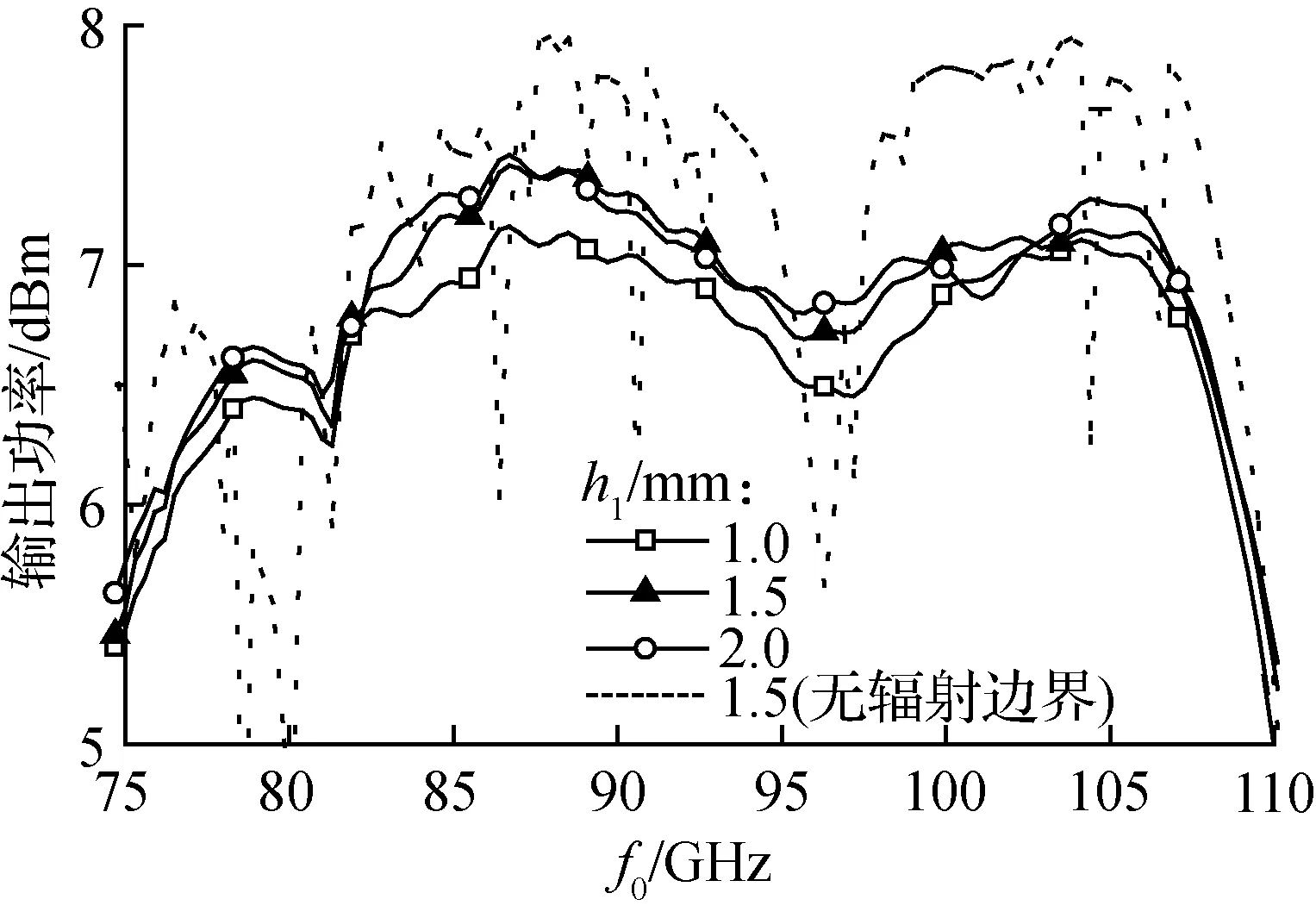

图11(b)为倍频器腔体2个高度尺寸h1和h2示意图,本文分别考察了这2个参数对倍频输出功率的影响.图12给出了以h1为参变量的倍频器输出功率在W波段全频段内的频响特性曲线,其中存在多个谐振吸收点的曲线所对应顶部为理想导体边界,其余3条曲线对应顶部带有吸波材料的吸收边界. 可见,在腔体上方增加吸波材料可以有效地抑制腔体的寄生谐振.腔体高度h1经优化后约为2 mm.为了减少波导微带转换中的高次模,经优化,h2取0.8 mm.

(a) 基于全尺寸模型S参数包的倍频电路ADS计算模型

(b) W波段三倍频器腔体高度示意图

图12 W波段三倍频器的输出功率频响应特性仿真

本文还分析了不同导电胶粘接层厚度倍频器的输出功率的变化情况.仿真结果表明,当导电胶粘贴层厚度较厚时,低频端输出功率较高,但是在105 GHz以上的高频端输出功率较低,因此,在二极管安装工艺中,需要控制导电胶层的用量,既要保证二极管与微带电路优良的电气连接,又要尽量减小导电胶的厚度,从而改善高频端的性能.

3 W波段三倍频器实验

基于上面的设计方案,加工了W波段三倍频器实验样品,如图13所示.腔体选用硬铝材料,采用上下Half传统的腔体加工方式;采用厚度为0.127 mm 的Rogers5880基片;二极管以反向并联的方式采用进口导电胶安装在焊盘(即微带端线)上.完成倍频器的装配后,对倍频器进行测试,采用Ka波段的全波段功放作为W波段三倍频器的激励源,当Ka波段功放的功率约为20 dBm时,利用W8486A功率探头和N1911A功率计测试了三倍频器的输出功率.在75~110 GHz频率范围内,输出功率测试结果如图14所示.由图可见,在整个W频段内,倍频器输出功率典型值为5 dBm,变化幅度小于±1.25 dB.实测结果和仿真结果变化趋势的一致性较好,两者之间的最大差值小于 2.45 dB.

图13 上下腔体打开的W波段三倍频器实物照片

图14 W波段三倍频器输出功率测试值结果及仿真结果

图15给出了本文和文献[5]的变频损耗测试结果的对比曲线.在频率高端102~110 GHz范围内,文献[5]和本文中的倍频器倍频损耗变化幅度分别为4和1.2 dB,由此可见,本文采用改进方法优化设计的倍频器在频率高端变频损耗平坦度有显著改善.

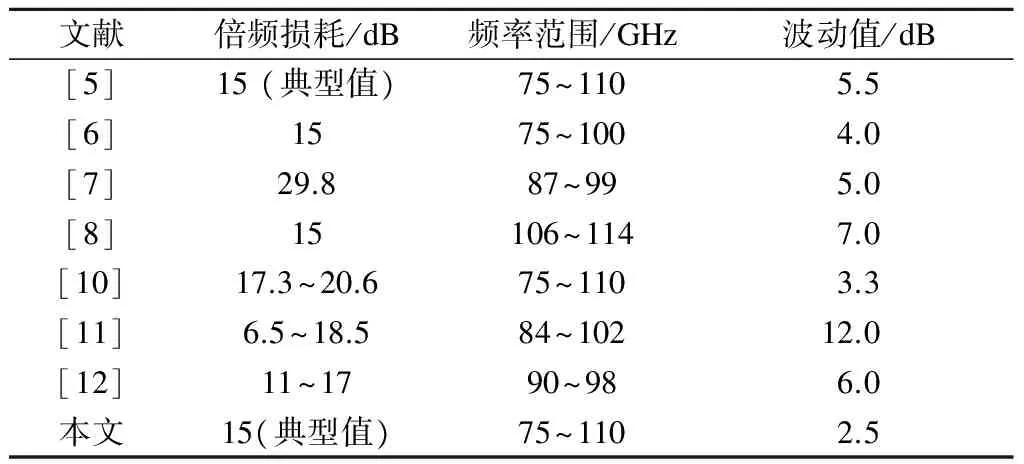

为了更清楚地反映本文设计方法在改善W波段全频带范围内输出功率平坦度方面的有效性,表2给出了本文设计的倍频器和国内外文献报道的倍频损耗测试结果的对比.可见,采用本文的改进方法所设计的W波段倍频器的倍频损耗平坦度得到明显改善.

图15 倍频器变频损耗测试结果对比曲线

文献倍频损耗/dB频率范围/GHz波动值/dB[5]15(典型值)75~1105.5[6]1575~1004.0[7]29.887~995.0[8]15106~1147.0[10]17.3~20.675~1103.3[11]6.5~18.584~10212.0[12]11~1790~986.0本文15(典型值)75~1102.5

4 结论

1) 本文深入分析了二极管实际工作环境对二极管输入输出阻抗的影响规律,以减小输入输出阻抗在工作频段内波动为目标,优化出安装二极管的微带端线尺寸.

2) 采用场路结合的联合仿真方法,充分考虑各个子区域之间的相互耦合,详细分析了腔体的高度对最终输出功率的影响,以宽带内的输出功率的平坦度为目标,优化设计出倍频器的匹配网络尺寸以及腔体的高度, 最终设计出W波段全波段三倍频器.

3) 实验样品测试结果表明,在20 dBm左右的Ka波段激励功率下,所设计的三倍频器在整个W波段的输出功率典型值为5 dBm,功率波动小于±1.25 dBm,由此验证了二极管模型的准确性以及宽带匹配网络设计方法的有效性,为研制W波段低成本、高性能、超宽带固态倍频源提供了有效的技术途径.

)

[1] 陈振华. 短毫米波宽带倍频源理论与技术研究[D].南京:东南大学信息科学与工程学院,2014.

[2] Alderman B, Sanghera H, Thomas B, et al. Integrated Schottky structures for applications above 100 GHz [C]//EuropeanMicrowaveIntegratedCircuitConference. Amsterdam, the Netherlands,2008: 202-205.

[3] Bishop W L, Meiburg E R, Mattauch R J, et al. A micron-thickness, planar Schottky diode chip for terahertz applications with theoretical minimum parasitic capacitance [C]//IEEEInternationalDigestonMicrowaveSymposium. Dallas, USA,1990: 1305-1308.

[4] Yao C, Xu J, Ying K. Design of a D-band frequency doubler using GaAs Schottky barrier diodes [C]//InternationalConferenceonMicrowaveandMillimeterWaveTechnology. Nanjing, China, 2008:1193-1195.

[5] Chen Z, Xu J. Design of a W-band frequency tripler for broadband operation based on a modified equivalent circuit model of GaAs Schottky varistor diode [J].JournalofInfrared,Millimeter,andTerahertzWaves, 2012,34(1): 28-41. DOI:10.1007/s10762-012-9943-5.

[6] 于伟华, 王雅薇, 佟飞, 等. 毫米波倍频器的设计与研制[J]. 北京理工大学学报, 2016, 36(9): 951-955. DOI:10.15918/j.tbit1001-0645.2016.09.013.

Yu Weihua, Wang Yawei, Tong Fei, et al. Design and fabrication of millimeter-wave frequency triplers[J].TransactionsofBeijingInstituteofTechnology, 2016,36(9): 951-955. DOI:10.15918/j.tbit1001-0645.2016.09.013.(in Chinese)

[7] 毛伟. 毫米波三倍频器的研究[D].成都:电子科技大学物理电子学院,2010.

[8] Zhang B, Fan Y, Zhang S X, et al. 110 GHz high performanced varistor tripler [C]//InternationalWorkshoponMicrowaveandMillimeterWaveCircuitsandSystemTechnology.Chengdu, China,2012: 1-2.

[9] Dou J, Jiang S, Xu J, et al. Design of a G-band frequency doubler based on a pair of parallelly mounted dual-diode chips [C]//Asia-PacificMicrowaveConference. Nanjing, China, 2015:1-3. DOI:10.1109/apmc.2015.7413571.

[10] Morgan M, Weinreb S. A full waveguide band MMIC tripler for 75—110 GHz [C]//IEEEMTT-SInternationalMicrowaveSymposiumDigest. Phoenix, USA,2001: 103-106.

[11] Han K, Liu T, He H, A W band balanced tripler MMIC with excellent harmonic suppression and low conversion loss [C]//IEEEInternationalWirelessSymposium. Shenzhen, China,2015: 1-4.

[12] Vukusic J, Bryllert T, Olsen A O, et al. High power W-band monolithically integrated tripler [C]//InternationalConferenceonInfrared,Millimeter,andTerahertzWaves. Busan, Korean, 2009: 1-2. DOI:10.1109/icimw.2009.5324703.