一种基于共享RAM的嵌入式多处理器通信方案*

2018-01-19聂同攀

聂同攀,谭 特,周 密

(1.中航工业第一飞机设计研究院,陕西 西安 710089;2.北京航空航天大学 计算机学院,北京 100191;3.北京中航瑞博航空电子技术有限公司,北京 100085)

在嵌入式系统设计中,有时需要两个或多个嵌入式微处理器芯片之间交互信息。例如,在分布式传感器网络中,用于传感器数据采集的处理器需要将数据传送给用于数据集成﹑处理的主控制器。

目前,大多数微处理器都采用串行接口通信,如以太网[1]﹑RS232[2]﹑电力线[3]等。串行通信有数据线少﹑实现简单﹑十分适合远距离通信等优点。然而,串行通信方式也有诸多不利,其中一个主要的不足是串行通信协议普遍都引入了数据包头部。在某些小数据包频繁发送的应用中,数据包头部的大小甚至大于真实负载数据的大小,大大降低了带宽利用率。在基于IEEE1451.3[4]标准的智能变送器系统中,出于扩展IO引脚等原因,每个变送器网络接口模块(TNIM)连接多个变送器通道模块(TCM)。如果TNIM和各个TCM之间通过串行总线通信,则TNIM每请求读取某个TCM上的某个传感器的数据,首先需要在总线广播TCM通道号和传感器号。事实上,绝大多数传感器数据都可以通过一位﹑两位或四位表示,而TCM通道号和传感器号需要数位表示。这样真实数据负载的带宽利用率将很低。

如果TNIM和各个TCM共享同一RAM芯片,各个TCM的微处理器将采集到的传感器数据写到特定的内存单元,那么TNIM只需要读取特定的内存单元,即可获取特定TCM上的特定传感器数据。这样就避免了TNIM发送TCM通道号和传感器号,从而提高了真实数据负载的带宽利用率。

文献[5]提出了一种基于PCI总线的共享内存多处理器通信方案。然而,由于PCI总线不支持TAS(Test And Set)原子操作,所以其自旋锁的实现并不理想。

基于上述问题,本文提出一种支持多个微处理器通过共享RAM进行通信的硬件接口设计方案。该接口设计方案采用一种基于菊花链的仲裁方式解决总线竞争问题。

1 总体设计

如引言中的分析及描述,本设计实现多个CPU通过共享的RAM通信。为实现这样的通信机制,参与通信的每个CPU都应当和用作通信介质的共享RAM相连接。

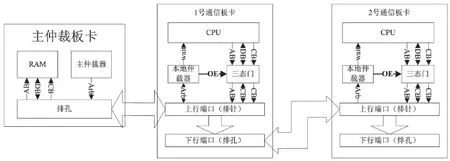

一种可行的连接方案是将多个板卡通过“上行端口”和“下行端口”堆叠在一起。如图1所示,主仲裁板卡的排孔向通信板卡提供连接到RAM芯片的接口。各个通信板卡除了拥有用于将本地CPU信号线和RAM信号线相连的“上行端口”外,还有一个“下行端口”。该端口可向下级板卡提供连接到RAM信号线的接口。图1绘制了两个通信板卡通过共享主仲裁器中的RAM芯片来相互通信。事实上,2号通信板卡的下行端口还可以堆叠更多的通信板卡。这样的“堆叠设计”可以使系统有较好的硬件可扩展性。

图1 总体设计

可以看出,上述方案中,各个参与通信的CPU实际上共享同一组连接到RAM芯片的总线。因此,必须提供仲裁机制,以防总线争用的发生。

本设计应用一种集中式的仲裁方式。如图1所示,系统中有且只有一块“主仲裁器卡”。这块板卡上有用于多CPU通信的RAM芯片,以及用于解决总线竞争的“主仲裁器”。系统中其余的板卡为参与通信的“通信板卡”。每一块通信板卡上除了有参与通信的本地CPU外,还有用于抢占共享总线使用权的“本地仲裁器”。本地仲裁器根据主仲裁器和上一级板卡提供的仲裁信号,决定本地CPU是否可以占用总线。如果仲裁信号有效,本地仲裁器将使能本地CPU和上行端口之间的三态门。这样本地CPU的地址﹑数据和控制总线就和用于通信的共享RAM的相应信号线建立了连接。

由于多个处理器共享总线,当本地仲裁器未取得总线使用权时,应当通知本地CPU进行等待(即在访存指令的执行期间内加入若干个等待周期)。因此,如图1所示,本地仲裁器有连接到本地CPU的wait信号线。

本地仲裁器内部提供若干个寄存器,本地CPU可以读写这些寄存器来配置或控制本地仲裁器。这些寄存器包括计时器以及其他用于实现特殊功能的寄存器。

2 仲裁机制

为防止因多处理器共享总线而带来的总线竞争问题,本设计必须引入一种仲裁机制。而基于“菊花链”的仲裁机制十分适合本系统的多级堆叠结构。

菊花链仲裁是一种集中式仲裁机制,核心思想是通过由多个板卡级联形成的“仲裁链”逐级传播总线授权信号。处在仲裁链第一级板卡的本地仲裁器拥有最高仲裁优先级。该最高优先级的本地仲裁器根据本地CPU是否有访问共享RAM的事务来决定是否占用总线,并为下级通信板卡生成仲裁信号(Arb1信号)。其余的下级n号板卡的本地仲裁器根据上一级仲裁器输入的仲裁信号判断总线是否已经被前级高优先级的通信板卡占用,并根据该输入信号﹑本地CPU是否有访存请求,为更下级n+1号板卡生成输入仲裁信号(Arbn信号)。当某块通信板卡获得总线使用权后,它通过连接到主仲裁器的hold信号,向主控制器指示总线是否仍被占用。

图2显示了本方案对这种仲裁机制的具体实现。主仲裁器向每一个本地仲裁器广播state信号和CurrNum信号。每个本地仲裁器接收state和CurrNum信号,并逐级连接用于仲裁的Arb信号和Hold信号。这样的设计使得系统可以十分方便地添加或删除通信板卡。

图2 总线仲裁机制

主仲裁器广播的state信号标识总线状态,该信号的值仅由主仲裁器改变。总线有两种状态:事务状态和仲裁状态。在每一个时钟周期,总线处于且仅处于一种状态。在仲裁状态对应的时钟周期内,各个通信板卡抢占总线使用权;而在事务状态对应的时钟周期内,获得总线使用权的板卡执行访问共享RAM的操作。

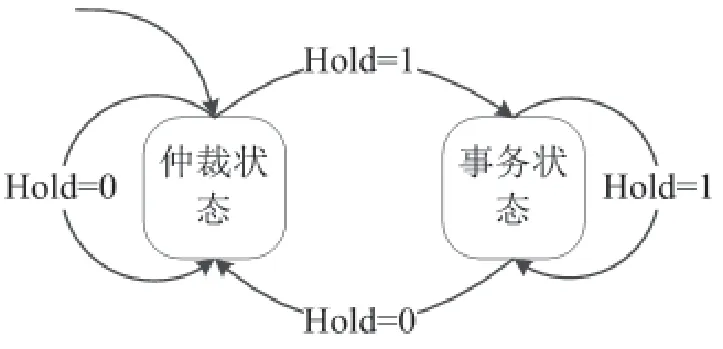

图3反映了总线状态的迁移过程。板卡上电或手动复位后,总线处于仲裁状态。Hold信号是唯一影响总线状态迁移的信号,由各个本地仲裁器输出的Hold信号组合而成。在仲裁状态对应的时钟周期内,如果某个板卡有待处理的访问RAM的操作并获得了总线使用权,则将Hold信号置为有效。该板卡的访存事务完成后,将Hold置为无效。

图3 总线状态迁移

主仲裁器除了广播用于标识总线状态的State信号,还广播CurrNum信号。该信号是为了实现循环优先级。如果系统中各个板卡的优先级是固定的,即处于仲裁链上端的板卡总是优先于下端的板卡访问共享的RAM,那么有可能出现下游板卡的数据率很低的情况。为了实现各个CPU可以公平访问RAM,应当在系统运行过程中动态改变各个板卡的优先级。

本设计采用“优先级轮转”的策略动态调整各个板卡的优先级,即每个通信板卡轮流获得最高优先级。主仲裁器在仲裁状态对应的时钟周期内,通过CurrNum信号标识当前最高优先级板卡的编号。与CurrNum对应的板卡将作为仲裁链的第一级板卡,之后主仲裁器对CurrNum加1并取模。这样就实现了最高优先级在各个通信板卡之间的轮转。

3 仿真验证及分析

利用VHDL语言实现本设计中的主总裁器和本地仲裁器,并构造了一个简单的CPU,用于模拟真实嵌入式微处理器STM32f207芯片在访问外接PSRAM时的时序。在此基础上,构造了四个CPU共享RAM的仿真测试系统,并用xilinx的仿真工具ISim软件进行了仿真验证。

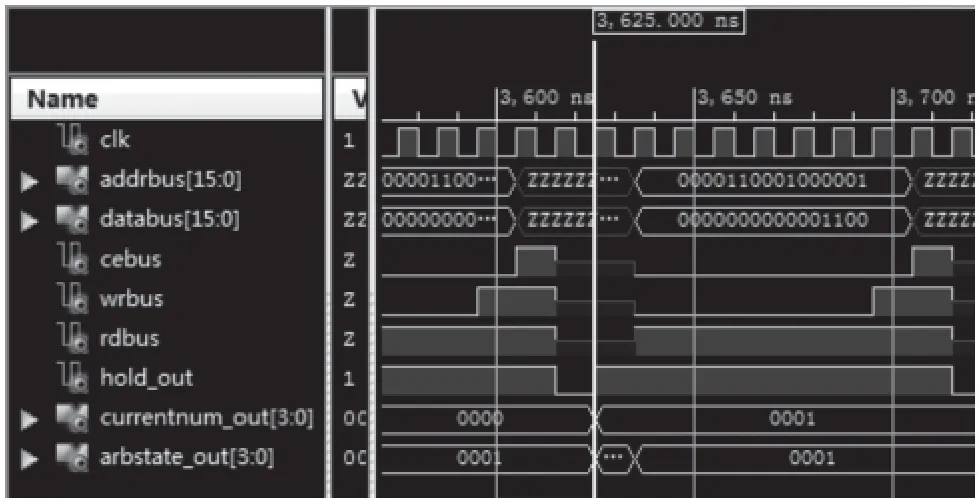

图4是仲裁算法的行为仿真结果,时钟周期为10 ns。在从第3 625 ns(如波形图部分的长竖线所示)开始的时钟周期开始处,由于标识总线是否仍被占用的hold_out信号无效,所以标识总线状态的arbstate_out信号迁移到了0x0000,即仲裁状态。同时,用于广播最高优先级编号的currentnum_out信号加1,表示此时1号板卡的优先级最高。

图4 仿真结果

在该处于仲裁状态的时钟周期末,由于hold_out信号有效,所以arbstate_out又被迁移到了0x0001,即事务状态。同时,与具体访存事务相关的数据﹑地址和控制信号出现在了相关总线上。

第3 705 ns时,访存事务结束。在第3 715 ns的时钟上升沿处,hold_out信号变为无效。至此,总线仲裁算法的逻辑得到验证。

从时序图可以看出,仲裁算法导致了两个时钟周期的浪费。因此,总线的利用率U为:其中a表示一次完整的访存事务所占的时钟周期数。

本通信方案的吞吐量和主仲裁器的时钟频率内存芯片的访存延迟有关。如果主仲裁器的始终频率为fclk,且内存芯片的访存时间折合a个主仲裁器周期,那么最大吞吐量为:

当主仲裁器的始终周期为50 MHz,且内存芯片的访存时间折合3个时钟周期时,系统的最大吞吐量为10 MB。

4 结 语

本文为解决嵌入式系统多处理器通信中串行通信协议开销较大的问题,提出了一种基于“共享RAM”的通信方案。这种通信方案几乎不引入任何协议开销,从而有效解决了串行通信传输低效的问题。此外,本文提出了一种“多级堆叠”的板卡连接结构,可使单个通信板卡十分方便地连接到通信系统,从而使得系统有很好的可扩展性。在“多级堆叠”的基础上,本文提出了一种基于“菊花链”的总线仲裁机制,解决了由多块板卡同时访问共享RAM时的冲突问题。未来,将进一步优化此方案,并将此方案应用到实际工程。

[1] 杨紫胜.嵌入式多功能接口转换器的设计与实现[J].福建电脑,2008,24(06):154-155.

YANG Zi-sheng.The Design and Implementation of Embedded Multi-purpose Connection Switch[J].FuJian Computer,2008,24(06):154-155.

[2] 于海昕.嵌入式多功能Hub的设计与实现[D].厦门:厦门大学,2007.

YU Hai-xin.The Design and Implementation of Embedded Multifunction Hub[D].Xiamen:Xiamen University,2007.

[3] 钟悠.基于VxWorks的嵌入式通信接口设备的设计与实现[D].西安:西北工业大学,2007.

ZHONG You.The Design and Implementation of Embedded Communication Interface Device Base on VxWorks[D].Xi’an:Northwestern Polytechnical University,2007.

[4] The Institute of Electrical and Electronics Engineers.Standard for a Smart Transducer Interface for Sensors and Actuators-Transducer to Microprocessor Communication Protocols and Transducer Electronic Data Sheet (TEDS)Formats for Distributed Multi-drop Systems,IEEE STD 1451.3-2003,IEEE Instrumentation and Measurement Society,TC-9[S].2004-03-31.

[5] 徐恪,吴建平,喻中超等.一种基于总线的多处理器共享内存机制[J].小型微型计算机系统,2003,24(03):321-326.

XU Ke,WU Jian-ping,YU Zhong-chao,et al.Multiprocessor Shared Memory Mechanism based on Bus[J].Small Microcomputer System,2003,24(03):321-326.