基于电源线载波的单线通讯系统设计

2018-01-18张成,聂飞,王远,印姗

张 成,聂 飞,王 远,印 姗

(中国工程物理研究院 总体工程研究所,绵阳 621999)

大型的试验系统对连接线数量有着严格的限定,小数据量的信号传输若使用专用的通信线缆,不仅会造成连线资源的紧张,还会增加系统的连线复杂度。在此类特殊场合中,传统的通信协议难以满足系统设计的要求,基于电源线载波的单线通讯成为一种可行的解决方案[1-5]。

针对以上需求,本文设计了一种基于FPGA的通信系统,通过MOSFET对电源进行调制,通过光电耦合器对调制信号进行解调,在20 m距离内实现了波特率可达10 kb/s的通信传输。该系统具有硬件结构简单,通信距离远,通信速率快等优点,目前已成功应用于某飞行器的飞行试验数据采集平台。

1 总体结构设计

该方案的总体设计如图1所示,系统由发送单元和接收单元构成。

图1 总体设计框图Fig.1 Overall design block diagram

发送单元主要由电源模块、FPGA、调制模块构成,通过FPGA控制调制模块实现对电源信号的调制;接收单元主要由电源模块、FPGA和解调器组成,通过解调器和FPGA实现电源信号的解调;二者仅通过电源线和地线相连。

当进行通信时,发送模块首先将数字信号调制到电源信号中,生成载波电源信号后再发往信号接收单元。接收单元解调载波电源信号从而得到电源信号和数字信号,最终实现供电和通信。二者通过异步串行通信方式进行信号的发送与接收。

2 硬件电路设计

2.1 信号发送单元设计

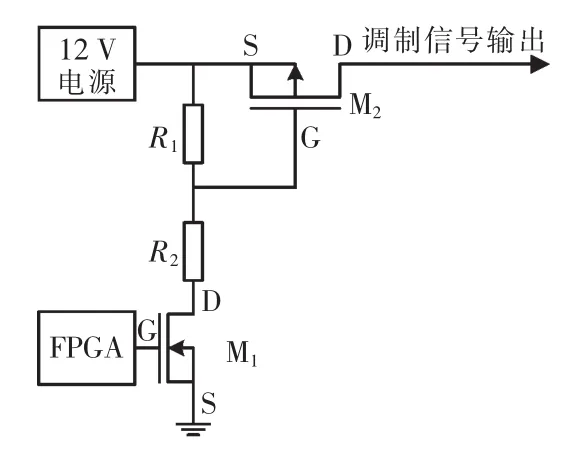

信号发送单元的硬件设计如图2所示。该方案主要由 FPGA、N-MOSFET(M1)、P-MOSFET(M2)、12 V电源以及R1和R2(阻值为4∶1)构成的分压电路组成。将12 V电源作为供电电源;将M2作为电源的通断开关;将FPGA作为M1的G极控制端。

图2 信号发送单元组成Fig.2 Block diagram of signal sending unit

当FPGA发送低电平时,M1关闭,此时 M2关闭,发送单元输出的电压为0 V;当发送高电平时,M1导通,此时M2上的G极电压为9.6V,S极为12 V,M2导通,电源调制电源输出的电压为12 V。

综上所述,FPGA输出的控制信号为低时,发送单元输出的电压为0 V;为高时,输出的电压为12 V。因此,只要M1和M2的开启/关闭时间能够小于FPGA控制信号的上升/下降时间,发送单元就可以输出频率和占空比均与FPGA控制信号完全相同的电源信号,即将通信信号调制到电源信号中,产生载波电源信号。而在信号接收单元将载波信号进行解调,就能够完成信号的发送和接收。

2.2 信号接收单元设计

信号接收单元的硬件设计如图3所示。该单元主要由电源转换模块、储能电容、解调电路和FPGA构成。电源转换模块转换12 V电源满足接收单元的供电需求;储能电容则保证发送单元在发送低电平时接收单元能够正常工作;限流二极管隔离储能电容和解调电路之间电气连接,防止储能电容供电时干扰解调电路工作;解调电路主要由光电耦合器实现,完成通信信号与电源信号的分离;FPGA则完成信号的识别与接收。

图3 信号接收单元组成Fig.3 Block diagram of signal receiving unit

载波电源信号进入到接收单元后被分为2路,一路通过储能电容进入电源转换模块完成电平转换,另一路通过限流电路进入光电耦合器,完成电平转换后进入FPGA,二者之间通过限流二极管进行隔离。当电源信号为高(12 V)时,储能电容充电,FPGA 接收信号“1”;当信号为低(0 V)时,储能电容放电保证整个电路正常工作,由于限流二极管的隔离,光耦输入为0 V,FPGA接收信号“0”。

综上,当光电耦合器的上升/下降时间小于通信信号的上升/下降时间时,接收单元的FPGA就能够准确接收到来自发送单元的通信信号,通过设定的逻辑对信号进行解析从而完成信号的接收。

此外,载波电源信号中零电平的持续时间不能过长,否则一旦钽电容中存储的能量耗尽,信号分离单元就会被迫关机。

3 信号的调制与解调

信号发送单元与接收单元之间采用异步串行通信模式,通信频率设为10 kHz。在发送单元,异步串行通信信号的调制过程如图4所示。

图4 异步串行信号的生成格式Fig.4 Generation format of asynchronous serial signals

当发送单元发送异步串行通信信号时,先发起始信号表征发送开始,其后发送标志位‘0’,16位数据(MSB格式),标志位‘0’。为了防止待发送的信号中连续出现过多的‘0’,导致接收单元断电关机,FPGA每发送完16位数据信号后,会再发送16位的数据信号“FFFF”给接收单元“充电”。当所有的数据信号发送完毕,发送停止位,信号传输结束。

在信号接收单元,光耦分离出的调制信号的解调流程如图5所示。系统首先将输入的数字信号引入同步器中,实现串行信号与接收时钟信号同步,再采用另一个频率为接收时钟4倍的时钟信号对同步信号进行连续采样,校验串行信号的起始位,防止FPGA误将干扰信号当作起始信号。当起始信号确认无误后,系统将按照发送单元的格式接收数据信号完成信号的接收。

图5 信号的解调流程Fig.5 Signal demodulation flow chart

4 试验结果

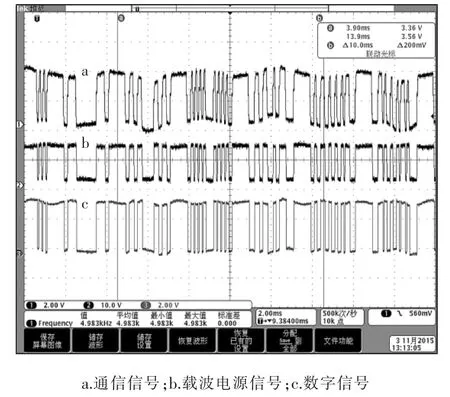

按照所述的方案分别实现信号发送单元和接收单元,搭建电源线载波实验平台以验证该方案的正确性。本次试验中,信号发送单元与接收单元之间采用20 m长的2芯同轴电缆连接,10 kHz的通信频率,共发送10个16位数据信号到信号接收单元。在试验过程中,使用数字示波器同时捕捉电源调制单元的FPGA发出的通信信号、P-MOSFET发出的载波电源信号以及光电耦合器转换后输出的数字信号。

测试获取波形的显示界面如图6所示,其中,波形a为FPGA发出的通信信号、b为P沟道MOS管发出的载波电源信号、c为光电耦合器转换后输出的数字信号。

图6 试验获取的信号波形Fig.6 Waveform of the signal obtained

5 结语

针对利用电源线进行信号传输的特殊要求,设计了一种基于电源线载波的单线通讯系统。该系统以FPGA,MOSFET和高速光耦为核心器件,不采用专用电力载波芯片完成电源线通信。试验结果表明,该系统的可实现性强,成本低,信号传输距离远,电路供电稳定可靠,满足了设计需求。

[1]刘恒光,姜秀杰,熊蔚明,等.基于直流电源的电力线载波通信耦合电路设计[J].电子设计工程,2016,24(14):186-189.

[2]Bertuol S,et al.Numerical assessment of propagation channel characteristics for future application of power line communication in aircraft[C]//10th Int Symp on EMC,2011:506-511.

[3]Dégardin V,et al.Theoretical approach to the feasibility of powerline communication in aircrafts[J].IEEE Trans VT,2013,62(3):1362-1366.

[4]赵益攀.基于电源线载波的防火排烟阀智能执行器研究 [D].杭州:浙江大学,2016.

[5]孙康岭,杨兆伟.基于电源线载波的有缆管道机器人通信系统[J].制造业自动化,2012,34(6):97-99.