一种宽带频谱分析结构优化与FPGA实现

2018-01-17,,

, ,

(1.武汉大学 电子信息学院,湖北 武汉 430072;2.武汉纺织大学 电子与电气工程学院,湖北 武汉 430200 )

在现代雷达、遥测与电子侦察领域中,宽带频谱分析是不可或缺的一部分.在这些高实时性应用场景中,接收机的采集和处理速度是衡量系统性能的重要指标.信道化接收机因具有高灵敏度、大动态范围、并行处理和大量信息实时处理等优点而得到广泛应用.常见的信道化接收机基于低通滤波器组结构,各个信道并行处理,互相并联,但每个信道本身的抽取滤波等计算过程仍旧是串行的,无法满足更高的实时性要求.Fields等将多相滤波技术应用于信道化接收机中[1-2],相比于低通滤波器结构的信道化接收机在实时性上得到了改善.

该方案以实际科研项目中对1.7~2.7 GHz的宽频带高实时性频谱分析需求为背景,采用了多相滤波结构提高宽带频谱分析的实时性,并从资源消耗的角度对此多相滤波结构与多路并行载波的产生进行了结构优化与资源平衡,在基于FPGA的硬件平台上实现了2.621 44 GSPS采样速率的信道化接收机与宽带频谱分析的设计,具有很强的可行性和工程实践性.

1 硬件平台与系统方案设计

硬件平台分为采集和传输两部分,宽带采集板将A/D转换器采集到的宽带信号进行信道化处理和多相抽取滤波,处理后的数据缓存到DDR3,通过千兆网板传给上位机进行频谱拼接与测量显示.该方案整体结构框图如图1所示.

图1 系统整体结构框图Fig.1 Overall structure diagram of the system

FPGA采用Xilinx公司的Kintex-7系列XC7K325t.XC7K325t拥有203 800个LUT,840个DSP48E1s,合理利用DSP48E1s资源能极大缓解逻辑资源的压力.同时,内部还有890个RAMB18和445个RAMB36,存储资源非常丰富,可以满足并行载波、多相分解与信道化算法的需求.A/D转换器选用TI公司的ADC083000.ADC083000是一款单通道、低功耗和高性能的CMOS模数转换器件,采样精度8 bit,最高采样率能达到3.4 GSPS.ADC083000有一个1∶4多路分解器将采集到的数据分解为4路LVDS数据,输出速率降为采样率的1/4,数据可以设置成单沿和双沿有效,理论有效位数能达到7.0 bit,因此,这款A/D满足1.7~2.7 GHz频谱分析带宽需求.

该设计需求的瞬时检测带宽为1 000 MHz,考虑到硬件平台的资源情况,划分5个子信道,每个子信道分析带宽为200 MHz,输入数据频率范围为1.7~2.7 GHz,则5个子信道的中心频率如表1所示.

表1子信道划分方案与各子信道中心频率

Table 1 Sub-channel classification scheme and center frequency of different sub-channels GHz

由带通采样定理,前端A/D的采样率不能低于带宽的两倍,即2 GSPS.为了减少盲区,将每个子信道检测的频谱范围增加到320 MHz,每个子信道做32 768点FFT运算,频率分辨力为10 kHz,子信道频谱拼接时仅取各子信道中心频率左右100 MHz,将5个子信道拼接后即可得到全频带频谱.基于此,将A/D转换器采样率定为2.621 44 GSPS.

2 多相滤波与并行载波设计方法

在宽带信号的信道化接收和频谱分析应用场景中,对系统的实时性要求很高.传统的内插与抽取滤波器是串行计算的结构,时间开销较大,实时性上无法得到保证.基于FPGA并行计算的特点[3],对FIR抽取滤波器采取多相分解进行结构优化,用面积换取速度,有效提升了系统的实时性[4-5].

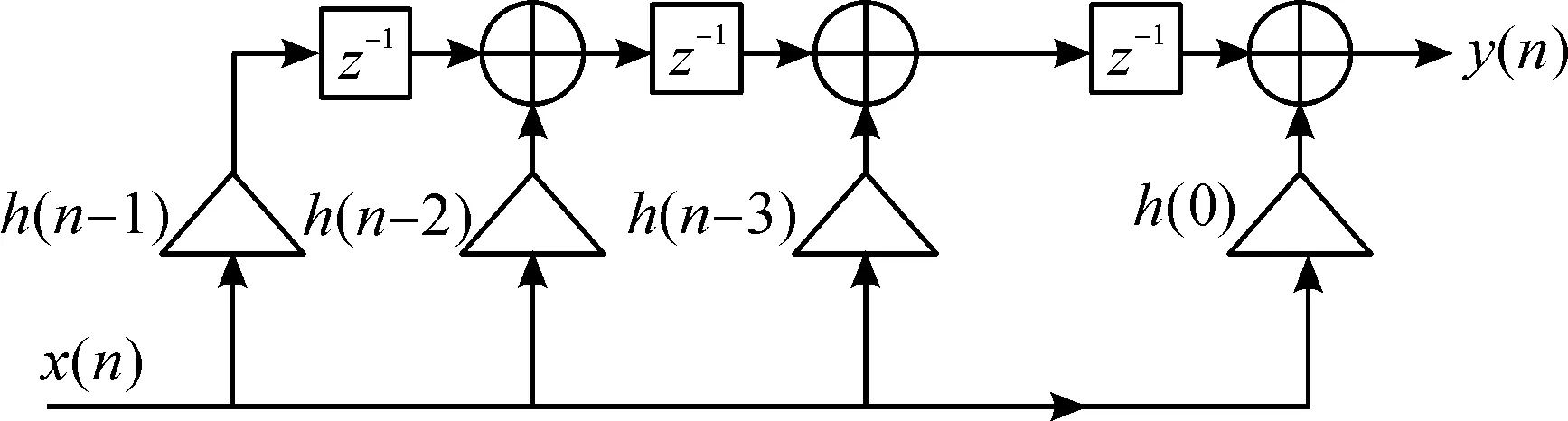

FIR滤波器的直接二型转置结构[6-7]如图2所示.

图2 FIR直接二型转置结构Fig.2 Transpose structure of FIR direct two-shape

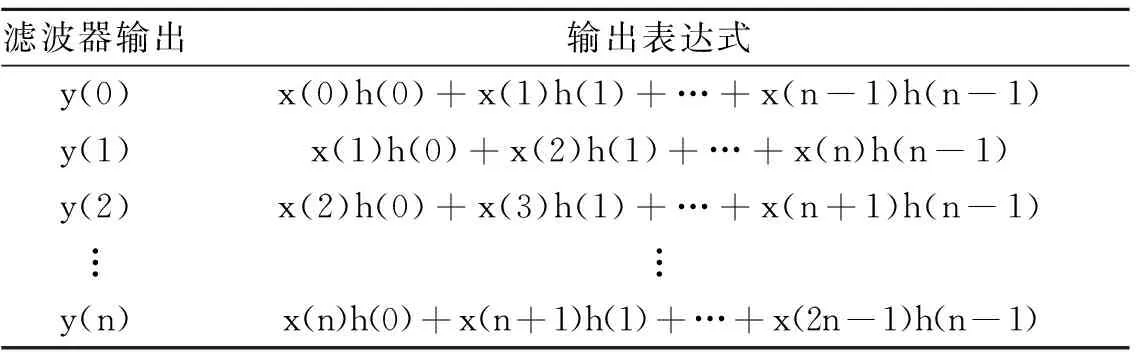

对此结构进行多相分解,实现结构优化.设FIR滤波器系数为h(0),h(1),h(2),…,h(n),输入滤波器的数据为x(0),x(1),x(2),…,x(n),对于输出y(0),y(1),y(2),…,y(n)的结果可以用表2表示.

表2 FIR滤波器输出结果Table 2 Output results of FIR filter

设FIR滤波器阶数为15,将其系数分成4组,第1组为h(0),h(4),h(8),h(12),第2组为h(1),h(5),h(9),h(13),第3组为h(2),h(6),h(10),h(14),第4组为h(3),h(7),h(11),h(15).将高速A/D采集的数据并行分为4路,第1路数据为x(0),x(4),x(8),…,x(4n-4);第2路数据为x(1),x(5),x(9),…,x(4n-3);第3路数据为x(2),x(6),x(10),…,x(4n-2);第4路数据为x(3),x(7),x(11),…,x(4n-1);可得到y(0)表达式为

y(0)=x(0)h(0)+x(4)h(4)+…+x(12)h(12)+

x(1)h(1)+x(5)h(5)+…+x(13)h(13)+

x(2)h(2)+x(6)h(6)+…+x(14)h(14)+

x(3)h(3)+x(7)h(7)+…+x(15)h(15)

(1)

y(1)表达式为

y(1)=x(1)h(0)+x(5)h(4)+…+x(13)h(12)+

x(2)h(1)+x(6)h(5)+…+x(14)h(13)+

x(3)h(2)+x(7)h(6)+…+x(15)h(14)+

x(4)h(3)+x(8)h(7)+…+x(16)h(15)

(2)

令H(0)=h(0)+h(4)+h(8)+h(12),H(1)=h(1)+h(5)+h(9)+h(13),H(2)=h(2)+h(6)+h(10)+h(14),H(3)=h(3)+h(7)+h(11)+h(15),X(0)=x(0)+x(4)+x(8)+x(12),X(1)=x(1)+x(5)+x(9)+x(13),X(n)=x(n)+x(n+4)+x(n+8)+x(n+12),定义一种运算“**”,使得

X(n)**H(n)=x(n)h(n)+x(n+4)h(n+4)+

x(n+8)h(n+8)+x(n+12)h(n+12)

(3)

则y(0)可表示为

y(0)=X(0)**H(0)+X(1)**H(1)+

X(2)**H(2)+X(3)**H(3)

(4)

相应地,y(1)可表示为

y(1)=X(1)**H(0)+X(2)**H(1)+

X(3)**H(2)+X(4)**H(3)

(5)

式中X(4)为X(0)延时一个时钟周期得到.由此可得到多相滤波后y(n)的输出表达式为

y(n)=X(n)**H(0)+X(n+1)**H(1)+

X(n+2)**H(2)+X(n+3)**H(3)

(6)

四路多相分解FIR结构相较于串行FIR结构虽然在资源消耗上增加了2倍,但其较高的运算效率是串行FIR结构所无法实现的.将多相滤波FIR结构推广到N阶,将FIR滤波器分为M组,设Q=N/M为整数,则其冲激响应为

(7)

在数字信号处理中,为了减少后续数据处理的压力,使得系统能以较低速率的时钟正常运行,最大程度降低硬件时序设计难度,通常对数据进行下采样以降低数据率[8-9].在FPGA中,先将A/D采集到的信号进行正交下变频,分别得到I路和Q路信号.I和Q路信号的多相滤波结构相同,均采用两级滤波结构,第一级FIR滤波器的采样率与截止频率之比为8∶1,下抽4倍后经过第二级FIR滤波器,第二级滤波器采样率与截止频率之比为4∶1,下抽2倍,得到单个子信道的多相抽取滤波后的数据.多相抽取滤波结构如图3所示.

图3 多相抽取滤波结构Fig.3 Structure of polyphase decimation filter

第一级FIR滤波器阶数为31,在FPGA中将其系数进行归一化并量化为10 bit,如表3所示.

表3 第一级FIR量化后系数值Table 3 Coefficient value of the first-layer FIR quantization

在满足设计精度要求的前提下,在进行FPGA设计时将计算过程中的部分系数值的乘法运算通过加法或者移位的方式来替代,节约了大量的乘法器资源.

FPGA中多路并行载波的产生方法通常有波表查询法和相位旋转法2种[10].波表查询法主要消耗FPGA内部存储资源,而相位旋转法会消耗大量乘法器和加法器,即占用FPGA内部的逻辑资源和DSP资源.考虑到XC7K325t的FPGA内部拥有非常充裕的存储资源,因此选择采用波表查询法来生成多路并行载波.波表采用双口ROM结构,存储深度为2 048,同相和正交载波同时产生,每个载波均分为16路.并行载波生成在FPGA内的逻辑框图如图4所示.

图4 FPGA内波表查询法并行载波生成逻辑框图Fig.4 Logic diagram generated by parallel carrier through wavetable inquiry method in FPGA

需要生成的载波包括1.8,2.0,2.2,2.4,2.6 GHz这5个载波,通过改变每个载波访问波表的指针偏移量来实现.实测波表查询法生成载波动态范围能达到60 dB,满足设计需求.

3 测试结果

在Matlab和Simulink中对该宽带子信道频谱分析和拼接算法进行联合仿真.

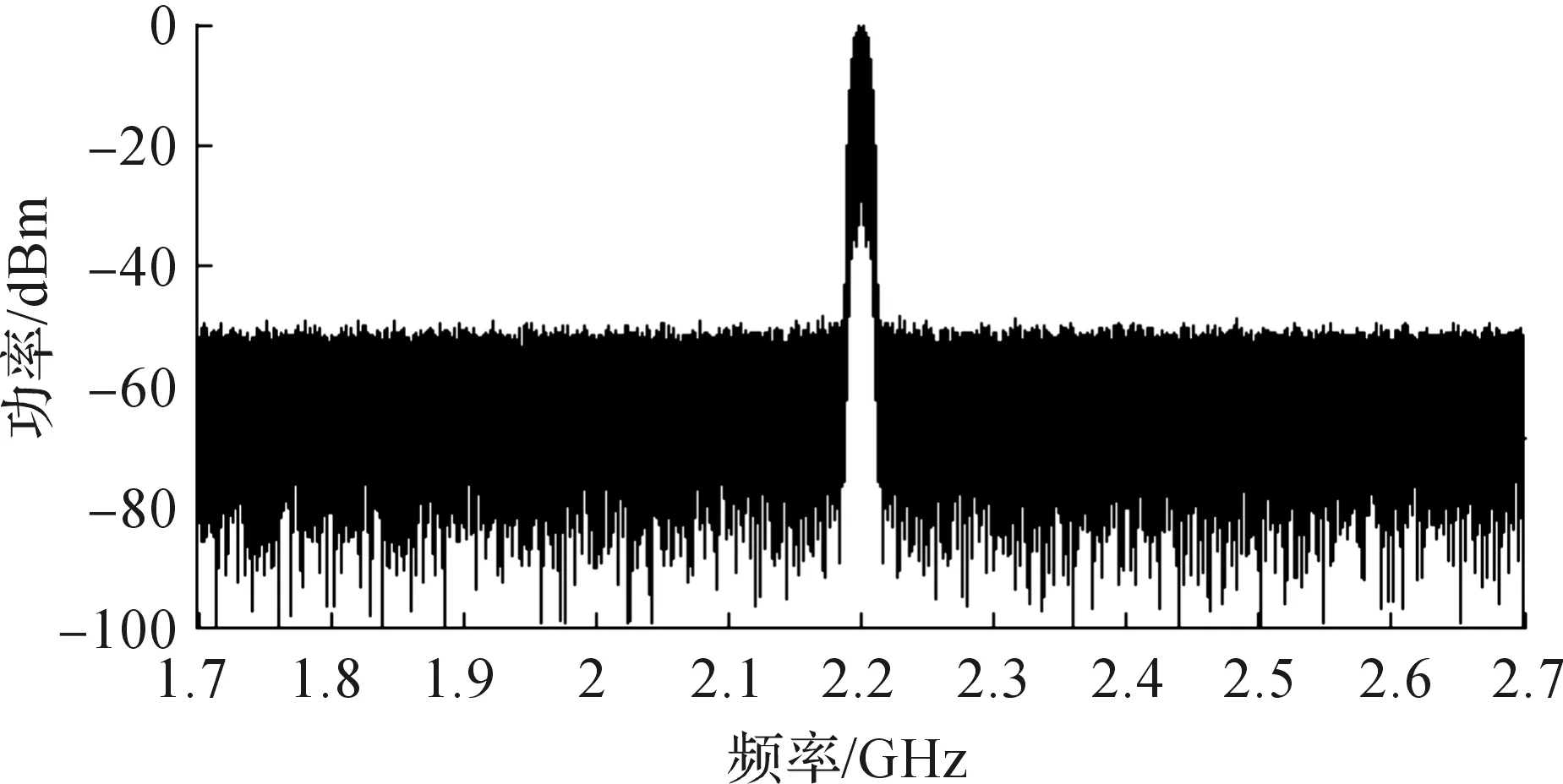

测试信号为20 MHz带宽的QPSK调制信号,载波频率为2.2 GHz,经过一个比特信噪比为50 dB的AWGN信道传输到宽带频谱分析模块.宽带频谱分析模块将信号按照表1所示方案分成5个子信道,每个子信道均分成I和Q两路进行正交下变频与多相抽取滤波,将抽取滤波后的I和Q两路数据重新组合成复数,进行32 768点的FFT运算,由此得到5个子信道的频谱数据.求其幅度谱,并对幅值进行归一化,将5个子信道的频谱拼接成1.7~2.7 GHz的全分析频带频谱,即完成了宽带频谱分析的过程.频谱拼接结果如图5所示.

图5 频谱拼接结果Fig.5 Spectrum matching results

在频谱拼接过程中,先对中心频率分别为1.8,2.0,2.2,2.4,2.6 GHz的5个子信道多项抽取滤波后的数据做FFT运算,每个子信道各自频谱如图6所示.

图6 5个子信道各自频谱Fig.6 Respective frequency spectrum of five sub-channels

将算法移植到硬件平台中,将实测的1.7~2.7 GHz全频带的信号频谱显示如图7所示.

图7 频谱拼接实测结果Fig.7 Measured results of spectrum splicing

测试条件与流程为:用矢量信号源产生带宽20 MHz、载波频率为2.2 GHz的QPSK中频调制信号,经由A/D转换器采集到FPGA中,经过子信道划分、正交下变频与多相抽取滤波,将5个子信道抽取滤波后的I和Q路数据通过千兆以太网[11]传输到基于MFC开发的配套上位机中,上位机进行后续的FFT运算和频谱拼接及显示.

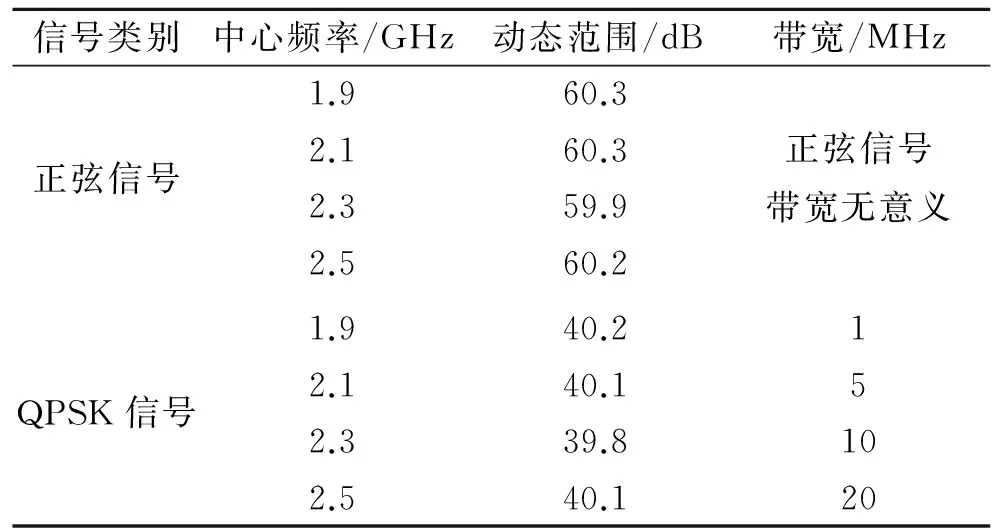

接着由矢量信号源输出4组正弦波与4组带宽不同的QPSK信号对宽带频谱分析系统的动态范围进行了测试.受限于测试信号的功率、实际A/D动态范围和FPGA量化误差等因素,实测动态范围相比仿真有所下降,但仍满足高实时性需求下的宽带频谱分析需求,测试结果如表4所示.

表4 硬件频谱拼接测试数据Table 4 Test data of hardware spectrum splicing

FPGA资源消耗情况如表5所示.

表5 FPGA资源消耗统计Table 5 Statistics of FPGA resource consumption

4 结 论

针对实时性要求较高的应用场景下的宽带频谱分析技术进行了研究,设计了一个1.7~2.7 GHz的宽带频谱分析系统,为实现较快的运算效率,对抽取滤波器进行了多相分解,并对多相分解的结构和信道化并行载波的生成结构进行了优化,以减少和平衡资源消耗,在FPGA中对算法进行了设计实现,最后将实测性能与仿真结果进行了对比,证明了该方案的可行性与有效性.该方案在频谱监测和电子侦察等领域有着广泛的应用,已应用于工程实践与科研项目中.

[1] FIELDS T W, SHARPIN D L, TSUI J B. Digital channelized IFM receiver[J]. IEEE microwave theory and technology symposium digest,1994,3(5):1667-1670.

[2] ZAHIRNIAK D R, SHARPIN D L, FIELDS T W. A hardware-efficient,multirate,digital channelized receiver architecture[J]. IEEE transaction on aerospace and electronic systems,1998,34(1):137-151.

[3] GORDANA J D. Multirate systems: design and applications[J]. Journal on communications,2008,78(1):25-33.

[4] LEKIC P N, MICIC A D, RISTIC J D, et al. Design of second order digital fir full-band differentiators using weighting coefficients[J]. Iete journal of research,2014,56(1):22-29.

[5] 吕影影,徐强,崔志超.一种基于多相滤波的高速信号处理算法[J].雷达科学与技术,2014(2):161-165.

[6] 曲少波.基于并行流水线结构的可重配FIR滤波器的FPGA实现[J].现代电子技术,2007,30(7):75-77.

[7] KIM P S, LEE M E. A new FIR filter for state estimation and its application[J]. Journal of computer science and technology,2007,22(5):779-784.

[8] 陈婷.基于FPGA的高速并行多速率信号处理技术[D].西安:西安电子科技大学,2013.

[9] MALVAR H S. Modulated QMF filter banks with perfect reconstruction[J]. Electronics letters,1990,26(13):906-907.

[10] 张青林,罗义军,陈淑珍,等.基于相位旋转法的NCO设计与实现[J].系统工程与电子技术,2010,32(5):908-911.

[11] 孟珞珈.基于FPGA的千兆网通信协议栈实现技术研究[D].成都:电子科技大学,2014.