一种超低相位噪声频率合成源方案设计

2018-01-08王李飞张宁彭子健薛沛祥李维亮

王李飞 张宁 彭子健 薛沛祥 李维亮

一种超低相位噪声频率合成源方案设计

王李飞1,2张宁1,2彭子健1,2薛沛祥1,2李维亮1,2

频率合成源是射频发生和频谱分析中最重要的组成之一,评价合成源性能指标的是输出信号的相位噪声、杂散、频率分辨率和频率切换时间.本文通过分析传统锁相环原理,提出一种通用的超低相位噪声合成源设计方案(带宽100MHz以内).在锁相环基础上,通过引入直接数字合成(Direct digital synthesizer,DDS)混频鉴相技术,使得到的射频信号理论值达到0.1mHz的频率分辨率,同时将带内相位噪声指标优化17dB以上.新方案同时兼顾了杂散和频率切换时间指标,保障合成源的输出信号稳定可靠,使其在自动测试领域拥有广阔的应用前景.

频率合成源,锁相环,极高分辨率,超低相位噪声

随着芯片集成度的提高以及测量仪器的发展,对频率合成源的频段、相位噪声、频率切换时间、频率分辨率等指标的要求不断提高.在目前的高性能频率合成源研发中,通常引入低相噪的窄带源与锁相环中压控振荡器的反馈信号进行混频鉴相优化输出信号的相位噪声指标,其中的窄带源信号采用锁相环的方式获得[1].这种方法虽然可以一定程度的优化输出信号的相位噪声指标,但是因为锁相环路自身引入的数字噪声,导致整体方案的近端相噪优化幅度并不大,而且无法从根本上获得超低的相位噪声指标.

目前的频率合成源信号通常会采用直接数字合成(Direct digital synthesizer,DDS)方式获得超高的频率分辨率指标,主要是将DDS合成的超高分辨率的低频信号作为参考信号,直接送入锁相环路中,通过R分频后进行环路鉴相[2].因为DDS自身的量化误差和DAC(Digital to analog converter)误差会导致杂散信号过多,同时近端相噪指标相对于参考晶振指标会严重恶化,导致锁相环路的参考信号相噪指标恶化,最终的输出信号相噪指标变差.所以该方案无法兼顾信号的相位噪声指标.

本文介绍的合成源方案,环路中通过引入DDS和超低相噪的点频源进行混频鉴相,在兼顾环路锁相时间和输出信号杂散等指标的前提下,获得一种通用的超低相位噪声和超高频率分辨率的高频合成源信号,使得最终的输出信号相噪指标相对于传统方案优化17dB,同时频率分辨率理论值达0.1mHz.

1 锁相环介绍及相位噪声分析

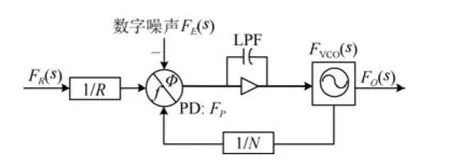

锁相环电路结构如图1所示,是一个相位负反馈的自动控制系统,其能够跟踪相位,实现输出信号与输入信号的相位同步.锁相环电路主要由参考分频器(R)、鉴相器(Phasedetector,PD)、环路滤波器(Loop fi lter,LPF)、压控振荡器(Voltagecontrolled oscillator,VCO)和反馈分频器(N)组成.电路中将VCO的N分频信号与参考信号的R分频信号鉴相,通过鉴相器输出与两种信号相位移成正比的误差信号.LPF将相位误差转换为电压信号,送至VCO调谐输出频率,当两鉴相信号频率相同时,鉴相器输出稳定的相位差,环路锁定[3−5].

图1 锁相环电路结构框图Fig.1 PLL circuit structure

环路中的噪声来源主要有三个,分别为参考源FR,因数字鉴相器中电流脉冲和时间抖动引起的数字噪声FE和VCO引入噪声FVCO[6−8].

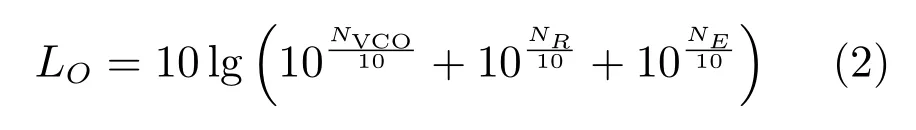

最终输出信号FO(s)的闭环传递函数见式(1),式中G(s)为环路的开环传递函数,N为VCO反馈分频比,R为参考信号鉴相分频比,KD为数字噪声FE的鉴相增益[5].

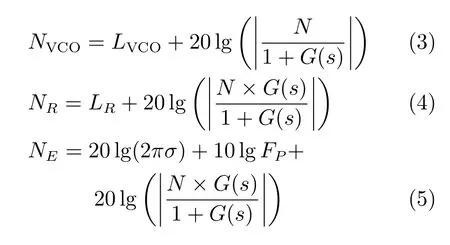

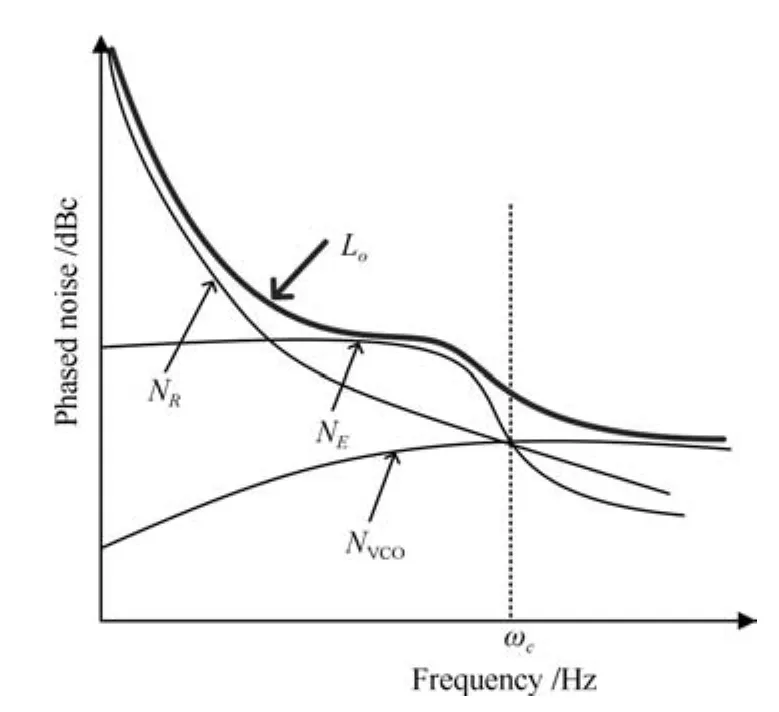

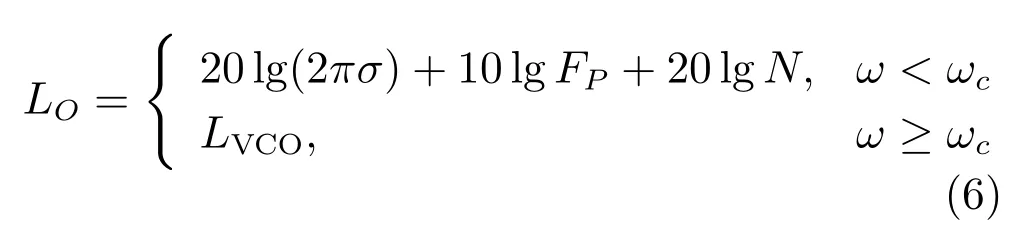

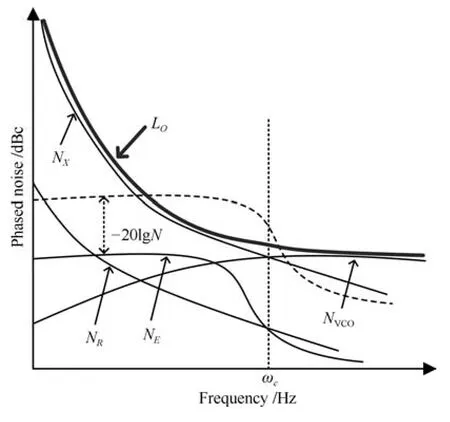

式(1)中各变量的传递参数在其频域特性如图2所示,图中ω为锁相环的环路带宽,从图中可以看出,锁相环对输入信号FR、FE表现为低通,而对FVCO表现为高通,所以当输出信号FO的带宽ω<ωc时,FO的相噪由FR和FE的相噪和决定;当ω>ωc时,FO的相噪由FVCO的相噪决定.最终,锁相环输出信号FO的相噪为所有信号的相噪功率谱密度之和[5],即:

式中

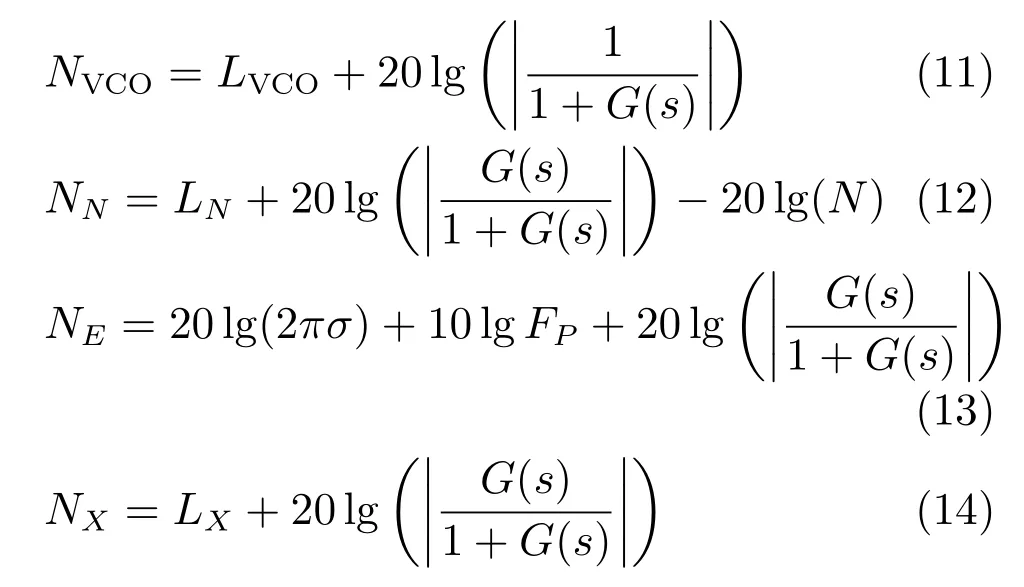

式中FP=FR/R=FVCO/N.NVCO是VCO的相噪,LVCO为VCO自身的相噪;NR为参考信号的相噪,LR为参考信号自身的相噪;NE为数字噪声的相噪,其中20lg(2πσ)为鉴相器的相位噪声基底(Normalized phased noise fl oor),由鉴相器芯片资料提供[9];FP为环路的鉴相频率(Hz).各部分相噪表现如图3.

图2 传递参数频域特性Fig.2 Passing parameters character on frequency domain

图3 锁相环中各输入信号相噪谱表现Fig.3 Input signals′phase noise spectrum performance in the PLL

最终的输出信号FO带内相噪主要由NR和NE中较差的决定,而一般选用的FR要求谱纯度极高(即NR≤NE).因此锁相环中,环路带宽以内的相位噪声主要由NE决定,而环路带宽以外的相位噪声由NVCO决定,最终FO的相噪计算见式(6).

2 新方案介绍以及性能指标分析

2.1 新方案原理介绍

相位噪声、频率分辨率以及频率切换时间、杂散等是射频信号最重要的指标,新方案将从优化这几项指标方面进行设计.对传统锁相环电路结构的分析可知,近端相位噪声指标主要由FE决定,从式(6)可以看出,在需要保证输出信号满足要求的情况下,可以减小反馈回路的分频系数N而优化带内相位噪声指标,如果在VCO的反馈回路引入100MHz的整数倍信号FX(保证FO−FX≤100MHz),与FO的反馈信号混频获得100MHz以内的信号,经过R分频后参与环路鉴相,可以消除反馈回路的分频系数N,达到优化带内NR和NE的相位噪声的目的.

射频信号的频率分辨率直接决定了测量仪器的测试精度,而传统锁相环中R×FO=N×FR,所以其频率分辨率主要由分频器N和R的最小分频比决定,受限于小数分频器自身原理结构,最终传统锁相环方案中相对于GHz的射频信号,其频率分辨率最高只能达到Hz级别.在新方案中通过引入直接数字合成加混频技术(DDS混频),因DDS采用相位累加技术可以得到极高的频率分辨率,使得最终射频输出信号的频率分辨率达到0.1mHz级别.

通过上述分析得到新系统的方案框图如图4.在新方案中,首先,将100MHz参考信号经过M 次整数倍频后得到FM,FM=M×100MHz,经功分器分两路,第一路FM送入DDS进行频率合成,得到FDDS(频率范围100MHz∼130MHz的窄带信号),然后通过多级带通滤波器进行带外滤波,输出信号与第二路FM混频,获得FN(FN=FM+FDDS,带宽30MHz),这样得到的窄带信号频率分辨率达0.1mHz,经过N 分频器分频后送入鉴相器鉴相,FP=FN/N.最终当环路锁定后,鉴相频率FP和输出信号FO分别满足式(7)和(8).

图4 新方案原理框图Fig.4 The new scheme block diagram

2.2 新方案相位噪声指标分析

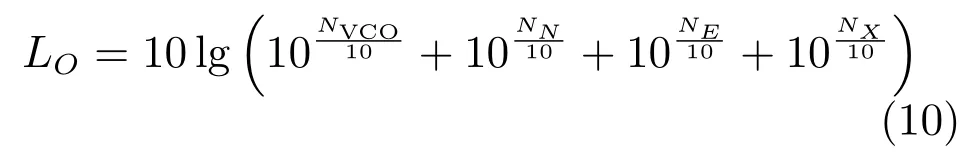

在图4新方案中,通过引入FX进行混频消除了锁相环中分频系数N 对相噪恶化的影响,通过引入DDS混频鉴相提高了FO的频率分辨率指标.新方案最终输出信号FO(s)的闭环传递函数见式(9).

从式(9)可以看出,最终环路带宽以内的信号相噪指标主要由FN、FE和FX中相噪较差的信号指标决定,而FN的N次分频信号作为新方案的参考信号代替传统方案中的FR,为保证新方案的最终输出信号相噪指标不会因引入DDS而恶化,这里必须保证FDDS的相噪指标NDDS优于100MHz的M次倍频信号FM的相噪指标NM,即NDDS≤NM.

新方案环路的最终输出相噪见式(10),通过与式(2)比较发现,相对于传统锁相环方案,新方案中信号FE的相位噪声优化了20lgN,但是引入了新的信号源FN和FX.另外环路带宽以外的相位噪声指标也得到了优化.比较NX、NN和NE发现,FN经过N次分频后相噪指标优化了20lgN,FX为100MHz的X 次整数倍,FX≫FP,所以环路带宽内的相位噪声主要由NX决定.因此新方案中FX成为能否获得超低相噪的关键.其中新方案各输入信号相噪谱表现如图6所示.

图5 新方案各输入信号相噪表现Fig.5 Input Signals′phase noise spectrum performance in the new scheme

式中

这里FX为100MHz的整数倍点频,且FO−FX≤100MHz.目前主要有三种方式获得:第一种为锁相环方案,但是该方案得到的信号相位噪声与传统方案相同,甚至在新方案中因引入复杂的电路结构导致恶化,所以新方案中FX不能使用锁相环获得.第二种方案为整数倍频方案,直接经过M次整数倍频获得FX.第三种方案为混频方案,通过对100MHz基准信号进行放大、滤波、混频等处理,最终获得想要的FX信号.FX的具体产生方式如图6所示,下面就两种方案获得的信号相位噪声作具体分析.

对于混频方案,混频是对两输入信号实现了加法或减法,所以混频器的输出信号相位噪声为两输入信号的相位噪声之和,具体计算同式(2),最终的相位噪声主要取决于相位噪声较差的信号,而当两信号相位噪声相同时,输出信号相对于输入信号的相噪恶化10lg2=3dB.

对于倍频方案,经过M 次整数倍频后信号相噪会恶化20lgM,当M=2时,信号相噪会恶化6dB,与混频方案比较发现,相同的输出频率下,采用混频方案,相噪会优化3dB.但是混频电路对信号质量要求较高,需要增加多级放大、混频、滤波等电路保证信号质量,所以在实际应用中,在成本、电路空间允许的情况下,建议优先使用混频电路.

图6 FX产生方案框图Fig.6 FXsignal generation block diagram

3 实际工程应用

3.1 工程应用介绍

在工程应用中,选用高纯度的100MHz基准信号,其相噪指标为−163dBc@10kHz,这样保证了在传统的锁相环方案中,NR≤NE,使数字噪声成为制约信号相位噪声的主要因素.

在传统方案中,如果输出FO=3250MHz,FR=100MHz,令R=2,得到FP=50MHz,N=65,一般的鉴相芯片(参考ADF4106),其相噪基底20lg(2πσ)= −223dBc/Hz[9],代入式(6)得到FO的相噪指标为−110dBc@10kHz.

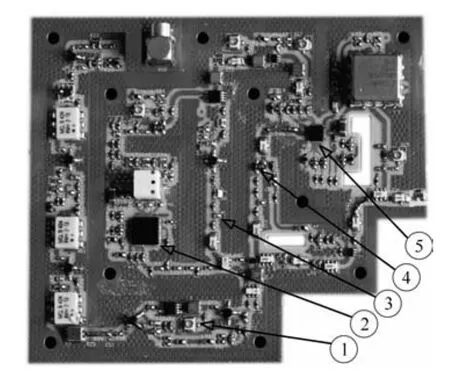

新方案的工程应用如图7,电路中分别使用ANALOG公司的ADF4106和AD9956作为鉴相芯片和DDS分频芯片,VCO使用ZCommunications公司的CRO3250B,最终输出FO频率范围为3225MHz∼3275MHz.

图7 实际工程应用印制板Fig.7 Printed circuit board in the practical engineering application

实际使用中,因受限于电路体积及成本考量,最终选择倍频方案获得FX混频信号,同时将M次倍频电路和X次倍频电路合为一路,最大限度节约电路成本,如图8所示;实际应用中电路包含5部分,分别为:1)100MHz倍频电路;2)DDS分频电路;3)FM与FDDS混频电路;4)FX与FVCO混频电路;5)锁相环路;具体见图7.

电路中首先将100MHz参考信号经过4次二倍频,获得1600MHz,其理论相噪为 −139dBc@10kHz,之后分两路,一路作为FM信号进行DDS混频处理,最终得到FN,频率范围 1700MHz∼1730MHz,然后 N 分频后作环路鉴相;另一路1600MHz经 2倍频得到FX=3200MHz,FX的理论相噪为−133dBc@10kHz,之后参与混频鉴相.图8为使用Keysight公司的N9030A信号分析仪实测的FX相噪指标,为−130dBc@10kHz.将上述FN和FM的取值代入式(8)得到工程实例中最终输出信号满足式(15).

图9 新方案FX=3200MHz的相位噪声指标Fig.9 The phase noise curve of FX=3200MHz in the new scheme

3.2 工程应用指标分析

从式(15)可以看出,最终FO的分辨率取决于FDDS,而FM进入DDS后先4分频,得到400MHz信号,之后进行频率合成得到FDDS,根据AD9956资料[10]得到DDS的输出频率FDDS为式(16)(式中FTW 为DDS控制字,字长48bit,通过SPI置数控制),其频率分辨率ΔFDDS为式(17),结合式(15)和(17)可以看出,新方案的输出信号频率分辨率理论值可达0.1mHz.

当FO=3250MHz时,FP=FO−FX=50MHz,如果在锁相环中引入小数分频,最终的输出信号近端噪声相对于整数分频会恶化3dB,所以新方案中必须保证N 为整数,且 FN在 1700MHz∼1730MHz之间,代入式(15)得到 N=34,此时对应 FN=1700MHz,FDDS=100MHz,输出信号FO的理论相噪指标应该与混频鉴相信号FX指标相同,即−133dBc@10kHz. 实际使用 Keysight公司的E5052B相位噪声分析仪测得的输出信号相噪指标如图10,从图中可以看出,3250MHz的相噪指标为−127dBc@10kHz.

图10 新方案FO输出为3250MHz的相噪曲线Fig.10 The phase noise curve of the 3250MHz in the new scheme

虽然引入DDS会恶化信号的频谱纯度,但是通过上述分析可知,新方案中锁相环路对FDDS与FM混频产生的信号FN表现为低通特性,杂散信号可以通过锁相环路滤除.实际使用Keysight公司的N9030A信号分析仪测得的输出信号3250MHz,带宽500MHz以内的非谐波杂散指标如图11,从图中可以看出,其500MHz带宽内杂散指标优于−76dBc.

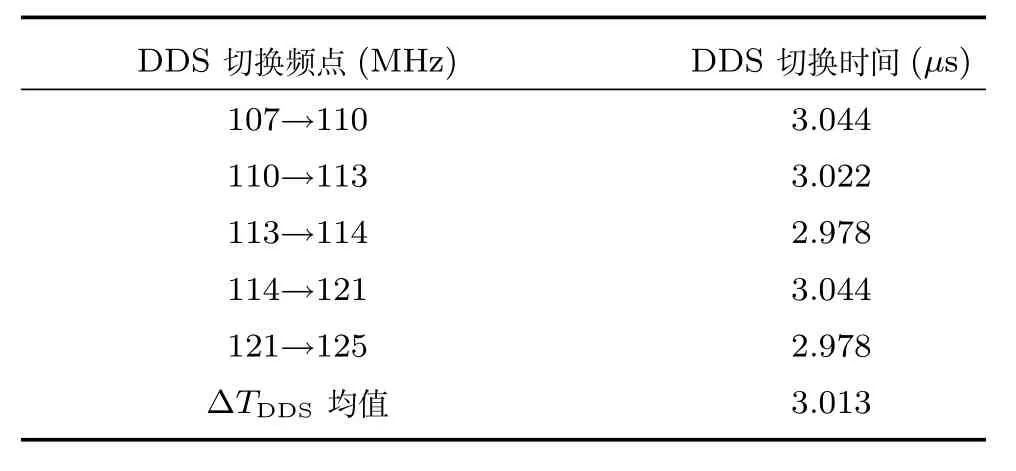

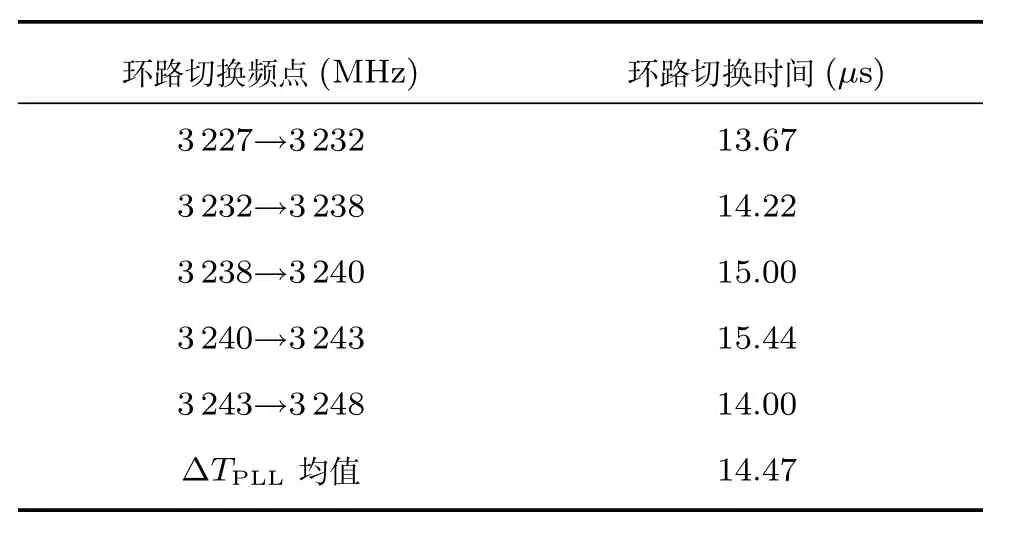

本方案通过引入DDS增加输出信号频率分辨率,同时因DDS的引入会相应的增加频率锁相时间,使用HP53310A调制域分析仪测得的DDS频率切换时间见表1,相对应的的环路输出信号FO切换时间见表2,从表中可以看出,环路的平均切换时间为15µs,DDS的平均切换时间为3µs,占总时间的20%,可以看出该方案在引入DDS得到极高分辨率的情况下,可以兼顾频率切换时间.

图11 FO=3250MHz时,500MHz以内杂散测试图Fig.11 The spurious test pattern at FO=3250MHz within 500MHz bandwidth

表1 DDS频率切换时间Table 1 DDS frequency hopping time

表2 环路切换时间Table 2 Loop locked time

通过上述分析可以看出,理论上输出信号FO= 3250MHz处相位噪声指标应为−133dBc@10kHz,而使用相位噪声分析仪实际测得的指标为−127dBc@10kHz,这是因为理论值中已经忽略数字噪声和参考源噪声,但是实际情况中通过式(10)可以发现,两者的相噪同样会叠加在最终的输出信号噪声中;另外,电路中因分频、倍频和混频等电子元器件会引入白噪声叠加到输出信号中,使得最终得到的数据与理论分析偏差6dB,满足预期要求.相对于传统方案,新方案中得到的信号相噪指标比传统方案提高了17dB.因本案例空间有限,实际电路采用倍频的方式获得FX参与环路混频鉴相,而根据上述分析可知,在电路空间充裕,相噪指标要求更高的条件下,如果采用混频方案获得FX后再进行混频鉴相,理论上可以获得更好的近端相噪指标.

新方案中因引入DDS进行频率合成,在不影响频率切换时间的前提下,使得FO的频率分辨率理论值达到0.1mHz.通过图11可以看出,因锁相环对混频信号表现为低通特性,环路中输出信号杂散指标并没有因引入FDDS和FX等信号进行倍频、混频等处理而变差,最终的输出信号频谱纯度极高.

4 结论

本文提出的超低相位噪声合成源方案,通过在传统的锁相环反馈回路中,引入高纯度的信号FX参与混频鉴相,将输出信号近端的相噪指标提高了17dB,同时因引入DDS进行频率合成,在兼顾频率切换时间和相噪等指标的前提下,将输出信号FO的频率分辨率理论值提高到0.1mHz.最终整个电路并没有因为引入DDS、FX等信号混频鉴相而造成过多的杂散信号,新方案保证了输出信号极高的频谱纯度.

1 Hou Jun-Feng.Design and Implementation of Multi-loop Frequency Synthesizer[Master dissertation],University of Electronic Science and Technology of China,China,2014(侯君锋.多环路频率合成器的设计与实现[硕士学位论文],电子科技大学,中国,2014)

2 Chen Cong-Hong.The Research of Low Phase Niose X-band Signal Generator[Master dissertation],University of Electronic Science and Technology of China,China,2014(陈丛宏.低相噪X 波段信号发生器的研究[硕士学位论文],电子科技大学,中国,2014)

3 Cheng Peng.Principles of Automatic Control.Beijing:Higher Education Press,2003.35−57(程鹏.自动控制原理.北京:高等教育出版社,2003.35−57)

4 Chu Zhao-Bi,Zhang Chong-Wei,Feng Xiao-Ying.Multiharmonics analysis based on fundamental frequency estimate.Acta Automatica Sinica,2009,35(5):532−539(储昭碧,张崇巍,冯小英.基于基波频率估计的多谐波分析.自动化学报,2009,35(5):532−539)

5 Fang Yong.Design of 8-10G Low Phase Noise Frequency Synthesizers[Master dissertation],Nanjing University of Science and Technology,China,2011(方涌.8-10G 低噪声频率综合器系统设计[硕士学位论文],南京理工大学,中国,2011)

6 Mehrotra A.Noise analysis of phase-locked loops.IEEE Transactions on Circuits and Systems I:Fundamental Theory and Applications,2002,49(9):1309−1316

7 Maあezzoni P,Levantino S.Analysis of VCO phase noise in charge-pump phase-locked loops.IEEE Transactions on Circuits and Systems I:Regular Papers,2012,59(10):2165−2175

8 Arakali A,Gondi S,Hanumolu P K.Analysis and design techniques for supply-noise mitigation in phase-locked loops.IEEE Transactions on Circuits and Systems I:Regular Papers,2010,57(11):2880−2889

9 ADF4106 data sheets[Online],available:http://www.analog.com,February 25,2016.

10 AD9956 data sheets[Online],available:http://www.analog.com,February 25,2016.

A Ultralow-phase-noise Scheme for Frequency Synthesizer

WANG Li-Fei1,2ZHANG Ning1,2PENG Zi-Jian1,2XUE Pei-Xiang1,2LI Wei-Liang1,2

Frequency synthesizer is one of the most important component of RF generator and spectrum analysis.The performance of its output signal is evaluated in terms of phase noise,scattering,frequency resolution and frequency hopping time.By analyzing the traditional theory of phase-locked loop,a ultralow-phase-noise scheme for the frequency synthesizer is put forward(bandwidth within 100MHz).In order to make the frequency resolution of the output signal reach to 0.1mHz in theory and optimize the in-band phase noise cver 17dB,direct digital synthesizer(DDS)and mixer phase detection technology based on phase-locked loop are introduced.Consideration is also given to both scattering and frequency hopping time to ensure the output signal is stable and reliable.The synthesizer has a good application in the fi eld of automatic test.

Frequency synthesizer,phase-locked loop,high resolution,ultralow phase noise

Wang Li-Fei,Zhang Ning,Peng Zi-Jian,Xue Pei-Xiang,Li Wei-Liang.A ultralow-phase-noise scheme for frequency synthesizer.Acta Automatica Sinica,2017,43(12):2225−2231

2016-02-28 录用日期2016-10-14

February 28,2016;accepted October 14,2016

电子测试技术重点实验室基金项目(9140C120201130C12050)资助

Supported by Project of Science and Technology on Electronic Test&Measurement Laboratory(9140C120201130C12050)

本文责任编委辛景民

Recommended by Associate Editor XIN Jing-Min

1.电子测试技术重点实验室 青岛266555 2.中国电子科技集团公司第四十一研究所青岛266555

1.Science and Technology on Electronic Test&Measurement Laboratory,Qingdao 266555 2.The 41st Research Institute of CETC,Qingdao 266555

王李飞,张宁,彭子健,薛沛祥,李维亮.一种超低相位噪声频率合成源方案设计.自动化学报,2017,43(12):2225−2231

DOI10.16383/j.aas.2017.c160162

王李飞 中国电子科技集团公司第四十一研究所工程师.2012年获得山东大学控制科学与工程学院学士学位.主要研究方向为微波毫米波高性能宽带合成源设计.本文通信作者.

E-mail:wanglifei0200@126.com

(WANGLi-Fei Engineer at the 41st Research Institute of CETC.He received his bachelor degree from Shandong University in 2012. His research interest covers wide-band highperformance frequency synthesizer design in microwave and millimeter waves.Corresponding author of this paper.)

张 宁 中国电子科技集团公司第四十一研究所高级工程师.2001年获得山东大学电力学院学士学位.主要研究方向为微波测量仪器.

E-mail:zn-1014@163.com

(ZHANG Ning Senior engineer at the 41st Research Institute of CETC.She received her bachelor degree from Shandong University in 2001.Her research interest covers microwave measuring instruments.)

彭子健 中国电子科技集团公司第四十一研究所工程师.2007年获得西安交通大学电信学院学士学位.主要研究方向为软件开发与设计.

E-mail:zijian1100@163.com

(PENG Zi-Jian Engineer at The 41st Research Institute of CETC.He received his bachelor degree from Xi′an Jiaotong University in 2007.His research interest covers software design and development.)

薛沛祥 中国电子科技集团公司第四十一研究所工程师.2011年获得北京航空航天大学自动化与电气工程学院硕士学位.主要研究方向为小信号测量技术和控制工程.

E-mail:xuepeixiang@163.com

(XUE Pei-Xiang Engineer at The 41st Research Institute of CETC.He received his master degree from Beihang University in 2011.His research interest covers small-signal measurment and control engineering.)

李维亮 中国电子科技集团公司第四十一研究所工程师.2013年获大连理工大学控制理论与控制工程专业硕士学位.主要研究方向为射频电路设计.

E-mail:wei.liang123456@163.com

(LI Wei-Liang Engineer at The 41st Research Institute of CETC.He received his master degree from Dalian University of Technology in 2013.His main research interest is radio freqency circuit design.)