用于高速传感器的宽频差分50%占空比校正器

2017-12-26陈祥雨

陈祥雨

(东南大学外国语学院,南京 211189)

用于高速传感器的宽频差分50%占空比校正器

陈祥雨*

(东南大学外国语学院,南京 211189)

提出了一种用于高速传感器的宽带差分50%占空比校准电路。与传统CMOS模拟占空比校准电路相比,所提出电路结构简单工作稳定,并且证明了该电路的最高校正频率可达4 GHz。所提出电路中的占空比检测器采用基于低通预滤波的连续时间积分器和带有源耦合逻辑结构的时钟缓冲器链。采用了0.18 μm CMOS工艺,并针对高速应用条件进行了优化。实验结果表明,所提出电路在500 MHz至4.0 GHz频率范围内正常,可接受的输入占空比为30%~70%。在4 GHz输入信号条件下功耗为5.37 mW,输出抖动为19.3 ps。测试芯片面积为550 μm×370 μm。

差分;占空比校准电路;连续时间积分器;源极耦合逻辑

在高速传感器采样电路中,时钟信号的完整性对于系统的信噪比和动态范围等性能至关重要[1-3]。随着工作频率的不断提高,想要获得具有合适波形、占空比、低附加抖动和足够幅度的时钟信号变得越来越困难。高速高精度ADC在上述高速传感器采集电路中扮演着关键作用,直接决定了信号的还原度和捕捉范围。当ADC的有效位数达到12 bit,采样频率为200 Msample/s的情况下,采样时钟的占空比和抖动制约了ADC的动态范围以及非线性误差。理论上可以将振荡器频率设置为系统时钟信号频率的两倍,并使用“二分频”模块生成50%的占空比时钟;不过,这样增加了系统功耗,并且在多频系统中实用性不高。因此,业界通常采用占空比校准电路(DCC)来获得精确的50%占空比时钟。

从已发表的技术文献来看,大多数常规DCC基于单端或单端输入差分输出[4-10]结构。单端电路可能会在开关切换期间产生严重的电流尖峰,在高频工作时产生较大的电源扰动。实际上,与CMOS静态逻辑相比,差分逻辑电路(例如,源极耦合逻辑(SCL))可以在以静态功耗为代价的情况下将开关噪声降低两个数量级[11-12]。传统的基于电荷泵的DCC[6]通常受电荷泵失配的影响。改进型差动电荷泵[7,10]降低了电荷泵失配的影响,然而,输出时钟正负脉冲的传输特性失配是不可避免的。参考文献[13]所述电路实现了较宽的占空比校正范围,且工作频率范围较宽,性能更好。

所提出的电路基于GF 0.18 μm CMOS工艺的高速DCC结构。整个DCC系统由两个负反馈回路组成,同时提高了收敛时间和精度。参考文献[13]中的控制级用来调节负载级电阻,替代了电流控制模式。与参考文献[13]基于低通滤波器的DCD不同,所提出的电路使用一种基于积分器的DCS结构作为DCD。当输入时钟波形具有50%占空比时,积分器输出差分信号为0。整个DCC系统由两个负反馈回路组成,从而提高了精度和速度。所提出的DCC采用差分时钟信号,具有简单稳定的架构,可在高达4 GHz的频率下进行时钟占空比校正。

1 系统设计

DCC的顶层拓扑结构如图1所示,采用全差分架构。两个控制级CS1和CS2用于扩展输入占空比范围。缓冲级BUF1和BUF2基于SCL逻辑。占空比检测器(DCD)采用了一个具有低通预滤波器的连续时间积分器,可以提高积分的精度。

图1 DCC的顶层拓扑

如图1所示,在两个CS中,输出节点的直流偏移电流可调,因此上升沿的输出转换速率可以增加或减小,而下降沿同时获得了相反的调节效果。设计中使用了一个反馈环路来产生差分控制电压CP和CN,这样无论输入占空比如何,反馈电路始终将输出占空比稳定在50%左右。图2展示了所提出DCC的工作时序图。如图2所示,波形的占空比依次从输入的30%变到输出的50%。

图2 所提出DCC的时序图

2 DCS的顶层建模

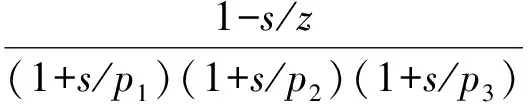

所提出DCC中反馈回路的简化传递函数如式(1)所示:

G(s)=KDCD·H(s)·KCS·e-s·td

(1)

因子KDCD表示DCD的转换系数,其值为8 mV/(1% error)。它表示,差分时钟信号若存在1%占空比误差,则等效差分直流电压为8 mV。KDCD的精确值由时钟信号的振幅和波形决定,且高频时略有下降。然而,在简化分析模型中,我们假设KDCD在整个工作频率范围内是一个常数。H(s)是DCD的电压-电压传递函数。DCD决定了直流环路增益和环路主极点位置。KCS代表控制级的增益,e-s·td表示缓冲级的传播延迟。

图3 所提出DCC的等效小信号模型

图3表示了所提出DCC的等效模型。Din和Dout分别代表输入和输出占空比。反馈回路的传递函数可以表示为

(2)

假设td1和td2的值足够小,G(s)可近似表示为

(3)

式中:td=td1+td2。

从式(2)到式(3)我们可以得到

(4)

基于p2,z和p3远远超过DCD的最大增益带宽乘积的假设,H(s)可以近似表示为

H(s)≈-Adc[1/(1+s/p1)]

(5)

所以

(6)

PM≈180°-90°-arctan(AdcKcsKDCDp1·td)

(7)

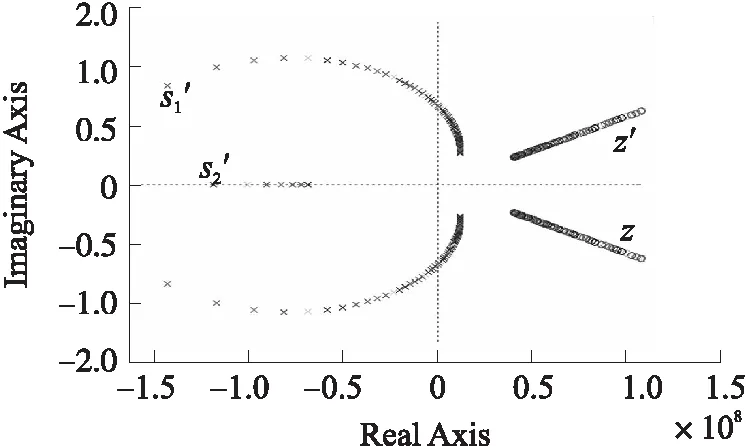

为了保证稳定性,相位裕度设置为大于60°。为了证明所提出的DCC的稳定性,分析了闭环函数的极点和零点,表达式为

(8)

图4给出了延迟时间对稳定性造成影响的一个例子。当延迟时间非常小时,极点位于s1和s1′,零点位于z和z′。当延迟时间增加时,极点将向s平面的右侧移动,导致不稳定。在本文中,整个DCC系统由两个负反馈回路组成。额外的反馈路径扩展了带宽,并提高了高频环路增益。因此,高频下的精度和速度也得到了提高。

图4 延迟对闭环传递函数极点和零点的影响

仿真结果表明,在所提出的DCC中,KCS在工作频率范围内处于0.035% error/mV到0.584% error/mV之间,Adc=61.16 dB,如图7和图9所示。KDCD=8 mV/(1%误差),在高频时略微下降。总延迟时间td随着时钟频率而增加,在4 GHz时td=115 ps。因此,所提出的DCC的相位裕度超过80°,闭环函数的极点都位于s平面的左侧。

3 电路设计

3.1 控制级(CS)

所提出CS的原理图如图5所示。

图5 所提出CS的原理图

在图5中,Vb是CS的偏置电压。差分控制电压CP和CN通过M1和M4转换为控制电流。使用电流镜M8~M11和M12~M15传递控制信号,从而将时钟馈通的影响最小化,如图6所示。连接到PMOS M2和M3的二极管用于抑制输出摆幅变化,即使M2和M3的漏极电流在较宽范围变化。

图6 控制电压在有无电流镜M8~M11和M12~M15时的波纹

图7 KCS随输入时钟频率的变化

KCS随输入时钟频率的变化见图7。引入KCS因子来代表CS的灵敏度。KCS的单位为(1% error)/mV,表示当CS增加1 mV控制电压时占空比的百分比变化。根据仿真结果,KCS在工作频率范围内从0.035% error/mV变化到0.584% error/mV。总体上来看,KCS随着输入频率的增加而增加。这是因为:(1)在高频下使占空比发生一定量的变化所需的绝对时间延迟较小;(2)在高频时上升沿和下降沿占整个时钟周期较大的百分比,因此相同量的斜率变化导致较大的占空比变化。KCS的变化直接导致闭环增益和环路带宽的变化,因此必须仔细处理以防止稳定性问题的出现。

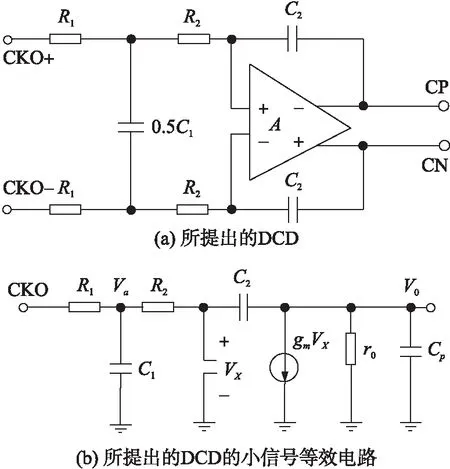

3.2 占空比检测器(DCD)

差分输出时钟CKO+和CKO-由DCD检测,占空比误差转换为差分直流电压,放大并最终反馈给CS。

所提出的是一种基于积分器的DCD,如图8所示。ro和Cp分别是输出DCD的阻抗。所提出DCD的前端使用无源器件(电阻器)实现,将差分电压电平传输特性的失配减少到最小。此外,还采用了一个二阶DCD来提高动态性能。

图8 所提出的DCD和所提出的DCD的小信号等效电路

根据所提出的DCD的小信号等效电路模型,假设使用单极OTA,那么DCD的电压传递函数H(s)可以简单地写为

(9)

其中

d3≈R2·C1·R1·C2·Cp·ro

(10)

d2≈R2·gm·ro·C1·R1·C2

(11)

d1≈gm·ro·(R1+R2)·C2

(12)

从式(9)可以计算出所有极点和零点的位置。

(13)

(14)

(15)

z≈+(gm/C2)

(16)

积分器的直流增益和单位增益带宽分别是

Adc=gm·ro

(17)

GBW=Adc·p1=1/(R2·C2)

(18)

根据式(1)、式(17)和式(18),环路增益和带宽分别是:

Adc_loop=KDCD·KCS·Adc

(19)

(20)

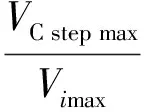

Adc_loop决定静态校正误差。DCD的动态稳定过程可分为大信号周期和小信号周期。在大信号稳定期间,最大转换速率为

(21)

式中:Vimax是DCD的最大差分输入电压。

总的转换时间是

(22)

式中:VCS step max是最大差分控制电压。

在小信号稳定期间,假设单极模型,则线性稳定时间为

(23)

式中:Ed是动态校正误差。

从式(22)和式(23)得出总的稳定时间为:

(24)

DCD的设计策略如下:

①由于静态校正误差可以写成

Es=1/Adc_loop

(25)

所以根据式(19)和式(25),可以得出

(26)

在最差的情况下,KDCD·KCS的值为0.28。

②根据式(24),R2·C2的值由下式确定

(27)

式中:KCS在最差情况下的值为0.035% error/mV

③令KCS=0.584% error/mV,根据式(12)计算最大环路带宽GBWloop_max。让p2对-z保持-20 dB/(°)的增益斜率。p2,z和p3应放置在远远超出GBWloop_max的位置,以最大限度地减少其对瞬态响应的影响。

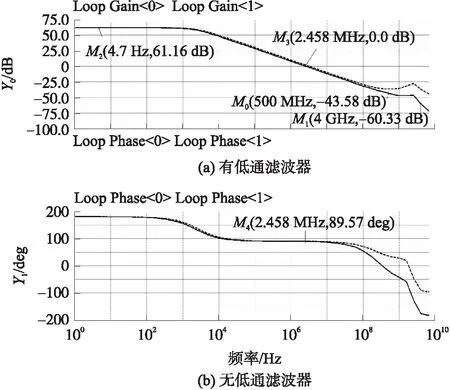

所提出的DCD的预期指标为Es=Ed=0.5%,Tsettle=1 μs。DCD在有无低通滤波器情况下的频率响应如图9所示,图中可见,低通滤波器的嵌入提高了DCD的整体性能。如图8所示,低通滤波器由R2和C2组成。除去R2和C2后,形成没有低通滤波器的电路。低通滤波器可以改善DCD的性能,可以降低所提出DCD的电压衰减。这样的话,上升沿的输出转换速率可以增加或减小,从而使系统更加精确。

图9 DCD的频率响应

3.3 缓冲级(BUF)

当忽略缓冲级的占空比失真时,可以使用延迟项e-s·td来描述其影响,其中td表示CS级和缓冲链的总延迟时间。延迟项e-s·td不会对环路增益或带宽做任何改变,但会引入额外的相移。总的来说,考虑到快速稳定,GBWloop_max频率的总相移不应超过120°。由主极点p1引入的相移为90°,假设p2,z和p3远远超出GBWloop_max,所引入的附加相移应限制在30°以下,即:

GBWloop·td<π/6

(28)

由于功耗与GBWloop成正比,所以最小的缓冲级功耗受到式(28)的限制。

图10 BUF单元原理图

所提出BUF单元的原理图如图10所示。Vbb是缓冲器的偏置电压,用以确保由电流镜像生成的Is保持不变。采用简单的SCL结构,由NMOS源和耦合对M1和M2组成,M1和M2交替的工作在饱和区和截止区,顶部的电阻R3和C决定了输出共模电压,尾电流源IB转入两个分支中的一个,并由输出电阻R1和R2转换成差分输出电压。

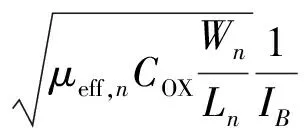

假设ΔV是由尾部电流IB引起的在R1(R2)上的电压降,则BUF单元的逻辑摆幅VSWING为2 V。此外,假设R1和R2的值均为RD,则逻辑摆幅为

VSWING=2RDIB

(29)

为了确保M1和M2工作正常,BUF单元的输入电压和输出电压必须满足以下两个方程,

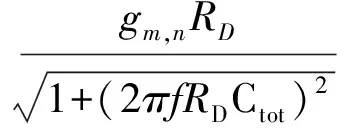

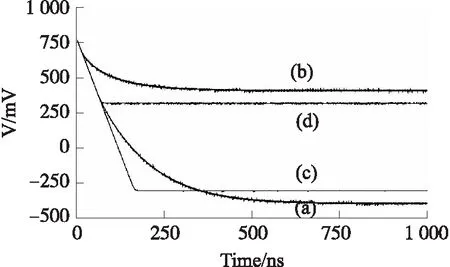

VINP-VOUTN (30) VINP-VOV-VTH (31) 式中:VOV和VTH分别为M1和M2的过驱动电压和阈值电压。 在由BUF单元串联组成的SCL缓冲级中, VOUTP=VINP (32) VOUTN=VINN (33) VSWING=VOUTP-VOUTN (34) 根据式(30)和式(31),可以得出 VOV (35) 在上述过程中,VTH≈490 mV,VSWING≈400 mV,根据式(29),为了使晶体管的寄生电容降到最小,M1(M2)的过驱动电压设定为尽可能大,这里设定为300 mV。 由于对称性质,逻辑阈值等于0,小信号增益为gm,n·RD,其中gm,n为M1(M2)的跨导,且ID1,2=IB/2。因为VINN=VINP=VOUTN=VOUTP=VDD-IB·R3-ΔV/2,且当ID1,2=IB/2时,M1(M2)的电压VDS和它们的VGS相等。所以,BUF单元的小信号增益为 (36) 此外,当输入时钟的频率为f时,BUF单元的小信号增益可以被描述为 (37) 传输延迟是 tPD,SCL=0.69RDCtot (38) (39) 式中:Cgg是后面BUF单元的输入栅极电容。 为了重构信号的波形,缓冲级的有效小信号增益应不小于 (40) 式中:VSWING_CS是CS的最小输出摆幅,仿真结果表明VSWING_CS≈200 mV。 对于输入时钟的最大频率,需要N个缓冲级,其中 N=logAv(fH)Again (41) 总的时间延迟是 td=NιPD,SCL (42) 总的电流消耗是 Itot=N·IB (43) 根据式(36)到式(41)、式(28)可改写成 (44) 流片电路中使用的缓冲级数量为2。 所提出的DCC采用GF 0.18 μm混合信号CMOS工艺设计和加工。图11所示的测试芯片(包括探针焊盘)的面积为550 μm×370 μm。 图11 The chip photography 系统建立过程通过后仿真进行验证,如图12所示。y轴是电压CP。总稳定时间在1 μs以内,和理论模型一致。 图12 所提出DCC的稳定行为 未封装的部件使用晶圆探针进行了测量。输出负载设置为50 Ω‖2 pF交流耦合。 实验结果表明,该电路可以在500 MHz~4 GHz频率范围内正常工作。整个频率范围内+/-0.5%误差的可调占空比范围超过了30%~70%。 图14 所提出DCC的波形 图13和图14分别是信号频率为500 MHz和4 GHz时的结果。 图13 所提出DCC的波形 DCC相对于不同输入占空比的测量结果如图15所示。整个频率范围内可接受的工作范围总体为30%~70%。在4 GHz输入时观察到峰值抖动为19.3 ps,如图16所示。 图15 所提出DCC在不同占空比输入和工作频率的波形 图16 4 GHz输入时的峰值抖动 表1列出了所提出电路和其他一些模拟DCC之间的比较。除在参考文献[16]中用0.055 μm CMOS工艺设计的DCC外,所提出DCC的后仿真结果优于列表中的其他DCC,在使用0.18 μm CMOS技术设计的电路中实现了更高的工作频率。 表1 性能统计与比较 本文提出了一种工作在500 MHz~4 GHz的差分50% DCC。所提出电路的新颖特性在于,占空比检测器使用了具有低通预滤波器的连续时间积分器和带有源耦合逻辑设计的时钟缓冲器链。 所提出的DCC采用了GF 0.18 μm CMOS工艺,并针对高速运行进行了优化。与传统的使用CMOS工艺设计的模拟占空比检测器相比,所提出的电路最大输入频率可达4 GH。实验给出了工作频率范围从500 MHz?4 GHz的测试结果。可接受的输入占空比范围为30%~70%。4 GHz时的功耗为5.37 mW,输出抖动为19.3 ps。 [1] Cai K,Ding K,Luo H,et al. Design of a Sample-and-Hold Circuit for High Speed CMOS Image Sensor[J]. Chinese Journal of Sensors and Actuators,2010,7:17. [2] Long J,Wei G,Wang X,et al. Design and Implementation of a PWM Based Sensor Readout Circuit[J]. Chinese Journal of Sensors & Actuators,2017,30(2):184-188. [3] Wang Y,Chen J,Hu J,et al. Research on Digital Interface Circuit for CMOS Micro-Capacitive Sensor with Low-Voltage Supply and Low-Power Consumption[J]. Chinese Journal of Sensors & Actuators,2015,28(2):198-204. [4] Yu X P,Fang Y,Shi Z. 2.5 mW 2.73 GHz non-Overlapping Multi-Phase Clock Generator with Duty-Cycle Correction in 0.13 μm CMOS[J]. Electronics Letters,2016,52(14):1261-1262. [5] Raja I,Banerjee G,Zeidan M A,et al. A 0.1-3.5-GHz Duty-Cycle Measurement and Correction Technique in 130-nm CMOS[J]. IEEE Transactions on Very Large Scale Integration(VLSI)Systems,2016,24(5):1975-1983. [6] Lin W M,Huang H Y. A Low-Jitter Mutual-Correlated Pulsewidth Control Loop Circuit[J]. IEEE Journal of Solid-State Circuits,2004,39(8):1366-1369. [7] Huang H Y,Chiu W M,Lin W M. Pulsewidth Control Loop Circuit Using Combined Charge Pumps and Miller Scheme[C]//Solid-State and Integrated Circuits Technology,2004. Proceedings. 7th International Conference on. IEEE,2004,2:1539-1542. [8] Han S R,Liu S I. A Single-Path Pulsewidth Control Loop with a Built-in Delay-Locked Loop[J]. IEEE Journal of Solid-State Circuits,2005,40(5):1130-1135. [9] Shin D,Song J,Chae H,et al. A 7 ps Jitter 0.053 mm Fast Lock all-Digital DLL with a Wide Range and High Resolution DCC[J]. IEEE Journal of Solid-State Circuits,2009,44(9):2437-2451. [10] Min Y J,Jeong C H,Kim K Y,et al. A 0.31-1 GHz Fast-Corrected Duty-Cycle Corrector with Successive Approximation Register for DDR DRAM Applications[J]. IEEE Transactions on Very Large Scale Integration(VLSI)Systems,2012,20(8):1524-1528. [11] Kiaei S,Chee S H,Allstot D. CMOS Source-Coupled Logic for Mixed-Mode VLSI[C]//IEEE International Symposium on Circuits and Systems. IEEE,1990:1608-1611 vol.2. [12] Alioto M,Palumbo G. Design Strategies for Source Coupled Logic Gates[J]. IEEE Transactions on Circuits & Systems I Fundamental Theory & Applications,2003,50(5):640-654. [13] Qiu Y,Zeng Y,Zhang F. 1-5 GHz Duty-Cycle Corrector Circuit with Wide Correction Range and High Precision[J]. Electronics Letters,2014,50(11):792-794. [14] Cheng K H,Su C W,Chang K F. A High Linearity,Fast-Locking Pulsewidth Control Loop with Digitally Programmable Duty Cycle Correction for Wide Range Operation[J]. IEEE Journal of Solid-State Circuits,2008,43(2):399-413. [15] Han S,Kim J. Hybrid Duty-Cycle Corrector Circuit with Dual Feedback Loop[J]. Electronics Letters,2011,47(24):1311-1313. [16] Jaiswal A,Fang Y,Nawaz K,et al. A Wide Range Programmable Duty Cycle Corrector[C]//Soc Conference. IEEE,2014:192-196. [17] Raghavan L,Wu T. Architectural Comparison of Analog and Digital Duty Cycle Corrector for High Speed I/O Link[C]//International Conference on Vlsi Design. IEEE,2010:270-275. AWideBandDifferential50%DutyCycle CorrectorforHighSpeedSensorsCHENXiangyu* (School of Foreign Languages,Southeast University,Nanjing 211189,China) A differential 50% Duty Cycle Corrector for high speed sensor is proposed in this paper. Compared with the conventional analog duty-cycle detectors designed in CMOS process,the proposed circuit has a simple and robust architecture and proofs the possibility of clock duty cycle correction at frequencies as high as 4 GHz. The novel features include a duty cycle detector using continuous-time integrator with a low-pass pre-filter and clock buffers chain designed with Source-Coupled Logic. The Duty Cycle Corrector is designed under Chartered 0.18 μm CMOS process and optimized for high-speed operation. The experimental results show that the circuit can work well at frequencies ranging from 500 MHz to 4.0 GHz and the acceptable input duty cycle range is 30%~70%. The power consumption is 5.37 mW and output jitter is 19.3 ps at 4GHz. The area of the test chip(include the probe pad)is 550 μm×370 μm. Differential;duty cycle corrector;continuous-time integrator;source-coupled logic 10.3969/j.issn.1004-1699.2017.12.016 2017-08-21修改日期2017-10-28 TP393 A 1004-1699(2017)12-1876-08 陈祥雨(1985-),男,山东德州人,工学学士,文学硕士,助理工程师,东南大学外语学习中心副主任。现从事电化教学、教学软硬件研发与测试、实验设备管理等研究。先后参与国家社科项目1项,省级重点社科项目1项。多次参加国际学术交流会议并发表论文,已申请专利6项,xiangyu0509@163.com。

4 实验结果

5 结论