适用于数字电源的新型温度自校准片上振荡器的设计

2017-12-05冯全源

谢 炜,冯全源

适用于数字电源的新型温度自校准片上振荡器的设计

谢 炜,冯全源

(西南交通大学 微电子研究所,四川 成都 611756)

设计了一种应用于数字电源的新型温度自校准高精度片上振荡器。该振荡器利用片内集成的环形振荡器作为“温度传感器”,环形振荡器的偏置电流设计成与热力学温度成正比,输出时钟信号频率对温度变化高度敏感,以此作为温度校准的参考信号,经过数字自校准算法产生控制RC振荡器充电电流大小的信号,校准RC振荡器输出时钟频率,从而完成片上实时温度自校准的功能。采用双比较器加SR触发器对称结构,降低比较器延迟误差。电路基于0.18 μm BCD工艺模型,采用Cadence和Hspice进行仿真。仿真结果表明,在–55~+155 ℃温度范围内,振荡器输出中心频率为10.1 MHz,振荡器的频率随温度变化的偏移量在±0.6%以内。

数字电源;环形振荡器;RC振荡器;低温漂;自校准;高频率

自2006年开关电源市场推出第一款数字电源芯片,模拟技术实现的电源芯片在市场的份额逐年减小,数字电源以其控制策略巧妙,设计可复用性高,对工艺依赖性低的优点被各大厂商和高校采纳和研究。在数字电源中,由于功率管的导通和关断均是由数字算法控制实现,这就要求时钟频率在温度变化时漂移尽量小,同时对片内振荡器输出时钟信号要求具备高频率、高独立性等特点。

在设计中,RC振荡器以其成本较低、结构简单、功耗较低被广泛使用[1]。文献[2-6]的输出时钟频率均太低,不能应用到数字电源中。文献[1]提出了一种高频率数字可调的RC振荡器,但是需要外接电阻阵列来调节频率,结构复杂同时增加了整体面积,并不适用在开关电源中。文献[7]设计了一种数字自校准的RC振荡器,通过芯片内部电容阵列来调节振荡频率,增加了芯片面积。综上所述,现有振荡器技术无法很好地满足数字电源对温漂、频率、面积和独立性的要求。文献[8]设计了带隙隔离策略减小振荡器的耦合噪声,通过数字修调方法减小温漂,但是效果不明显。

本文介绍了一种无需任何外部元器件或校准信息的高频温度自校准的振荡器。综合了RC振荡器和环形振荡器,其内部利用环形振荡器对温度变化的高敏感度,通过数字自校准算法产生相应的反馈信号调节RC振荡器的充电电流,减小温度变化对输出频率的影响;采用双比较器加SR触发器对称结构,降低比较器延迟的误差。提供了高频率高稳定性的片上时钟信号,并应用于数字电源芯片内部。

1 数字自校准振荡器

1.1 电路结构

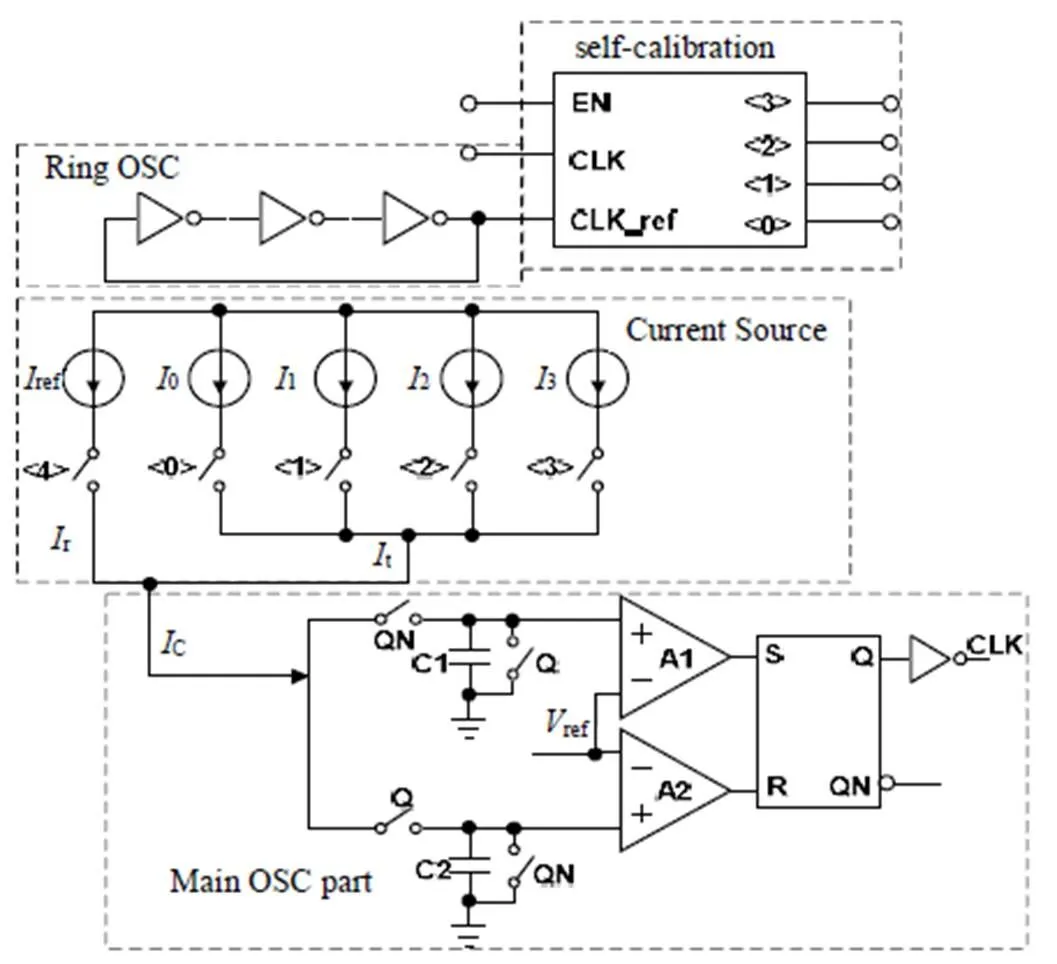

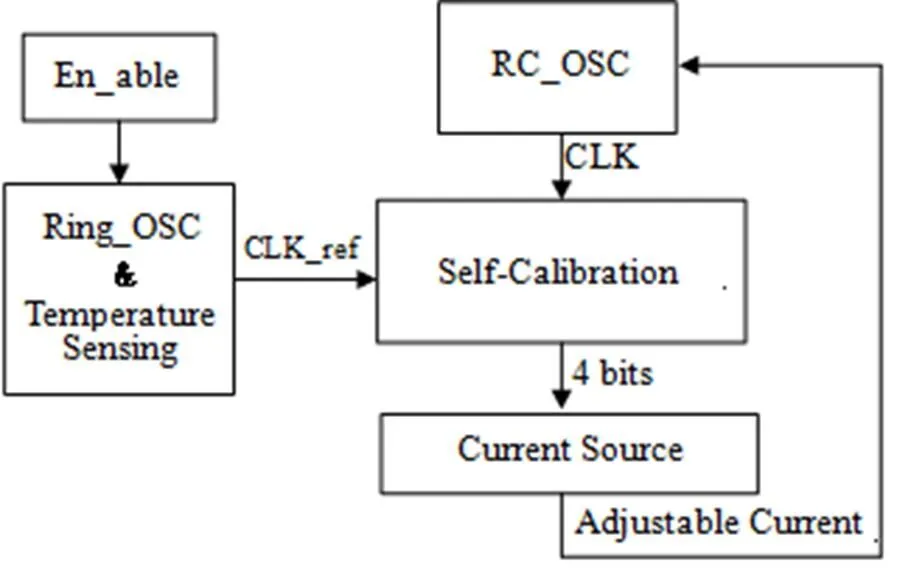

图1为设计的数字自校准振荡器电路的原理框图,由RC振荡器主体、电流源、环形振荡器和数字自校准等模块构成。

图1 数字自校准振荡器原理框图

RC振荡器主体通过可校准电流C对电容C1、C2充放电产生信号CLK,为芯片中数字算法部分提供高频高精度的时钟信号;环形振荡器模块相当于片上“温度传感器”,其温度敏感度远大于RC振荡器,输出信号CLK_ref用来作为参考时钟信号;数字自校准模块实时对CLK信号计数、比较调节电流源输出t,从而完成自校准功能。

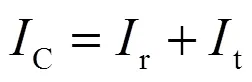

1.2 RC振荡器主体模块原理

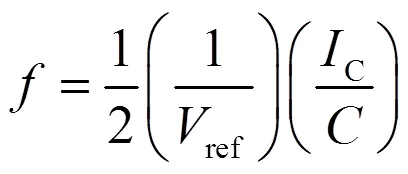

为了分析RC振荡器主体电路的工作原理,假设四个开关都是高电平闭合,低电平断开。初始状态下SR触发器处于复位状态,S=0,R=1,Q=0,QN=1,在这个状态下,开关QN闭合,开关Q断开使电容C2通过回路对地放电,电流源C对电容C1进行充电,直到电容上的电压C1超过比较器A1负端的参考电压ref;这时,比较器A1输出高电平,比较器A2输出低电平,S=1,R=0,Q=1,QN=0,电容C1通过回路对地放电,C对电容C2进行充电,直至超过比较器A2负端输入ref,于是,电路又回到了初始状态。一个完整的电路振荡周期完成并按此循环。假定,电容1=2=,则RC振荡器输出时钟频率为:

在常见的RC振荡器结构中,充电电压会分别同H、L比较,由于比较的电压不同,其上升延迟与下降延迟自然不同,存在设计周期与实际周期不符的情况。在本文设计的改进电路中,采用了同一比较电压输入的双比较器的对称结构,两个比较器的迟滞特性一样,有效地消除了由于迟滞特性带来的频率误差,提高了精度。

1.3 可调电流源具体实现电路

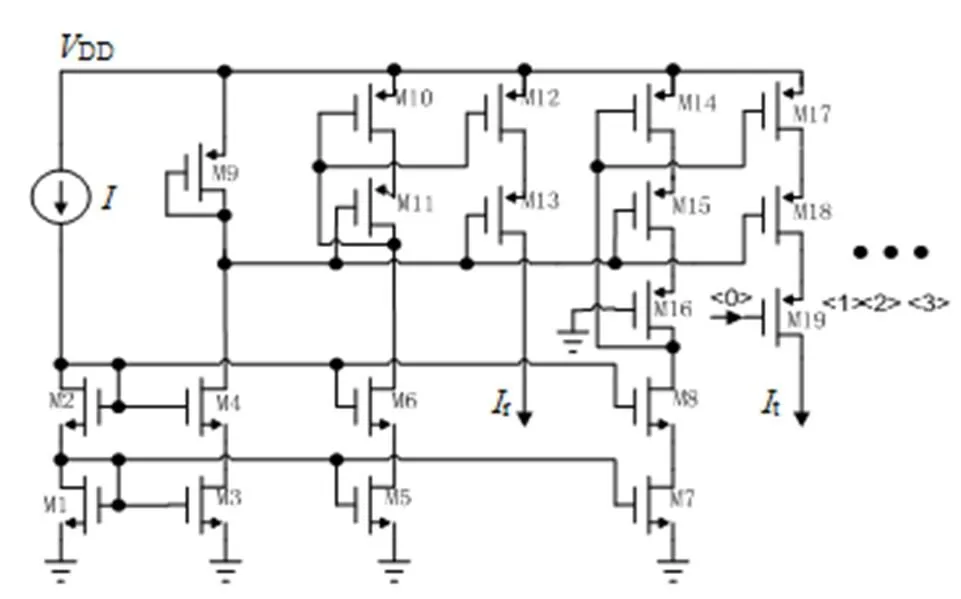

图2是电流源具体实现电路,其中M1、M2作为主控管,与M3、M4组成共源共栅电流镜,选择合适的M9管尺寸,确保M11与M13的栅源电压相等,并且当M10和M12的漏源电压相等,则会使共源共栅M12、M13消耗的电压余度最小,而且精确镜像电流,产生为RC振荡器电容充电的固定电流r。

图2 可调电流源具体实现电路

图2中M14~M19管组成低压共源共栅结构电流镜,其中M19管的栅极接数字校准模块输出的控制信号,当控制信号为低电平时,M19管导通,精确镜像电流,产生为RC振荡器电容充电的可变电流t;当控制信号为高电平时,M19关断,电流为零。最后输入RC振荡器的充电电流C为:

1.4 环形振荡器模块原理

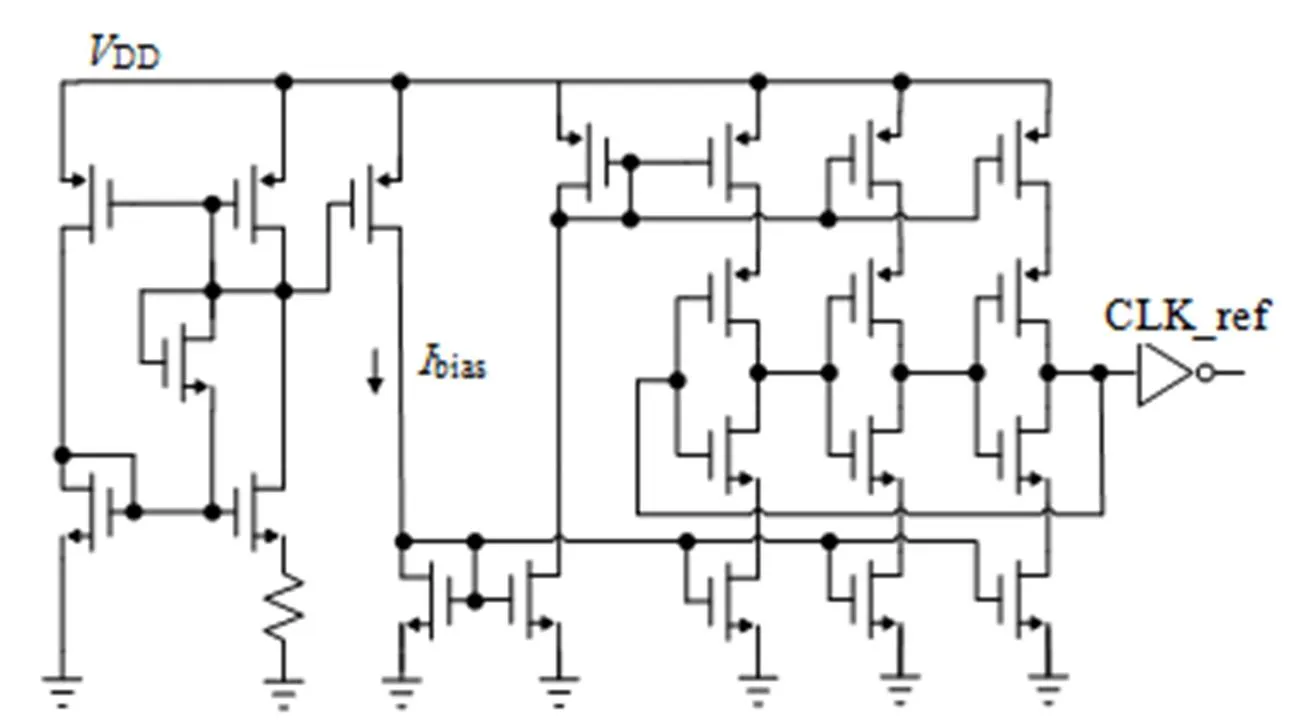

在本文设计中,利用一个简单的三级环形振荡器来检测温度变化。如图3所示。

图3 三级环形振荡器基本结构

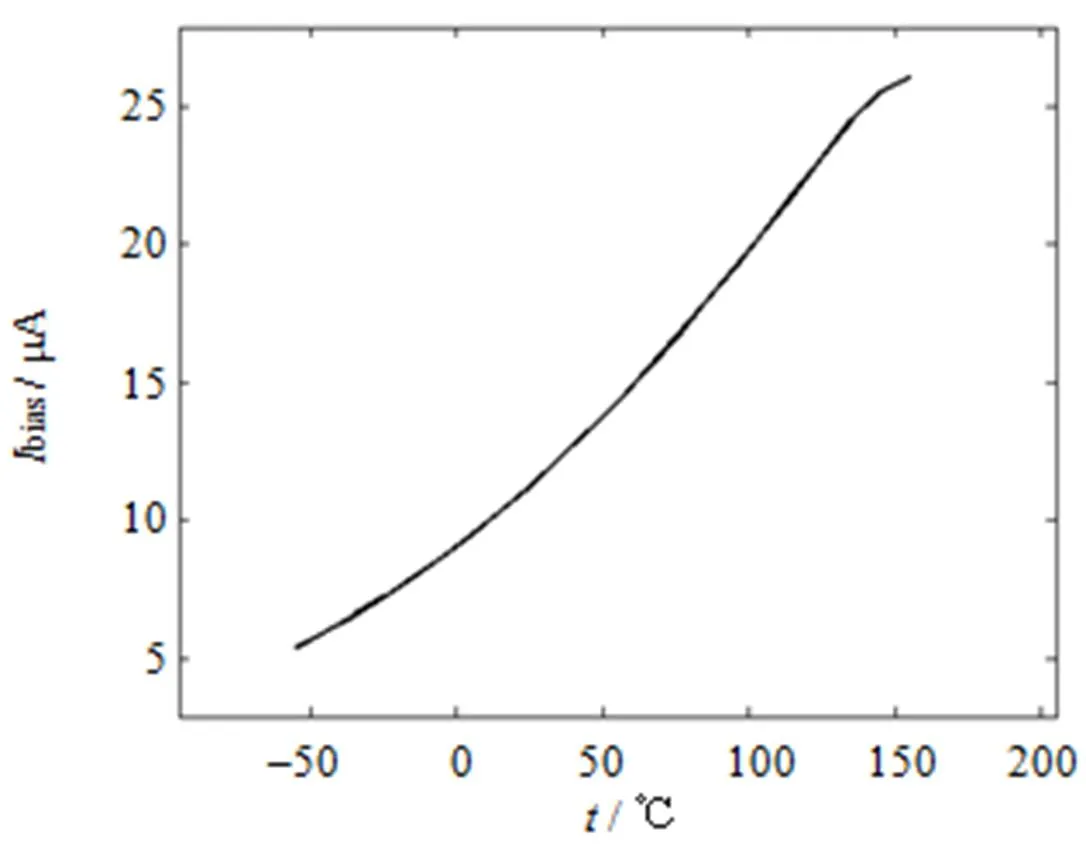

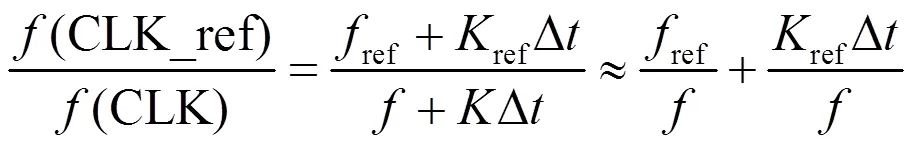

环形振荡器的偏置电流bias被设计成与热力学温度成正比,其温度特性曲线如图4所示。温度越高,偏置电流越大,对寄生电容充放电的速度就越快,输出时钟信号频率就越高。在温度变化从–55 ℃到155 ℃,偏置电流bias变化从5.4 μA到26 μA。

图4 环形振荡器偏置电流温度特性曲线

1.5 数字自校准原理

理论上,在没有数字自校准模块时,图1所示的电路也能实现振荡器的功能,但在实际应用中,数字电源芯片的周围环境温度不断变化,内部振荡器输出的时钟信号频率会与目标频率具有一定偏差,甚至这个偏差会超出一定范围导致数字算法出现较大误差引起芯片故障。在以往研究中提出的数字控制RC振荡器的设计,大多是基于芯片制备完成后测试时校准或者芯片外接时钟信息元件来校准频率,这在一定程度上增加了成本和占用面积;还有一些研究在芯片内部集成电阻阵列或电容阵列,通过数字控制相应地增加或减小电阻或电容值,根据公式(1),这在一定范围内能够有效降低温度漂移,但是电阻或电容阵列占用的芯片面积较大,同样会增加成本,而且制造偏差的存在,影响时钟信号的校准精度。

本文提出的设计可以完成在芯片使用过程中进行自适应的频率校准工作,无需外接任何时钟信息元器件,极大地降低温度变化对时钟信号的影响。可校准电流源模块仅由MOS管组成,占用面积小。自校准环路独立于RC振荡器主体模块,这意味着在补偿后可以将环路关断以降低功耗。

数字自校准原理框图如图5所示,上电开始,RC振荡器主体电路产生一个时钟信号CLK使数字部分开始工作,当数字部分控制的En_able使能信号为高电平(En_able=1),环形振荡器模块和自校准模块开始工作,CLK_ref作为自校准模块的系统时钟,其内部计数器对高电平时期的CLK信号进行计数,计数结果同寄存器内部设置的常数范围进行比较。如果计数结果大于常数,这意味着此时CLK_ref频率增大,温度变高,CLK频率会偏高,自校准模块会在同一周期通过调节4 bits信号,相应地减小对电容充电的电流。正常情况下,调节4 bits信号为0111,每一位控制一路修调电流,假设此时调节信号为0110,t减小,根据公式(1)和(2),时钟信号频率降低;反之,如果计数结果小于设定的常数,此时CLK频率偏低,充电电流被调大,时钟信号频率恢复到正常范围。

图5 数字自校准原理框图

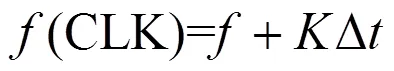

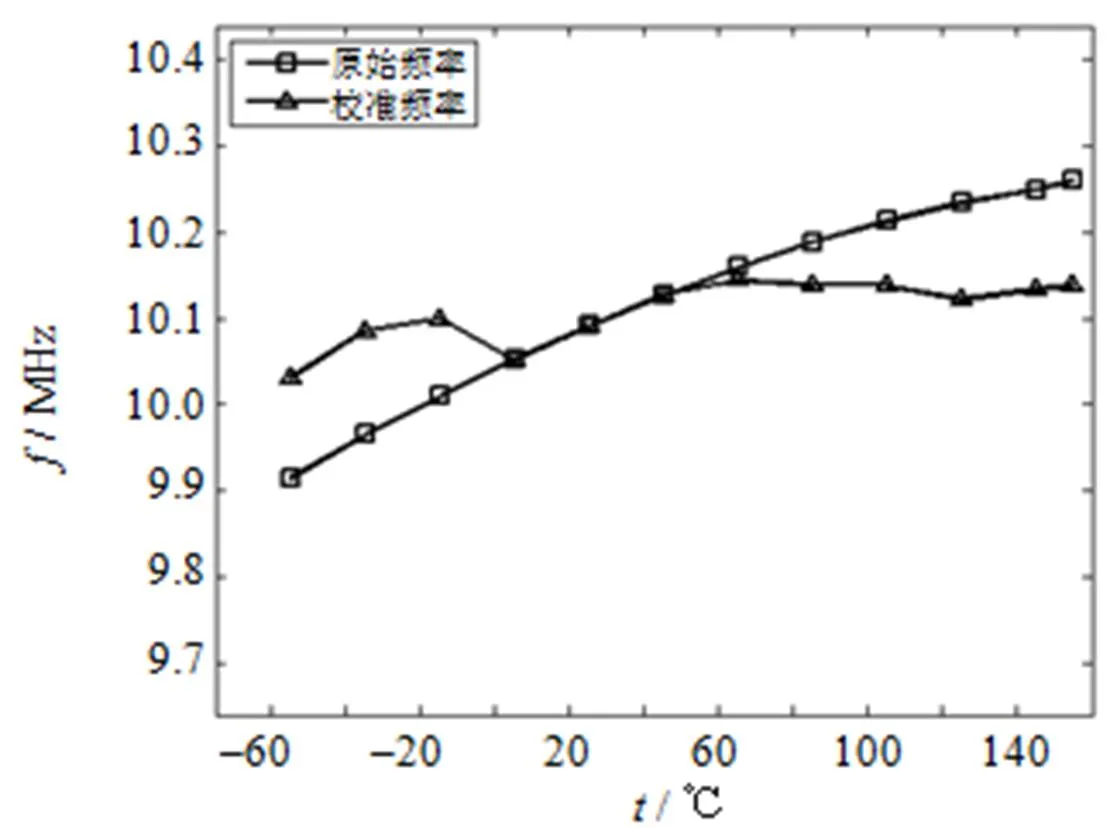

假定温度在27 ℃时为标准态,此时CLK信号频率为,CLK_ref信号频率为ref。环形振荡器输出时钟CLK_ref随温度变化比例为ref,RC振荡器主体输出时钟CLK随温度变化比例为。通过改变环形振荡器偏置电流设计ref/=16.5。

式中:Δ是温度变化量。

由式(5)可以看出,温度变化后两个时钟信号频率的比例会大于或小于在寄存器内部设置的标准值。根据这个比例相应地调节电容充电电流,最终使CLK时钟信号频率稳定在允许的范围内。

2 结果与讨论

基于BCD 0.18 μm 5 V工艺,设计了一款10.1 MHz的振荡器,利用Hspice仿真软件对数字自校准RC振荡器电路进行仿真验证。仿真条件:电源电压为5 V,RC振荡器主体基准电压ref=1.25 V,对温度从–55 ℃到155 ℃进行直流扫描。环形振荡器输出时钟信号CLK_ref频率温度特性曲线如图6所示。

图6 环形振荡器输出信号频率温度特性曲线

在温度从–55 ℃变化到155 ℃,CLK_ref信号频率从36.9 MHz变化到100.4 MHz,符合设计初对参考时钟信号的温度高灵敏度的要求。

表1列出在温度为27 ℃时,电源电压在4.5~5.5 V变化范围内,振荡器输出频率CLK的仿真结果。电源电压波动10%以内,振荡器输出时钟频率偏移在0.9%左右。

表1 时钟频率随电源电压仿真结果

Tab.1 The simulating result of frequency varying with power supply voltage

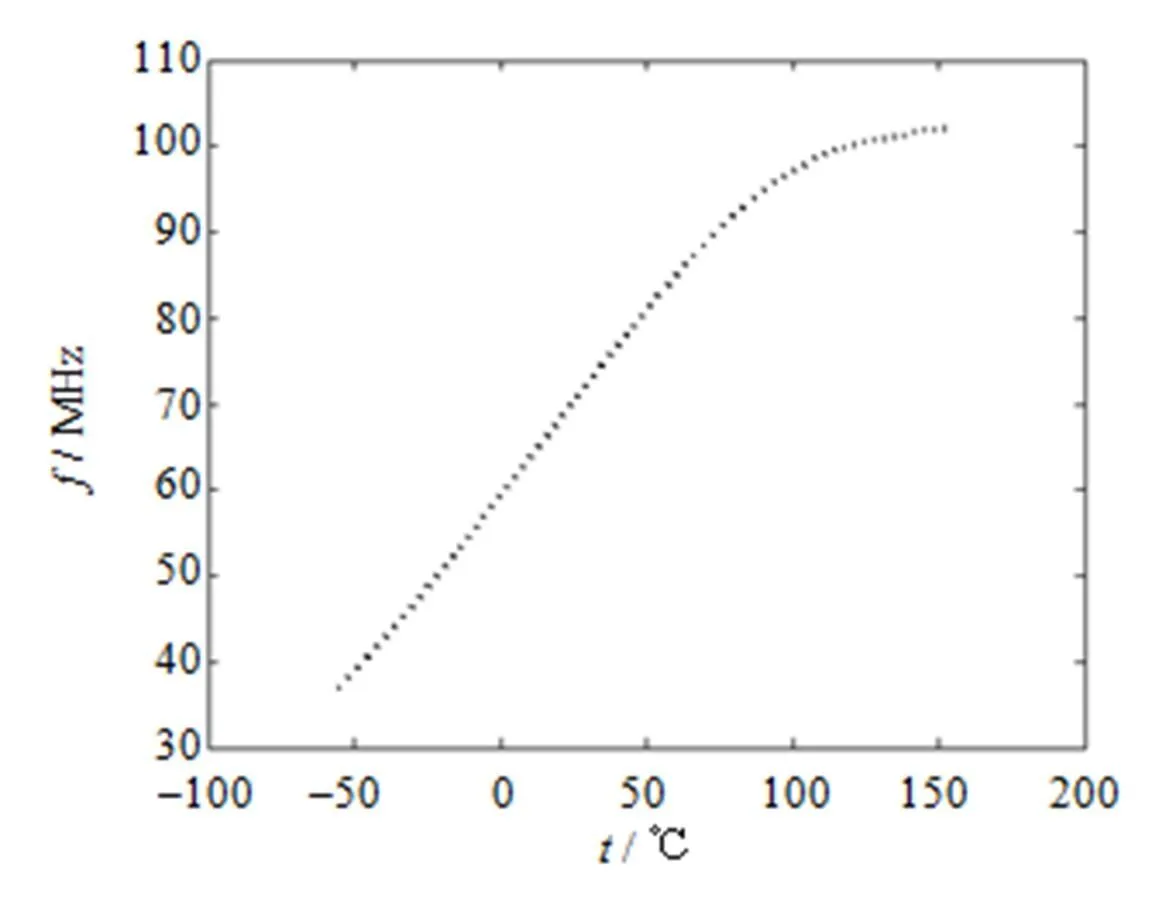

图7为振荡器输出频率温度特性曲线,图中,正方形连线表示未经过任何校准的CLK时钟信号的温度特性曲线,在温度变化范围为–55~+155 ℃,频率变化范围为9.9~10.27 MHz。三角形连线为自校准过后的温度特性曲线,可以看出,校准后的最终输出频率为10.1 MHz,时钟信号频率稳定在10.04~10.145 MHz,波动不超过±0.6%。

图7 振荡器输出频率温度特性曲线

3 结论

基于0.18 μm BCD工艺,设计了一种新型片上振荡器,无须任何外接时钟信息元件,通过数字自校准调节充电电流输出频率。在较宽温度范围–55~+155 ℃,振荡器输出时钟频率波动不超过0.6%。该电路不仅完全满足数字电源芯片对温漂的应用需求,亦可单独集成为时钟芯片,其输出频率为10.1 MHz,但并不局限于10.1 MHz。

[1] YU S H, CHEN Y M, GUO W D, et al. A digital-trim controlled on-chip RC oscillator [C]//Proceedings of the 44th IEEE 2001 Midwest Symposium on Circuits and Systems. New York: IEEE, 2001: 882-885.

[2] 董春雷, 宁振球, 金星, 等. 一种带温度补偿的高精度片上RC振荡器 [J]. 微电子学, 2015, 45(1): 58-62.

[3] 刘帘曦, 杨银堂, 朱樟明, 等. 一种新型高精度RC振荡器电路的设计 [J]. 电路与系统学报, 2005, 10(1): 147-150.

[4] 范建功, 冯全源. 一种适用于BUCK型DC-DC芯片振荡器电路设计 [J]. 电子元件与材料, 2015, 34(11): 81-84.

[5] 柯志强, 张涛. 一种高精度张弛振荡器的设计 [J]. 电子器件, 2014(3): 412-415.

[6] 付鑫, 冯全源. 一种频率可调低温漂振荡器的设计 [J]. 电子元件与材料, 2016, 35(7): 68-71.

[7] WANG J C, KOH L H, GOH W L. A 13.8-MHz RC oscillator with self-calibration for ±0.4% temperature stability from –55 to 125 ℃ [C]//2015 IEEE International Conference on Electron Devices Solid-State Circuits (EDSSC). New York: IEEE, 2015: 423-426.

[8] BOAS A V, OLMOS A. A temperature compensated digitally trimmable on-chip IC oscillator with low voltage inhibit capability [C]//2004 IEEE International Symposium on Circuits and Systems. New York: IEEE, 2004: 501-504.

[9] 洛建军, 范旭东, 刘海銮. 一种应用于SD/MMC控制器的RC振荡器的设计 [J]. 杭州电子科技大学学报, 2017, 37(1): 6-10.

[10] WANG J C, GOH W L, LIU X, et al. A 12.77-MHz on-chip relaxation oscillator with digital compensation for loop delay variation [C]//2015 IEEE Asian Solid-State Circuits Conference. New York: IEEE, 2015: 1-4.

(编辑:张金平)

Design of a novel on-chip oscillator with temperature self-calibration for digital power

XIE Wei, FENG Quanyuan

(Institute of Microelectronics, Southwest Jiaotong University, Chengdu 611756, China)

A novel on-chip oscillator with temperature self-calibration was designed for digital power. The oscillator used ring oscillator on chip as a “temperature sensor”, the offset current of ring oscillator was designed to be proportional to thermodynamic temperature. As a reference signal for calibration, the frequency of the output clock signal was highly sensitive to temperature. The self-calibration algorithm controlled the current of RC oscillator and calibrated the output clock frequency, which completed real-time temperature self-calibration function. The symmetric structure of two comparator and SR trigger was adopted to reduce the delay error. Based on 0.18 μm BCD process, the circuit was simulated by using Cadence and Hspice software. The simulation results show that the center frequency is 10.1 MHz, and the offset of oscillator frequency with temperature variation is within ±0.6% when the temperature ranges in –55-+155 ℃.

digital power; ring oscillator; RC oscillator; low temperature drift; self-calibration; high-frequency

10.14106/j.cnki.1001-2028.2017.12.005

TN432

A

1001-2028(2017)12-0021-04

2017-09-06

冯全源

国家自然科学基金重点项目资助(No. 61531016);四川省科技支撑计划重点项目资助(No.2016GZ0059;No.2017GZ0110)

冯全源(1963-),男,江西景德镇人,教授,研究方向为数字、模拟及射频集成电路设计,E-mail: fengquanyuan@163.com ;

谢炜(1991-),男,山西运城人,研究生,研究方向为模拟集成电路设计,E-mail: xdm2138@163.com 。

2017-11-30 14:13

网络出版地址: http://kns.cnki.net/kcms/detail/51.1241.TN.20171130.1413.010.html