一种基于时序路径的FPGA接口时序测试方法

2017-11-25朱伟杰费亚男郭冠军

朱伟杰 周 辉 费亚男 阳 徽 郭冠军

北京航天自动控制研究所,北京100854

一种基于时序路径的FPGA接口时序测试方法

朱伟杰 周 辉 费亚男 阳 徽 郭冠军

北京航天自动控制研究所,北京100854

针对航天高速高可靠FPGA接口时序测试,分析了FPGA接口类型及测试需求,介绍了一种基于时序路径的FPGA接口时序测试方法,结合时序路径模型,阐述了异步总线接口时序测试的测试流程和计算方法,并给出实际案例。该方法集成了功能仿真和静态时序分析的优点,特别适合极限工况下的FPGA接口时序验证,已经应用到多个航天高可靠FPGA接口测试中,与传统的动态门级时序仿真相比,能显著提高验证效率和测试覆盖率。

时序路径;FPGA接口时序测试;静态时序分析

随着军工产品向着高集成度、小型化、高速和高可靠性方向发展,FPGA和CPLD等可编程逻辑器件在军工产品中的应用数量成爆发式增长。FPGA应用的领域广泛、使用的场合关键,确保FPGA设计的正确性和可靠性已成为保证产品高可靠性的关键。作为电子设备的核心器件,FPGA需要与板级芯片、外围接口进行高速稳定的数据传输,其接口时序(特别是极限工况下)的正确性直接影响了整个设备的可靠性,因此,对各种工况下的FPGA接口时序进行完备地测试尤为重要。本文基于大量的FPGA软件测试实践,提出了一套基于时序路径的FPGA接口时序测试方法,并应用于多个型号FPGA测试中。该方法发现了诸多接口时序不满足而导致的通信错误问题,具有验证效率高、测试覆盖率全等优点。

1 FPGA接口分类及测试方法分析

1.1 FPGA接口类型与测试需求分解

FPGA片内有大量的逻辑门和触发器,适合实现复杂的时序逻辑和数字电路,作为核心器件,FPGA需要与外设(如DSP、存储器或其他特定功能芯片等)进行稳定可靠的数据通信,这对FPGA接口时序精度提出了苛刻的要求。接口时序测试的目的是确保FPGA芯片工作在极限与典型环境下,接口时序满足上级和下级系统接口时序要求,并留有时序余量(默认20%余量)。极限环境指FPGA工作在最大和最小工况下,典型环境是指典型工况,其中最大工况为FPGA芯片允许的最高温度和最低电压,该工况下器件内部信号传播延时最大,对建立时间不利但对保持时间有利;典型工况为FPGA芯片工作的典型温度和典型电压;最小工况为FPGA芯片允许的最低温度和最高电压,该工况下器件内部信号传播延时最小,对建立时间有利,但对保持时间不利。

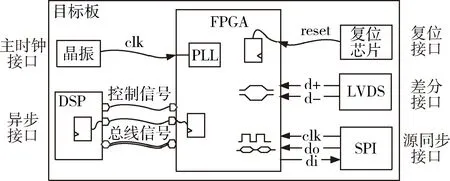

图1 典型FPGA接口类型示意图

一个典型FPGA目标板如图1所示,FPGA输入输出接口主要分为主时钟接口、复位接口、差分接口、源同步接口和异步接口等5类[1-2],这5类接口的测试需求分解如下:

(1)主时钟接口

主时钟包括外部输入时钟及通过FPGA片内PLL,DCM等生成多时钟域的时钟组。主时钟接口测试主要考核在基准时钟有漂移以及基准时钟有余量的情况下,输入接口及内部时序路径的建立保持时间是否满足工艺库中触发器的要求,输出接口的时序关系是否满足协议值的要求。测试方法是使用静态时序分析工具(如Synopsys公司的PrimeTime、FPGA厂商自带的时序分析工具)执行静态测试。

(2)复位接口

复位信号使内部触发器恢复到初始状态,其实现方式有异步复位、同步复位以及异步复位同步释放,建议采用异步复位同步释放的处理方式,它既可以达到无延时异步复位处理的要求,又能避免释放时刻寄存器输出出现亚稳态。复位接口的测试主要考核复位信号的恢复时间和移除时间是否满足工艺库中触发器的要求。测试方法是使用跨时钟检查工具(如QuestaCDC、SpyGlass等)查看异步复位是否进行同步化处理,或当复位同步化电路没有问题时,再通过静态时序分析工具执行静态测试检查同步释放的寄存器是否满足移除/恢复时间。

(3)差分接口

差分接口主要应用于高速信号传输,此类接口一般通过专用芯片或FPGA硬核实现单端转差分或差分转单端,接口测试主要考核差分信号的延时是否控制在工艺库的输入延迟偏差范围内。

(4)源同步接口

源同步接口的数据信号存在随路时钟信号,即时钟信号与数据信号存在固定的相位关系,如SPI,IIC通讯协议接口。针对源同步输入信号,需要考核信号的相对时序关系(如时钟和使能信号的偏斜值)是否满足要求;在输入信号为协议值以及与协议值存在20%偏差的情况下,数据的建立时间和保持时间是否满足要求。针对源同步输出信号,需要考核输出信号的相对时序关系是否满足任务书或外围芯片手册的要求。传统的测试方法是通过时序仿真进行动态测试。

(5)异步接口

异步接口是指外部输入信号与FPGA内部采样时钟无固定相位关系,如FPGA和板级芯片(如DSP,1553芯片等)交互的接口信号,此类接口直接影响电子设备内部通信的可靠性,是接口时序测试的重点。针对单比特异步输入信号主要考核信号是否采取了同步机制以避免出现亚稳态,测试方法是使用跨时钟域检查工具执行静态测试。针对输出信号要分析输出时序是否满足协议值的要求;针对多比特异步信号(如数据总线)主要考核在协议值以及与协议值偏差20%的情况下,总线建立保持时间是否满足要求,传统的测试方法是通过时序仿真进行动态测试。

1.2 传统FPGA接口时序测试方法分析

基于以上分析,异步接口由于接口信号数量多、时序关系复杂因而成为接口测试的高风险点和重点。传统的测试方法以芯片手册为基础,通过时序仿真的方式来验证接口信号的建立时间、保持时间是否满足时序要求。但时序仿真存在固有缺点,分析如下:

1)时序仿真对于验证电路时序的正确性在很大程度上依赖于测试向量的完备性,由于测试向量未必对所有相关时序路径都敏感,所以时序路径的覆盖率很难达到100%;

2)基于事件驱动的时序仿真需要耗费大量运行时间,尤其是大规模设计时序仿真耗时较长;

3)针对FPGA在3种工况下的延时文件和布局布线网表进行仿真,进一步增加了时序仿真耗时。

为了提高验证效率和时序验证的准确性,本文提出了一种基于时序路径的FPGA接口测试方法,将被测件的逻辑仿真功能验证和静态时序验证分开,分别采用不同的验证手段加以验证,再将2种验证结果相合进行二次接口时序分析,兼具分析速度快、路径覆盖全和各种工况分析准确的优点。

2 基于时序路径的FPGA接口时序测试方法

2.1 接口时序测试流程

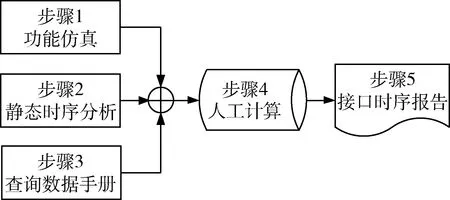

基于时序路径的FPGA接口时序测试流程如图2所示,步骤为:1)执行功能仿真,获得接口信号的无时延波形;2)通过静态时序分析计算接口时序路径延时;3)查询芯片数据手册获得接口信号的协议值;4)人工计算FPGA接口信号的建立时间和保持时间;5)编写接口时序报告。

图2 基于时序路径的FPGA接口时序测试流程

下文先建立FPGA电路时序模型,再阐述使用静态时序分析工具提取接口信号延时以及人工分析接口时序的方法,最后结合实例给出异步接口时序的计算公式。

2.2 时序路径模型

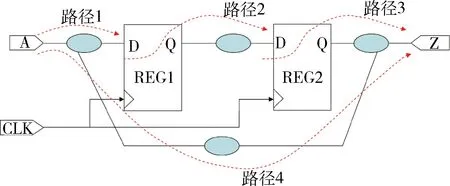

同步时序逻辑的电路可看作由组合逻辑和寄存器相间隔而成,静态时序分析是基于时序路径的,它将整个设计分解为4种主要的时序路径[3],如图3所示。

图3 FPGA时序路径示意图

时序路径的起点只能是设计的基本输入端口或内部时序单元,如寄存器、锁存器的时钟输入端;时序路径的终点只能是内部时序单元的数据输入端或设计的基本输出端口。路径1从FPGA输入引脚到内部寄存器数据端;路径2从内部寄存器时钟输入端到下一内部寄存器数据输入端;路径3从内部寄存器时钟输入端到FPGA输出引脚;路径4从FPGA输入引脚到输出引脚(中间间隔组合逻辑)。功能仿真由于不含有标准延时文件(*.sdf),所以路径1~4的器件延时为0,即FPGA接口信号为理想无延时波形。使用静态时序分析工具(如PrimeTime)可计算出3种工况下各条路径的最大延时和最小延时。

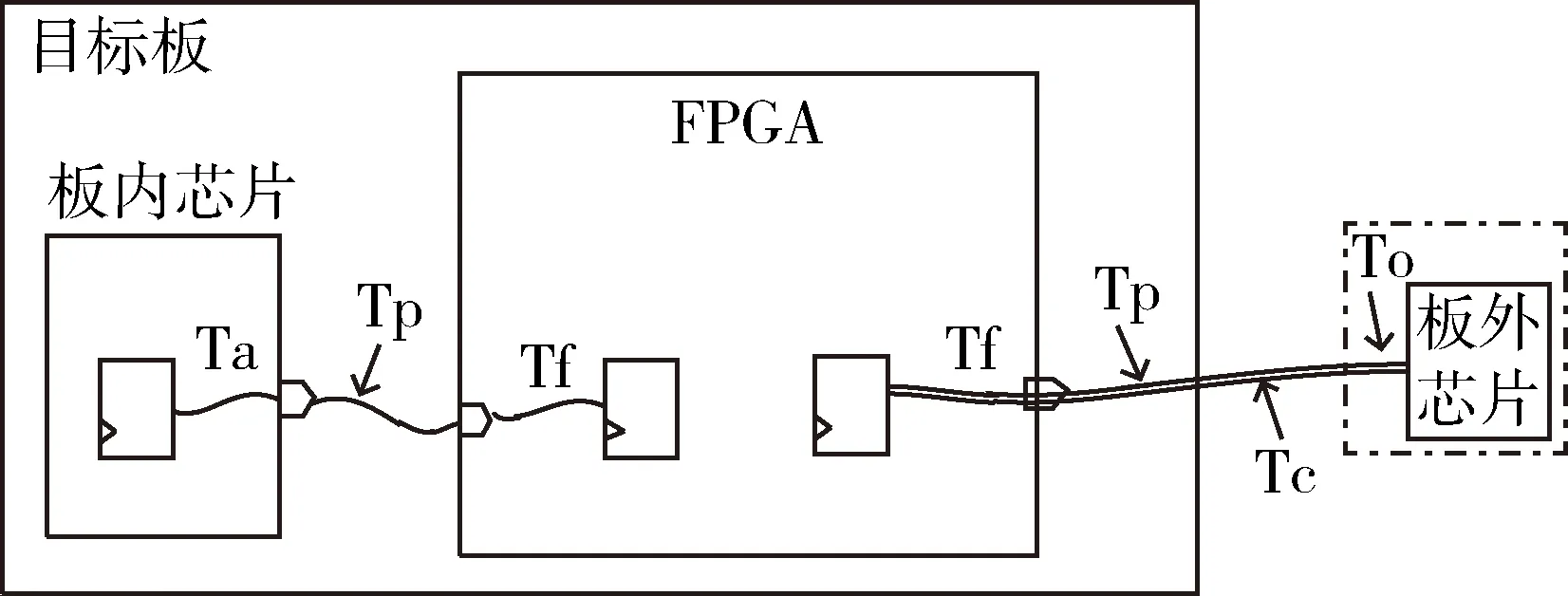

图4 接口延时计算示意图

板内接口是指板级芯片直接与FPGA相连的控制信号接口,如图4所示,这类接口需考虑板内芯片寄存器到引脚的延时Ta、电路板走线延时Tp,FPGA芯片引脚到内部寄存器的延时Tf,其中Ta可由芯片数据手册得到;一般设计中,Tp相对芯片内部延时非常小,可以忽略不计,在超高速设计中,Tp需结合理论值和经验值进行估算。板外接口是指FPGA的输入输出信号经过增强驱动能力的芯片(如422/485差分芯片)或者直接走线到接插件(背板)与其他目标板相连。如图4所示,板外接口需要考虑FPGA芯片引脚到内部寄存器的延时Tf,FPGA芯片引脚到接插件的延时Tp,电缆延时Tc,板外芯片寄存器到接插件延时To。

2.3 通过静态时序分析计算时序路径延时

静态时序分析针对同步电路设计使用穷尽分析方法计算内部路径和外部接口路径的建立保持时间以及纯组合路径的延迟时间,是一种针对大规模门级电路进行时序验证的有效方法。由于不需要编写测试向量,所以静态时序分析验证时间远小于门级仿真时间,测试路径覆盖率理论上可达100%。

作为专门的静态时序分析工具,PrimeTime可以提供完备的时序分析和设计检查。使用PrimeTime验证FPGA时序可分为2个方面:1)内部寄存器到寄存器(即图3的路径2)的时序检查,即对时序逻辑器件和门控时钟进行建立时间和保持时间的检查、对寄存器的清零端和复位端进行恢复时间和移除时间的检查、时钟最小周期和脉宽检查等;2)端口时序检查,计算图3的路径1,3和4的最大延时和最小延时。

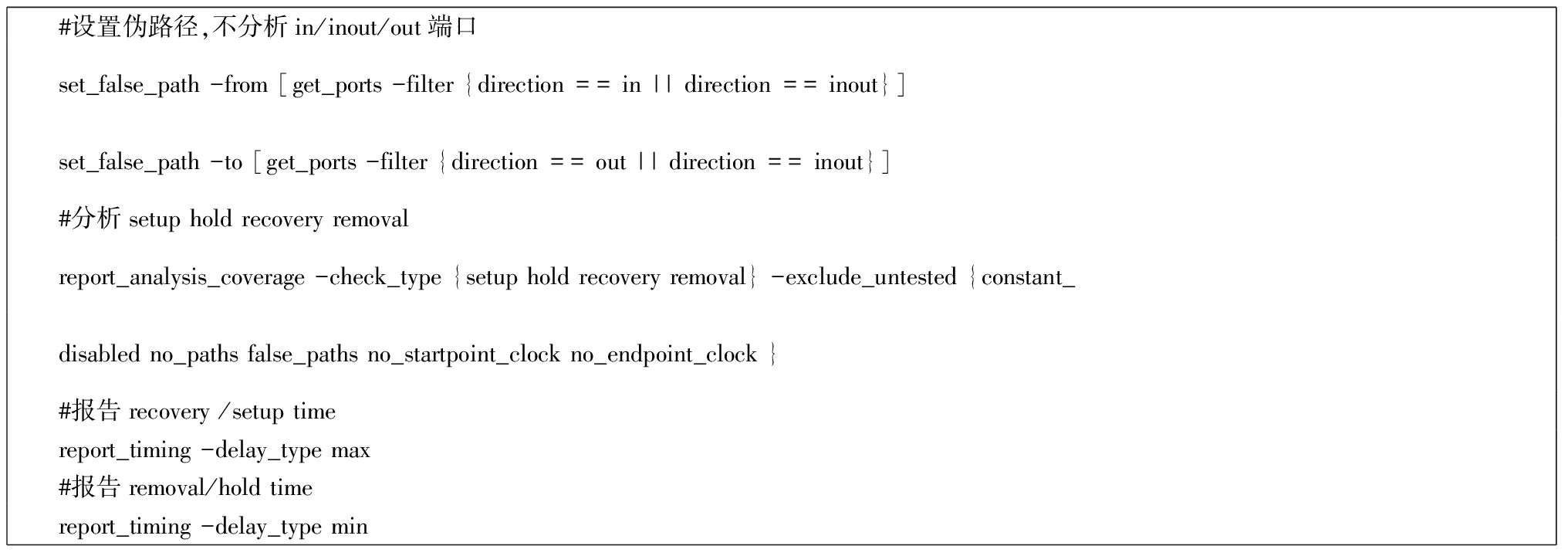

PrimeTime时序检查的脚本说明如下:

1)建立PrimeTime设计环境,包括设置文件路径、读入网表文件和SDF延时文件、链接顶层设计和定义时钟等;

2)执行内部寄存器时序检查,检查寄存器setup/hold/recovery/removal时间是否满足要求,为排出无关路径干扰,可先说明时序例外情况,即将输入输出端口设置成伪路径;

#设置伪路径,不分析in/inout/out端口set_false_path-from[get_ports-filter{direction==in||direction==inout}]set_false_path-to[get_ports-filter{direction==out||direction==inout}]#分析setupholdrecoveryremovalreport_analysis_coverage-check_type{setupholdrecoveryremoval}-exclude_untested{constant_disabledno_pathsfalse_pathsno_startpoint_clockno_endpoint_clock}#报告recovery/setuptimereport_timing-delay_typemax#报告removal/holdtimereport_timing-delay_typemin

3)执行端口时序检查。基于时序路径的接口测试需要人工结合仿真波形分析接口信号是否满足协议要求,作为分析依据,需要使用PrimeTime提取FPGA输入输出信号的端口最大和最小延时。

2.4 基于时序路径的接口时序计算

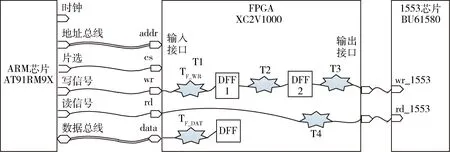

图5 FPGA与ARM总线接口示例

异步接口以图5所示FPGA(XC2V1000)与ARM(AT91RM9200)通信为例,ARM总线输出信号均为ARM时钟域下的同步信号,FPGA采用本地时钟来解析总线信号实现数据读写,本文以ARM写操作为例,对基于时序路径的接口时序计算方法进行详细阐述。

2.4.1 单比特控制信号时序测试

对于输入类控制信号(如图5中ARM总线片选、读写信号),通过跨时钟域检查工具分析逻辑设计是否采取了同步措施(如两级同步),同步后能否保证数据被正确采样。对于输出类控制信号(如图5中FPGA输出1553读、写信号),首先通过静态时序分析计算3种工况下控制信号最大和最小延时(如图5中延时T3和T4),再人工分析输出信号的延时是否在协议值范围内。

2.4.2 异步总线数据建立和保持时间测试

步骤1):执行功能仿真

针对FPGA布局布线后,网表文件执行功能仿真(即门级仿真),测试用例必须覆盖芯片接口的各种操作(如读写操作),从而得出接口信号的无延时仿真波形。由于功能仿真不包含延时文件,因此仿真速度较快。

异步总线接口的同步方式通常是FPGA对关键信号(如读写和片选)进行两级同步,在同步后的关键信号的上升沿或下降沿将数据打入寄存器,将外部异步接口转换成内部同步接口。

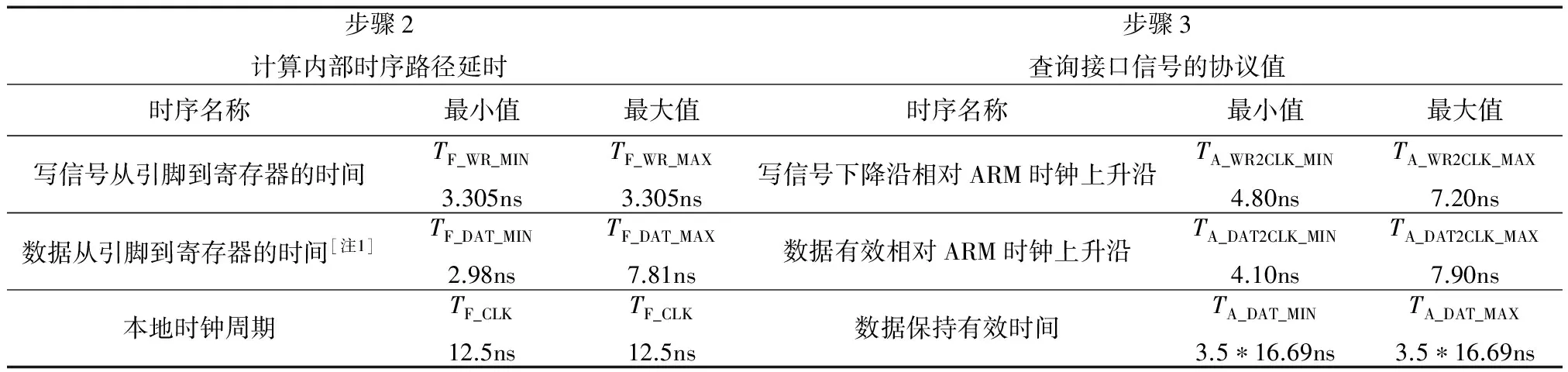

步骤2):计算内部时序路径延时

静态时序分析工具PrimeTime计算FPGA内部时序延时的脚本见2.3节,计算结果见表1。

步骤3):查询接口信号的协议值

查询芯片数据手册可以得到ARM端接口信号相对于ARM时钟的最大和最小延时,结果见表1。

表1 总线接口信号延时

(注1:对于位宽为N比特的数据总线,TF_DAT_MIN为所有数据线延时中的最小值,TF_DAT_MAX为所有数据线延时的最大值。)

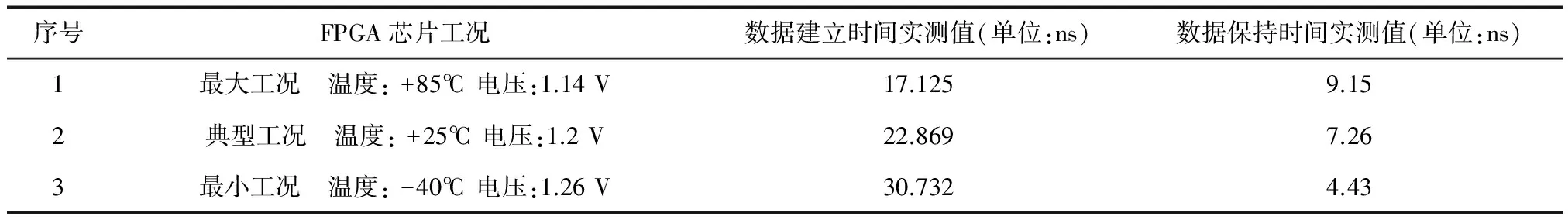

表2 FPGA异步接口时序测试报告

步骤4):人工计算建立和保持时间

人工分析时,首先识别关键信号,即有效时间最短、以该信号跳变沿对数据采样的信号,然后计算关键信号与数据的建立和保持时间。

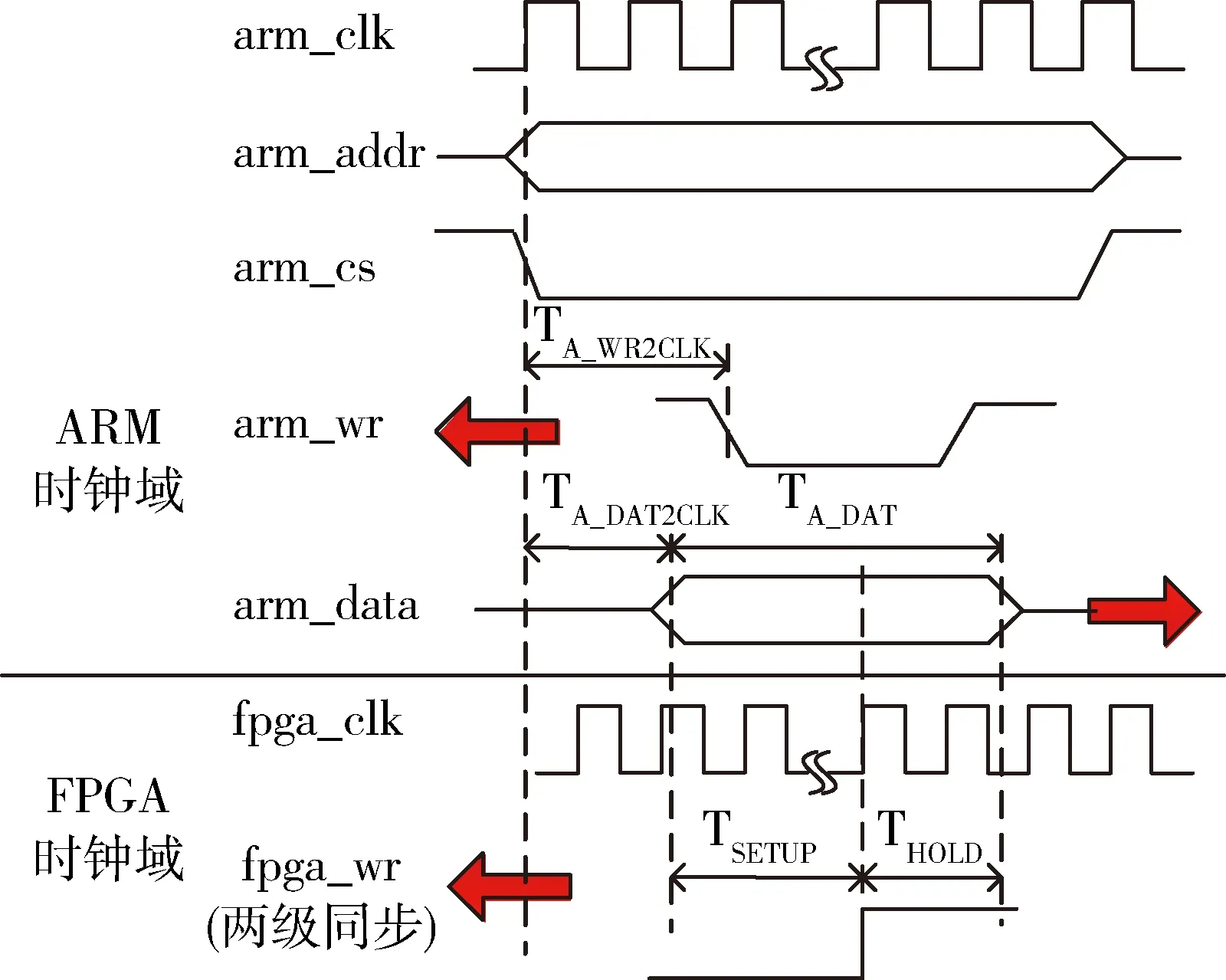

图6 ARM写操作时序图

以图6中 ARM写操作时序为例,地址(arm_addr)和片选(arm_cs)信号持续时间最长,不会出现时序不满足的情况;在本地时钟域下,FPGA对写信号(arm_wr)进行两级同步(fpga_wr),并在其跳变沿对数据(arm_data)采样,所以写信号为关键信号。3种工况下,最大工况(高温低压)对建立时间不利,最苛刻情况下的数据建立时间应该让写信号最早到达,让数据最晚到达。

①总线数据建立时间测试

建立时间TSETUP是指在写信号采样时刻之前数据保持稳定不变的时间,时间基准是ARM时钟沿,时序路径起点是ARM寄存器输出端,终点是FPGA寄存器输入端,包含了ARM输出延时、电路板走线延时和FPGA输入延时,在一般设计中电路板走线延时相对于FPGA芯片管脚到触发器的延时时间来说非常小,可以忽略不计。如图6所示,建立时间应计算经FPGA同步后的关键信号(fpga_wr)的跳变沿与数据总线的时间关系:

TSETUP=T写信号最小延时+T写信号最小同步时间-T数据的最大延时

=(TA_WR2CLK_MIN+TF_WR_MIN)+(N*TF_CLK)-

(TA_DAT2CLK_MAX+TF_DAT_MAX)=(4.8+3.035)+

2*12.5-(7.9+7.81)=17.125nsgt;0 满足要求

注2:N的取值:关键信号与FPGA本地时钟为异步关系,二者相位差为0~1个时钟周期,然后经过内部两级同步在跳变沿对数据进行采样,故N取值2~3。最苛刻情况下让关键信号最早到达,所以对于两级同步,此处N取值为2。

② 总线数据保持时间测试

保持时间THOLD是指在写信号采样时刻之后数据保持稳定不变的时间,其计算同样是基于功能仿真和静态时序分析的结果。与建立时间相反,3种工况下,最小工况(低温高压)对保持时间不利,最苛刻情况下的数据保持时间应该让写信号最晚到达,让数据最早到达,如图6时序所示。

THOLD=T数据最小延时+T数据有效的最小时间-T写信号最大延时-

T写信号同步最大延时=(TA_DAT2CLK_MIN+TF_DAT_MIN)+

TA_DAT_MIN-(TA_WR2CLK_MAX+TF_WR_MAX)-N*TF_CLK=

(4.10+2.98)+3.5*16.69-

(7.20+3.035)-3*12.5=9.15nsgt;0满足要求

注:N取值:与建立时间相反,最苛刻情况下让关键信号最晚到达,所以对于两级同步,此处N取值为3。

步骤5):编写接口时序测试报告

编写接口时序测试报告,如表2所示。接口时序测试需要分析3种工况下的建立时间和保持时间是否为正。

3 应用效果

在集成电路设计中,由于流片费用昂贵,所以其时序分析验证有一套严格的流程和标准。而在FPGA设计或验证中,由于FPGA可反复擦写、烧写速度快,所以常用的测试方法是直接下载到FPGA中进行板级测试,另外由于设计人员或测试人员对时序测试缺乏认识,认为只要时序分析报告没有报错、板间通信正常就代表时序没有问题。这样就存在时序路径覆盖不全面、测试场景不全面从而导致时序错误遗漏,最终在实际应用或高低温实验时引发极限工况下的偶发问题。

基于时序路径的FPGA接口时序分析方法应用于可编程逻辑器件的开发方测试及第三方测试,相比时序仿真,不仅能显著缩短测试时间,而且能分析出最苛刻情况下的接口时序是否满足协议值要求。在多个型号FPGA软件测试中发现如下几类典型问题:

1)复位信号由于扇出较大导致恢复时间或移除时间不满足要求;

2)极限工况下接口信号时序不满足协议值要求;

3)极限工况下内部信号的建立时间和保持时间不满足要求;

4)FPGA管脚约束(如驱动电流、IO标准)不合理,管脚连接中途容性负载反射导致关键信号出现毛刺,造成误操作;

5)FPGA管脚分配不合理导致芯片输出信号延时偏差较大,控制信号不满足协议值要求,总线信号一致性差;

6)跨时钟域信号未采用同步机制。

在设计早期发现接口时序问题能极大地降低电子设备的研制和试验成本,提升系统的可靠性。基于时序路径的FPGA接口时序分析在工程实践中有广泛的应用价值。

4 总结

对航天高速高可靠FPGA接口时序测试进行了深入的分析,提炼出一种基于时序路径的FPGA接口时序测试方法,阐述了接口时序分析的测试流程和计算方法,并应用到多个航天型号FPGA软件测试中。

[1] 王石. 基于FPGA芯片的功能仿真平台构建及静态时序分析[D]. 西安:西安电子科技大学,2008. (Wang Shi.Construction of Function Simulation Platform and Static Timing Analysis Based on FPGA Chips [D]. Xidian University, 2008.)

[2] 周珊,王金波,王晓丹. 基于时序路径的FPGA时序分析技术研究[J]. 微电子学与计算机, 2016,33(1):76-80. (Zhou Shan, Wang Jinbo, Wang Xiaodan. Research of FPGA Timing Sequence Analysis Technology Based on Timing Sequence Path [J]. Microelectronics and Computer, 2016,33(1):76-80.)

[3] 周海斌. 静态时序分析在高速FPGA设计中的应用[J].电子工程师, 2005,31(11):41-44. (Zhou Haibin. The Application of Static Timing Analysis in High Speed FPGA Design [J]. Electronic IC Engineer, 2005,31(11):41-44. )

AnFPGAInterfaceTimingVerificationMethodBasedontheTimingSequencePath

Zhu Weijie, Zhou Hui, Fei Yanan, Yang Hui, Guo Guanjun

Beijing Aerospace Automatic Control Institute, Beijing 100854, China

AimingatthehighspeedandreliableFPGAinterfacetimingsequenceverificationonspaceflight,theFPGAinterfacetypeandtestspecificationisanalyzed,andanFPGAinterfacetimingverificationmethodbasedonthetimingsequencepathisintroduced,andthetestflowandcalculationmethodwhichisbasedonthetimingpathmodelandappliedinthetimingtestofasynchronousbusinterfaceisclarified.TheadvantageoffunctionsimulationwithstatictiminganalysisareintegratedinthismethodwhichissuitableforthetimingverificationoflimitingconditionespeciallyandisappliedinseveralhighreliableFPGAtestingonspaceflight.Bycomparingwiththetraditionaltimingsimulationofgate-level,theverificationefficiencyandcoveragecanbeimprovedbyusingthemethodintroducedinthispaper.

Timingpath; FPGAinterfacetimingsequencetest;Statictiminganalysis

TN47

A

1006-3242(2017)04-0079-06

2016-12-13

朱伟杰(1987-),男,山东威海人,硕士研究生,工程师,主要研究方向为FPGA软件设计与测试;周辉(1984-),男,陕西咸阳人,硕士研究生,工程师,主要研究方向为FPGA软件设计与测试;费亚男(1988-),女,长春人,硕士研究生,工程师,主要研究方向为FPGA软件测试;阳徽(1985-),男,湖南邵阳人,硕士研究生,高级工程师,主要研究方向为FPGA软件设计与测试;郭冠军(1978-),男,河南民权人,硕士研究生,高级工程师,主要研究方向为FPGA软件设计。