基于RAID-5的机载阵列存储技术

2017-11-20陈臻

陈 臻

(中国电子科技集团公司第五十一研究所,上海 201802)

基于RAID-5的机载阵列存储技术

陈 臻

(中国电子科技集团公司第五十一研究所,上海 201802)

在现有的机载环境下,对空中复杂环境的电磁信号的采集记录信息量巨大,往往无法在一次的飞行试验中实时分析所获取的信息。大容量实时信息采集存储的必要性越来越得到重视,在复杂环境中,各个波段的信号混叠预处理之后的数据需要在地面恢复重演。介绍了一种基于COM-E模块+Xilinx K7系列FPGA+RAID控制器+XMC存储模块架构的存储系统,模块化的设计更容易维护和日后升级使用。通过RAID-5的阵列管理方式灵活控制工作模式,提高存储速率。系统的实时写入带宽大于3 GB/s,可以作为机载环境下采集设备后端的高速存储设备广泛应用。

RAID-5;NAND-Flash;机载;高速;阵列存储

0 引 言

当前航空航天技术迅速发展,各种新兴的电子设备被安装于各类机载设备上。这些电子设备用于测量机载设备的参数,会产生大量的需要记录的数据用于记录飞行过程中飞行的工作状态。这些数据的来源多样,产生速率快,数据量大。受制于机载设备本身实时处理能力的局限性,这些数据需要被实时高效地记录下来,返回地面后需要被回收和分析研究。

同时,随着半导体工艺的迅速发展,大规模集成电路的密度越来越高,前端数据采集系统的采集速率、精度、测量范围等性能也大幅提升,高带宽、高速率、多通道已经成为当前机载设备采集系统的主流发展趋势。一款采样速率为1 GHz、采样位数为12 bit的模数转换(AD)芯片,1 s便会产生12 Gbit的数据,要完整记录这1 s内的信号脉内信息,存储速率必须要大于1.5 GB/s。同时机载设备单次飞行的时间长,所记录的空中复杂环境中的信号具有多样性,多频段混叠,能在短时间内产生大量的数据信息。这些特征对机载存储设备的速率和容量都提出了非常严苛的要求。同时,机载设备的飞行成本高,需要在有限的飞行次数中获取尽可能多的数据信息,高性能的存储系统在未来的机载设备中将有着必然的需求。

本文设计了一款基于COM-E模块+Xilinx K7系列现场可编程门阵列(FPGA)+独立磁盘冗余阵列(RAID)控制器+XMC存储模块架构的标准阵列存储系统,采用了RAID-5方式对磁盘阵列进行统筹管理,用于记录机载设备飞行过程中的海量数据。由于采用了CPU架构,通过RAID-5实现文件系统的重构,数据重演过程可以免于导出,可直接通过操作系统对数据进行分析和过滤。

1 设计方案

1.1 数据来源

系统通过标准RapidIO协议作为数据来源总线接口。RapidIO是一种高效的、低引脚数量的高速互连体系架构,传输可靠,硬件成本低,无需专门配置外围电路对其进行支持。

2007年发布的RapidIO2.0协议,速率支持范围从原有的3.125 Gbps基础上,增加了5 Gbps 和 6.25 Gbps 2种速率,最大的信号传输带宽提高到100 Gbps,在4×模式下足以满足机载设备多种来源的数据速率要求。

RapidIO同时对各类微程序控制器(MCU)均有较好的兼容性,FPGA、数字信号处理器(DSP)、 PowerPC均对RapidIO有开放式的IP核或库函数,便于在后期维护和升级。

本设计通过Xilinx(赛灵思)公司Kintex-7 系列FPGA作为RapidIO协议接收和预处理的芯片,将RapidIO转换为PCIe2.0协议并将数据转发至RAID芯片进行进一步处理。

1.2 RAID技术

RAID用于将多个磁盘存储阵列统一管理,可分为RAID0~RAID6等多个等级。选取适当的RAID等级,可以满足用户对存储系统扩展性、读写性能和存储容量的要求。在均衡管理和冗余纠错方面,RAID-5是目前最主流的RAID方式。RAID-5使用其中一个阵列保存校验数据,当整个阵列存储系统某个阵列的数据发生损坏时,可利用余下的阵列和保存校验数据的阵列重新恢复损坏阵列的数据而保证整个存储数据的完整性。机载设备的数据完整性尤为重要,需要完整重演整个飞行过程,RAID-5可很好地保证存储阵列和数据的意外损坏不会发生[1]。

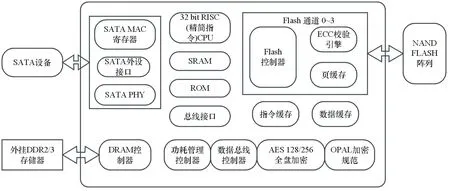

RAID芯片采用了Marvell公司的88RC9580,该芯片将6U VPX载板上自带的4路SATA协议的数据流以及来自XMC存储模块的4路SATA协议的数据流,共8路SATA数据流,组成磁盘列阵,并以PCIe 2.0 ×8的形式和PCIe桥接芯片互相通讯。Marvell 88RC9580原理框图如图1所示。

88RC9580内嵌900 MHz ARM CPU,同时支持最多8 GB DDR2/DDR3内存,全面兼容PCIe 2.0 ×1,×4,×8,支持8个 6 Gbps SATA/SAS接口,支持SSP/SMP/STP/Wide port形式的SAS接口,能够很好地支持RAID-5方式的管理模式。

利用CPU通过PCIe接口直接对88RC9580进行RAID方式的配置和阵列管理,可以方便地在操作系统上对文件进行数据维护和管理。

1.3 NAND Flash闪存控制

以往的闪存控制多采用MCU直接控制的方式,通过直接对NAND Flash进行读写操作的方式进行管理,这种方法的管理算法复杂,效率低下。且由于每片NAND Flash芯片的自编程操作时,内部CACHE在缓冲数据时,无法对其进行任何操作。如要提高工作效率,需对整个磁盘阵列进行流水线的读写操作,即在第1组阵列的缓冲过程中,在第2组阵列进行数据操作,进行多阵列的联协操作。在需要进行容量扩展或速率的升级时需要颠覆原先的流水线阵列的结构,不便于维护[2]。

本设计选用了Silicon Motion闪存主控芯片SM2246EN。该芯片专用于对NAND Flash的直接操作控制。SM2246EN原理框图如图2所示。

SM2246EN超高连续读取速率可达540 MB/s,持续写入速率可达490 MB/s,同时先进的错误矫正(ECC)管理可以有效地增加数据的可靠性,支持先进的Toggle、ONFI及Asynchronous NAND算法。每片SM2246EN建立一个NAND Flash阵列,通过SATA接口与RAID芯片进行通讯,多个SM2246EN建立的多阵列维护的工作交给RAID芯片来完成,可以最大程度地减轻CPU的工作负荷。本设计使用了8片SM2246EN、每组外挂12片NAND Flash的方式,采用多组阵列的方式既保证了数据位宽,又为NAND Flash的流水操作保证了空间上的阵列数量。

图1 Marvell 88RC9580原理框图

图2 SM2246EN原理框图

1.4 系统架构

目前主流的存储系统的架构主要分为FPGA+NAND Flash阵列、FPGA+DSP+NAND Flash阵列、FPGA+CPU+NAND Flash阵列,其中第1种FPGA直接控制阵列的方式,管理算法复杂,且没有文件系统,无法直接对存储系统进行有效的管理,需要配置地面大容量的记录仪等卸载设备;第2种架构加上DSP后对信号处理的能力增强,但对阵列的管理依然要通过FPGA进行;第3种通过CPU模块加上操作系统可以增强对文件系统的管理,且FPGA丰富的对外接口可以分担CPU在数据传输方面的负荷,也可以进行一部分的预处理[3]。

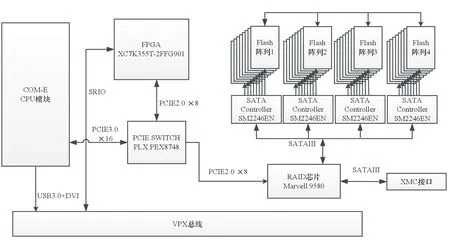

阵列存储的设计原理框图如图3所示,该设计选用第3种架构,利用Xilinx(赛灵思)公司Kintex-7 FPGA作为协议转换通道,将RapidIO协议转换为PCIe协议。PLX公司的PEX8748芯片作为PCIe桥芯片,可以在PCIe2.0/3.0协议中切换,对整个系统内部的数据流进行有效综合,使CPU、存储阵列和采集数据源之间的数据得以互相访问。选用的COM-E模块自带INTEL I7 CPU及其外围电路,自带操作系统可进行后期平台开发,应用软件用于分析数据。

图3 6 U 阵列存储系统设计原理框图

2 软件实现

2.1 FPGA软件

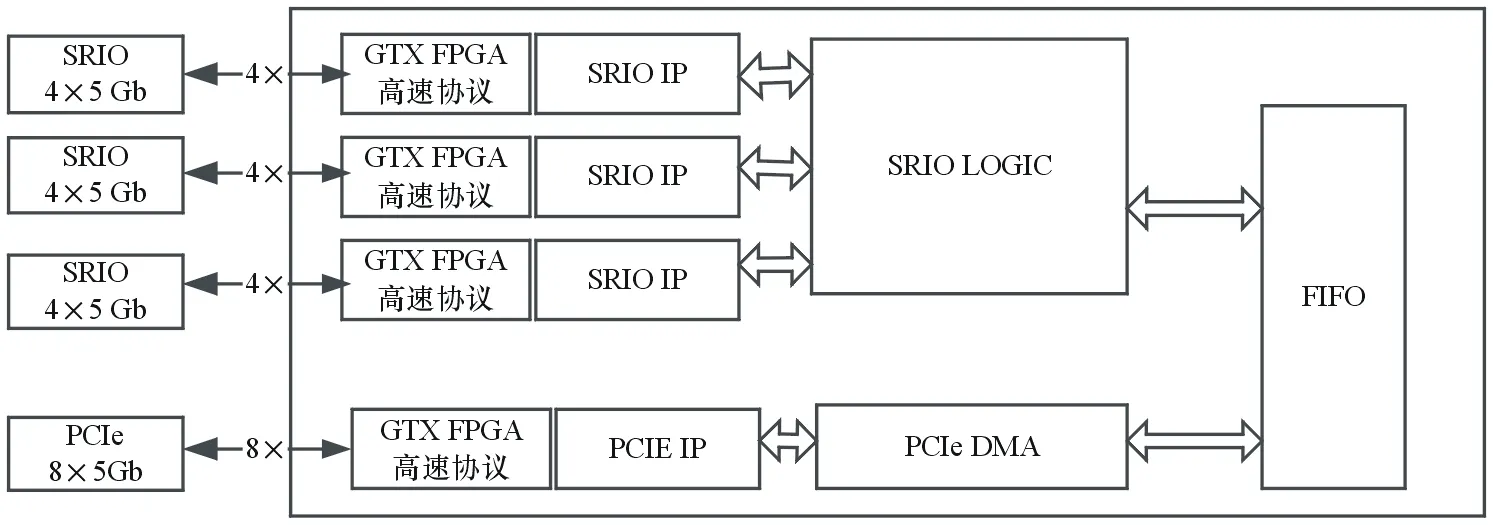

利用Xilinx RapidIO解决方案实现RapidIO网络中FPGA上的RapidIO节点。FPGA原理功能框图如图4所示,利用Xilinx RapidIO的GTX接口进行数据的交互,对外具有4个4×RapidIO的5 Gbps的通道。通过RapidIO IP将高速串行信号转换为并行数字信号,将数据转发入RapidIO LOGIC模块进行预处理。

图4 FPGA 原理功能框图

RapidIO 逻辑分为2个子模块,分别为CLK MODULE 和RapidIO TOP。CLK MODULE为时钟模块,将外部时钟的输入转换为合适的时钟;RapidIO TOP模块完成RapidIO 协议的实现,分为3个子模块:RAPIDIO CORE、REQUEST MODULE 和RESPONSE MODULE。各模块对应功能如下:RAPIDIO CORE,实现对RapidIO 的IP 例化;REQUEST MODULE,实现RapidIO 的命令请求发送;RESPONSE MODULE,完成RapidIO 的命令接收解析。RapidIO逻辑架构如图5所示。

图5 RapidIO LOGIC逻辑架构图

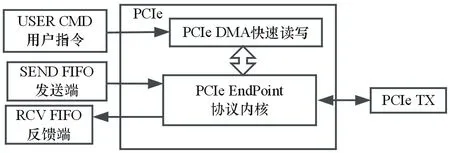

PCIe 逻辑设计主要分为5 个子模块[4],分别为PCIe Endpoint、PCIe DMA、USER CMD、SEND FIFO和RCV FIFO,各模块对应功能如下:PCIe Endpoint,为封装的PCIe 协议内核,完成PCIe 协议的链路层和传输层;PCIe DMA,完成PCIe 协议的事务层,并可以直接进行向上位机内存空间进行数据读写;USER CMD,用于产生控制指令;SEND FIFO,接收来自DDR 的数据暂时缓存,并准备送入PCIeEndPoint;RCV FIFO,接收来自PCIeEndPoint 的数据暂时缓存,并准备送至DDR。PCIe逻辑架构框图如图6所示。

图6 PCIe逻辑框图

2.2 RAID-5控制

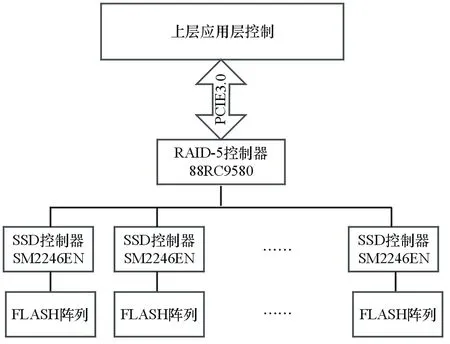

COM-E板载CPU通过PCIe接口对88RC9580进行控制,可以采用RAID-5方式对磁盘阵列进行管理。Marvell官网提供的动态链接库(DLL)可对88RC9580进行RAID方式的配置和错误检查及纠正(ECC)校验算法的设置,通过ONFI机制高效控制管理NAND Flash阵列。

COM-E模块基于X86架构,在Windows操作系统可以更直观地对磁盘阵列进行可视化的管理。图7显示了RAID-5方式对Flash阵列进行控制的软件框架结构,其中CPU实现了上层应用层的控制,也就实现了对整个Flash阵列的控制[5]。

图7 RAID-5控制框架

对RAID-5控制器的访问操作一共可分为5个步骤:

(1) 打开PCIe总线端口,建立起所有端口的拓扑结构。由于本设计中的RAID-5控制器和FPGA端口均有PCIe端口,选择0号端口对RAID-5控制器进行配置。

(2) 通过Marvell官方提供的API函数raid_request_channel申请RAID通道。

(3) 通道开启后,需要对CPU的内存数据及传输数据的CACHE进行申请。当存储模块高速工作后,对CPU和内存的占用会达到一个较高比率,通过raid_alloc_coherent函数对资源进行预先申请,可使CPU处于待接收数据的状态。

(4) 对传输数据的分包大小进行设置,每存满一个4 GB的文件建立一个新的文件。选择4 GB大小可方便对数据进行导出操作时,满足接收方FAT32文件系统最大接收的单个文件大小。

(5) 完成分包的设置后,将文件分包的描述符挂载至RAID控制器的PCIe端口,利用raid_async_send函数完成数据的传输。当一帧数据完成传输后会产生一个中断,进入中断处理。在中断处理的过程中,内存会开启一个缓存来接收下一帧数据,步骤(2)中的CACHE开启的大小决定着内存对于突发数据流的缓冲帧数的大小。完成一帧数据的传输后会自动从内存中取得下一帧数据,继续传输直至清空内存中用于RAID通道开启的CACHE。单帧操作的流程图如图8所示。

图8 RAID-5操作流程图

3 速率分析

数据传输的速率为机载存储设备最重要的指标,直接影响到数据采集的带宽和完整性。故在设计初期对存储速率的分析显得尤为重要。

流水线技术是提升存储速率的关键技术,可以避免存储芯片内部CACHE进行缓存工作时浪费大量时间。具体而言,流水线技术是一种在空间上并行执行、时间上重叠执行的操作,其基本理论为将一个任务t拆分成为若干个子任务t1,t2,…,tm,一旦t1完成,后继的子任务就可以立即开始,并以同样的速率进行运算。

记录一条存储信息定义为一个任务,第k个任务用Tk表示,每个任务需要M个过程,则:

(1)

图8为NAND Flash的操作流程,tCBSY为芯片内部的页编程操作,充分利用该时间对编程时间进行流水操作,可以大幅度地提高写入的速率。即对一组阵列进行操作时,在tCBSY这段时间内不能对其进行其他任何操作,但可对另一组阵列进行操作。每个Flash本身包含4个target,自流水级别即可达8级。加上硬件设计时采用的多阵列设计,本设计的流水操作最大可达32级。N级流水操作原理如图9所示。

图9 N级流水操作原理

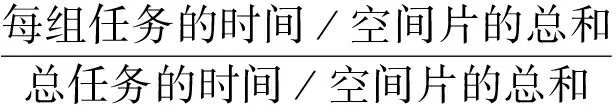

每条指令执行时间均为τ=max{ti},即一级流水操作中最慢的时间,对Flash芯片而言即为芯片自编程时间。如果在这个时间间隔内,对需要处理的其他Flash阵列进行流水操作,则:

(2)

式中:n为流水级数;L为第1组任务工作忙的时间间隔内通过流水的任务数。

假设进行4级流水操作,L取值不同的条件下:n=4,L=10时,η=0.77;n=4,L=20时,η=0.87;n=4,L=30时,η=0.91。

可以看出,流水段数一定的情况下,增加任务数L可以提升流水线的效率,使效率η→1。

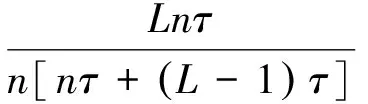

衡量存储速率的另一个重要指标是吞吐率,它表示单位时间内处理的任务数量,通过提高吞吐率,可提高流水线任务的处理能力。定义为:

实施一个任务所需要的时间=1/吞吐率

流水线任务的吞吐率P为:

(3)

随着流水线的效率提高,其吞吐率也会随之提高。

本设计中一个存储阵列由4片Flash组成,根据图8,进行四plane(叠层)操作时,若进行4级流水,本系统写入速度为(并联芯片数×流水线级数×页大小×页个数) /(加载时间+写入编程时间)=(4×4×8 640×4) Byte /(90+1 300) μs=396 MB/s,若进行极限32级流水,则读取速率可达3 168 MB/s,即存储速率可超过3 GB/s。

根据前端信号来源的分类特征,本设计需要对前端1 GHz采样率的12位AD芯片采样的原始数据进行录取,单路AD的存储速率为1.5 GB/s,加上飞行过程中产生的状态信息,在RapidIO通道上产生的有效数据的速率约为1.8 GB/s。RapidIO2.0的数据开销后的打包效率约为92%,即对该设计的最低的存储速率要求为2 GB/s。通过32级流水操作足以满足系统对存储功能的要求。

4 系统验证及性能测试

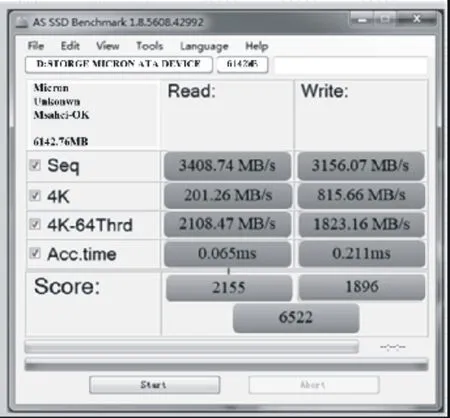

在COM-E模块的WIN7系统上安装存储速率测试软件AS SSD Benchmark对整个6 TB的存储阵列进行速率测试,得到的性能测试结果如图10所示。

图10 AS SSDBenchmark

可以看到,持续的读写速率均超过了3 GB/s,通过对固定数据的读写对比测试,对1 TB的文件进行的24 h持续操作对比试验,数据误码率低于10-13。

5 结束语

本文介绍了一种针对航空机载设备的阵列存储技术,改变了以往机载存储设备对文件管理系统方面的缺失性。通过FPGA的对外接口资源进行协议转换,利用高性能的CPU通过RAID-5方式对阵列进行统筹管理。该技术具有以下特点:

(1) 对逻辑资源的分配进行优化,将有限的CPU的逻辑资源充分用于文件系统的建立和海量数据的维护。

(2) 合理分配存储阵列构成的空间结构,对流水操作的数量和数据位宽进行综合考虑,充分提高流水线效率。

(3) 通过硬RAID的方式,利用RAID-5方式减少资源开销,保证数据的纠错机制,实现对阵列数据完整性保障及数据损耗的恢复功能。

(4) 存储阵列的32级流水模式大幅增加了单个存储阵列的吞吐率,有效提升了存储速率,也节省了芯片使用的数量。

单块存储阵列的存储容量达到了6 TB,存储和回访的速率均超过3 GB/s,在更大带宽和速率的需求下可以方便扩容并联使用,能够充分保证机载环境下数据的高吞吐率和数据重演的要求,也可以作为一种通用的存储系统应用于各种航空航天设备。

[1] 董永帅.Flash文件系统及存储管理技术研究与实现[D].武汉:华中科技大学,2008.

[2] 潘旭明.基于NAND Flash的存储设备设计与实现[J].无线电通信技术,2017,43(4):91-95.

[3] 彭振翼.固态存储系统PCIe接口的设计方法与实现[D].武汉:华中科技大学,2013.

[4] 步凯.基于RAID技术的固态存储阵列系统的研究与设计[D].长沙:国防科技大学,2008.

[5] 张元凯.基于PCIe和RAID5的高速存储系统设计[D].北京:中国科学院,2010.

AirborneArrayMemoryTechnologyBasedonRAID-5

CHEN Zhen

(51st Research Institute of CETC,Shnaghai 201802,China)

In the existing airborne environment,the information collection and record quantity of electromagnetic signals in complex air environment is huge,and it is often impossible to analyze the acquired information in real time in one flight test.The necessary for large-capacity real-time information acquisition and storage is getting more and more attention.In complex environment,the data after preprocessing of each band's signal are needed to be resumed on the ground.This article describes a storage system based on COM-E module + Xilinx K7 series FPGA+RAID controller+XMC storage module architecture,and modular design is easier to be maintained and upgraded for the future.The array management of RAID-5 is used to flexibly control the working mode and improve the storage rate.The real-time write bandwidth of the system is greater than 3 GB/s,and it can be widely used as a high-speed storage device at the back of acquisition equipment in airborne environment.

RAID-5;NAND-Flash;airborne;high speed;array memory

TP333

A

CN32-1413(2017)05-0074-07

10.16426/j.cnki.jcdzdk.2017.05.016

2017-08-23