基于FPGA的VME总线多串口实验设计

2017-11-01张士辉

王 鹏, 张士辉, 琚 静

(甘肃交通职业技术学院 信息工程系, 甘肃 兰州 730070)

职业技术教育

基于FPGA的VME总线多串口实验设计

王 鹏, 张士辉, 琚 静

(甘肃交通职业技术学院 信息工程系, 甘肃 兰州 730070)

将现场可编程门阵列技术与VME总线技术相结合,运用VHDL语言编程实现多波特率、多数据位、多停止位的多种类别、不同数量的串口,有益于培养学生的知识应用能力,提高工程实践能力,全面掌握串行通信技术。这种实验设计方式有效地实现了教学内容与生产现场实际需求的对接,扩展了实践教学的深度与广度。

多串口实验; 实验教学; FPGA; VME

串行通信接口因具有支持多种通信协议、传输距离远、抗干扰性强等特点在工业控制领域得到了广泛应用。在高等职业教育的“微机原理与接口技术”和“单片机原理及接口技术”课程教材中,只涉及到单一的串行通信模式。然而在实际的工业应用中,现场通常需要有多个串口的主控制器与多个现场从设备通过RS232、RS422、RS485等多种串行通信模式进行通信[1]。因此,将FPGA技术与通用模块VME背板总线技术相结合[2],通过VHDL语言编程实现多种类别、不同数量、不同模式的串行接口,创新实验设计,对培养学生的综合应用能力,灵活掌握串行通信知识将大有裨益。

1 实验硬件平台设计

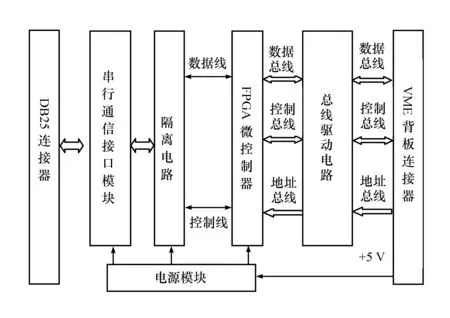

实验硬件平台主要包括DB25连接器、串行通信接口模块、隔离电路、FPGA微控制器、总线驱动电路、VME背板连接器、电源模块,如图1所示。

DB25连接器通过串行通信接口模块与基于FPGA的VME总线多串口卡进行通信;FPGA微控制器接收来自VME总线主模块的指令,配置本地控制寄存器;FPGA微控制器与串行通信接口模块之间通过光耦进行隔离,控制多个串口收发模块发送和接收串行数据。实验平台中采用光耦隔离模块构成的隔离电路,以降低外界电磁的干扰[3]。FPGA微控制器通过总线驱动电路与VME总线主模块之间实现数据交互。串行通信接口模块用于实现不同通信方式之间电平转换[4]。VME总线主模块通过设定FPGA内部的状态寄存器改变UART的工作参数,如波特率、停止位和数据帧结束标志等,实现多种串口工作模式[5]。

图1 基于FPGA的VME总线多串口实验框图

2 实验软件系统设计

2.1 基于FPGA的多串口实现

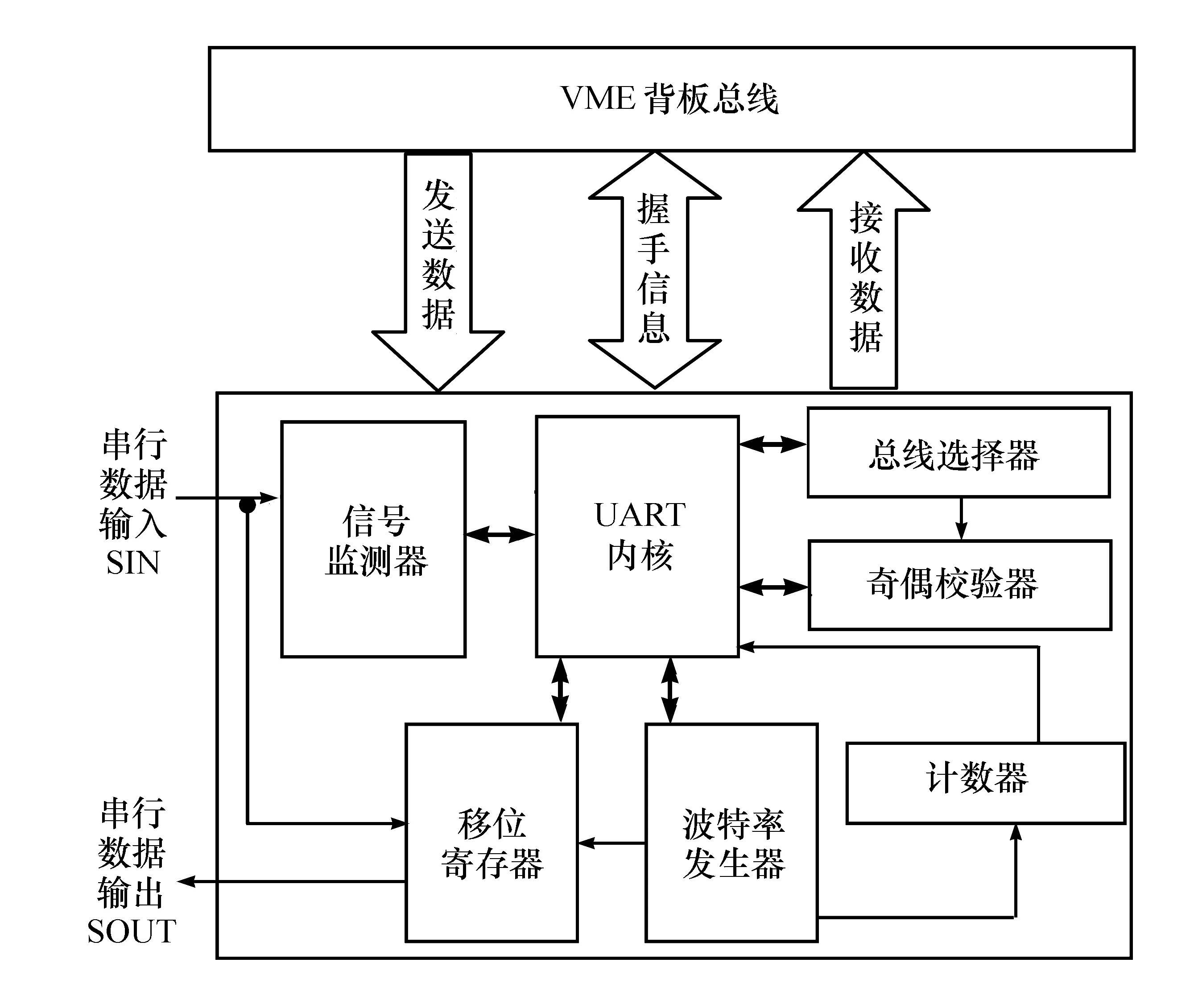

基于FPGA的多串口,主要通过VHDL语言编程实现内核、移位寄存、信号监测、波特率产生等功能模块[6],如图2所示。

图2 基于FPGA实现的多串口框图

多串口内核模块是系统实现的核心。

在接收过程中,信号监测模块实时监测串行接口上的信号,当有新数据出现时立即通知内核模块[7]。移位寄存器在内核模块的控制和波特率发生器的驱动下,同步接收并保存端口上的串行数据。

在发送过程中,内核模块依据发送数据的格式要求产生待发送序列,移位寄存器在波特率发生器的驱动下,将存储在内部的数据串行输出。波特率发生器根据波特率保持寄存器中设定的数值,以32倍波特率时钟频率产生时钟信号实现精确采样,完成数据同步。

计数模块用于统计串行通信过程中数据传输的数目,并向内核模块反馈。总线选择器根据数据收发的不同状态选择对应的总线接入奇偶校验模块,通过组合逻辑电路实现奇偶校验位的检查和添加。

2.2 信号监测处理流程设计

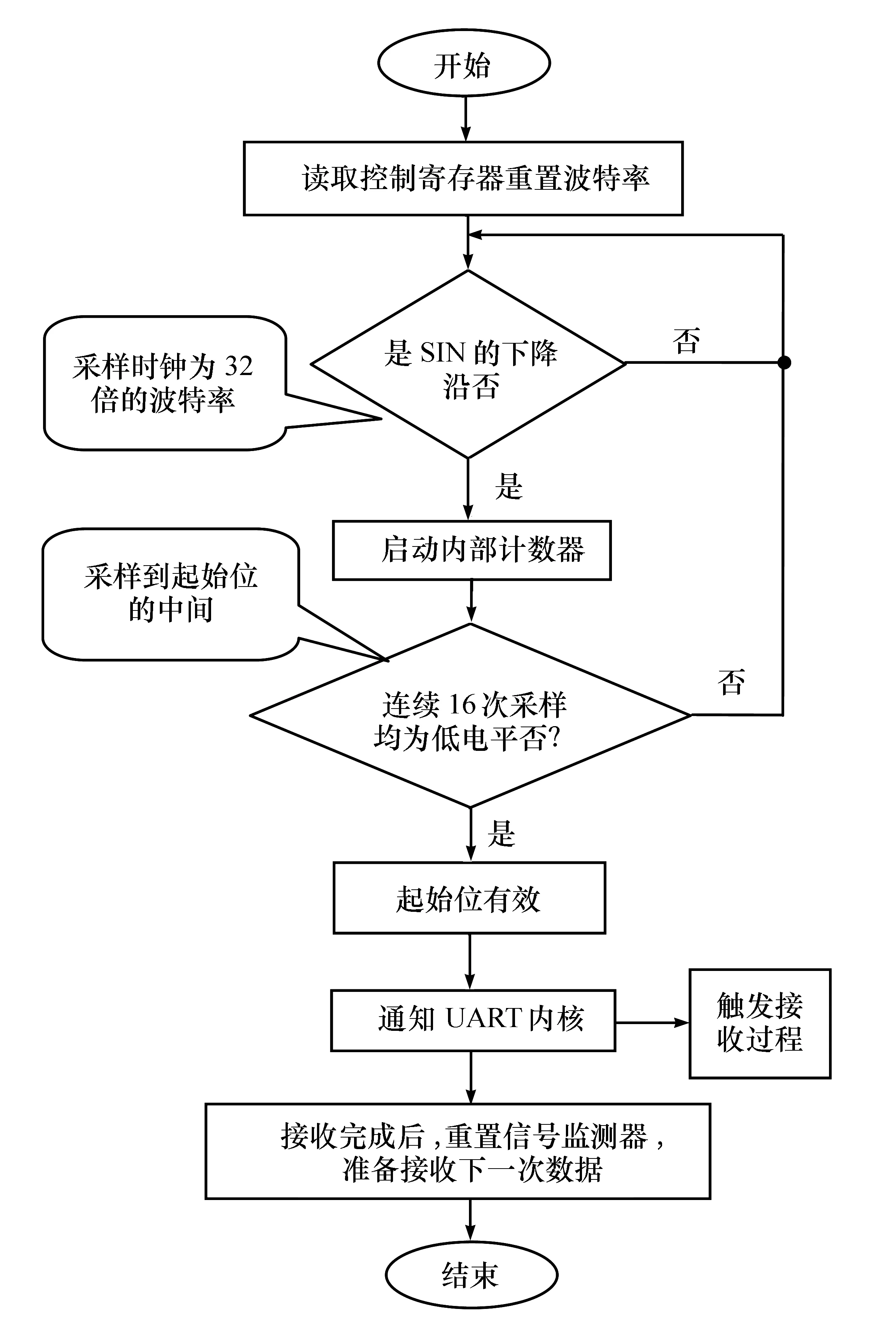

信号监测模块读取控制寄存器中的参数,以32倍的波特率设置采样时钟,并检测SIN线上的数据。为防止接收过程中发生误判,只有在时钟信号的上升沿到来时,SIN线上连续采样出现16个低电平,才判定为正确的起始位,然后信号监测模块通知内核,触发接收过程,开始接收数据[8],否则重新寻找新的起始位。正常接收过程开始后,在每位数据的中间位置采样SIN线,并把采样结果以移位方式送入移位寄存器。接收完毕后,重置信号监测模块,准备开始接收下一组数据[9]。

信号监测模块数据处理流程如图3所示。

图3 信号监测数据处理流程图

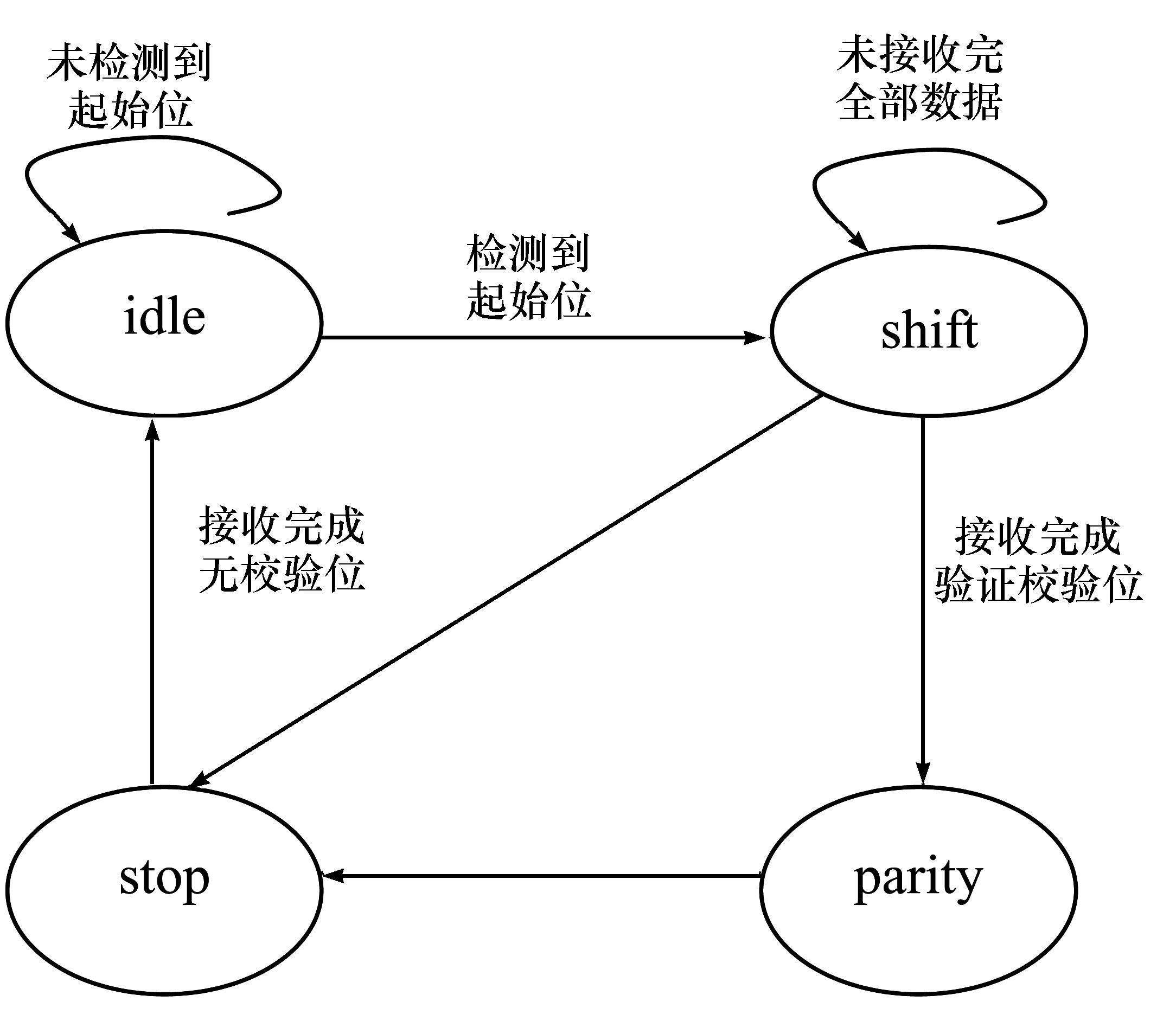

2.3 内核模块数据接收的状态机实现

内核模块数据接收通过一个包含idle(空闲)、shift(数据接收)、parity(奇偶校验位接收)以及stop(停止位接收)4种状态的状态机实现,如图4所示。状态机通过判定转换条件(未检测到起始位、检测到起始位、未接收完全部数据、接收完成无校验位、接收完成验证校验位)的成立,来实现各状态之间的转换,例如,若状态机当前处于shift状态,当条件“接收完成验证校验位”成立时,状态机转入parity状态,完成该状态下的操作。在数据接收过程中,接收电路对接收数据的有效性和接收过程进行检查和监测,若发现停止位错误时,数据将被自动丢弃[10]。

图4 内核模块接收状态机状态转换图

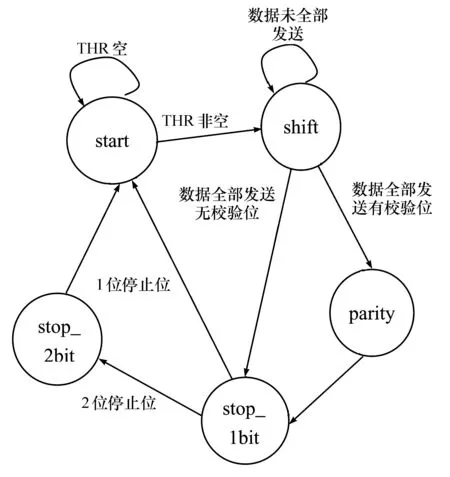

2.4 内核模块数据发送的状态机实现

内核模块数据发送过程通过一个包含start(起始位发送)、shift(数据位发送)、parity(奇偶校验位发送)以及stop_1bit(1位停止位发送)、stop_2bit(2位停止位发送)共5种状态的状态机实现,如图5所示。通过判断转换条件(THR空、THR非空、数据未全部发送、数据全部发送且有校验位、数据全部发送且无校验位、1位停止位、2位停止位)的成立,来实现各状态之间的转换,完成起始位、数据位、奇偶校验位以及停止位的发送。例如,若状态机当前处于shift状态,一旦“数据全部发送有校验位”条件成立时,状态机即转入parity状态,执行该状态下的操作。

图5 内核模块发送状态机状态转换图

3 仿真实例分析

基于FPGA的VME总线多串口实验验证过程如下。

多串口将接收到的串行数据存入缓冲区,遵循先来先发的原则将各个串口的数据进行串并转换,并根据数据发送格式的要求进行发送。上位机接收到来自多串口的信号后,确定数据来源于哪一个串口,对数据译码处理并进行显示。通过上下位机相互发送数据,进行误码率测试[11],可以验证多串口通信及逻辑处理功能达到实验预期目标。

4 结语

基于FPGA的VME总线多串口实验,将现场可编程门阵列技术与VME总线技术相结合,使得学生可以有效地扩展和实现已经学习过的串行通信知识。该实验能很好地融合数字电路、微机原理与接口技术、硬件设计语言等课程知识,既有利于学生对理论知识的学习与掌握,也有利于培养学生对知识的应用能力[12],对于学生创新能力与工程实践能力的提高将会发挥积极的作用。

References)

[1] 江朝晖,陆元洲,王鹏.电子系统设计中常用串行接口及其应用[J].教育教学论坛,2016(50):50-52.

[2] 韩记晓,万勇利,张常江,等.基于FPGA的VME自定义总线接口设计[J].自动化技术与应用,2016(4):103-106.

[3] 康华光.电子技术基础:模拟部分[M].6版.北京:高等教育出版社,2013.

[4] 刘先博.基于FPGA与MCU的多串口通信接口设计与实现[D].南京:南京理工大学,2014.

[5] 陈媛,王再英,彭倩,等.基于嵌入式多串口数据传输系统的设计与实现[J].科学技术与工程,2013,13(1):183-187.

[6] 唐明.基于FPGA与PC机串行通信UART模块设计[D].武汉:华中师范大学,2013.

[7] 吕国成,杨延军,王志军.基于BeagleBone的嵌入式教学平台研制[J].实验技术与管理,2016,33(3):151-153.

[8] 王昱煜,张杰,侯大勇,等.基于FPGA的UART模块设计[J].电子技术与软件工程,2016(7):126-127.

[9] 党俊博,李哲,李雅俊.基于FPGA的串口通信电路设计与实现[J].电子科技,2016(7):106-109.

[10] 贾亮,冀源.基于FPGA的串口通信控制器设计[J].微型机与应用,2016(22):33-35.

[11] 李盛杰.UART测试技术研究[J].计算机与数字工程,2017(3):598-602.

[12] 严文娟,贺国权.基于PSPICE的二阶压控电压源低通滤波器仿真实验研究[J].实验技术与管理,2017,34(2):101-104.

Design on experiment of VME bus multi-serial ports based on FPGA

Wang Peng, Zhang Shihui, Ju Jing

(Department of Information Engineering, Gansu Vocational and Technical College of Communications, Lanzhou 730070, China)

In combination of the field programmable gate array technology and the VME bus technology, the innovation of the serial communication experimental design is realized. By using the VHDL programming language, the multi-baud rate, multi-data bits, multi-stop bits of various categories, the different number of serial ports are achieved, which is beneficial to train the students’ knowledge application ability and improve their engineering practical ability, and is helpful for the students to master the serial communication technology comprehensively. This design method effectively realizes the connection of the teaching content to the actual demand of the field production, and expands the depth and breadth of the practical teaching.

experiment of multi-serial ports; experimental teaching; FPGA; VME

TP23

A

1002-4956(2017)10-0143-03

10.16791/j.cnki.sjg.2017.10.035

2017-05-23

甘肃省高等学校科学研究项目(2015A-200);2016年度甘肃省高等教育内涵发展创新创业教育教学改革研究项目(2016Y-37);甘肃交通职业技术学院科学研究项目(2015Y-03)

王鹏(1978—),男,甘肃华亭,硕士,工程师,主要研究方向为计算机控制、嵌入式系统应用和物联网应用技术.

E-mail:systemview@126.com