UART波特率发生电路设计

2010-09-05赵琳娜李红征

赵琳娜,赵 煌,李红征

(1.江南大学信息工程学院,江苏 无锡 214036;2.中国电子科技集团公司第58研究所,江苏 无锡 214035)

UART波特率发生电路设计

赵琳娜1,赵 煌1,李红征2

(1.江南大学信息工程学院,江苏 无锡 214036;2.中国电子科技集团公司第58研究所,江苏 无锡 214035)

设计了一种基于“ATD+迭代法”的UART波特率发生电路。波特率发生电路中的ATD电路用于监测串行数据的变化,并在串行数据的边沿(上升沿或下降沿)输出低电平信号。波特率探测电路对ATD电路的输出信号的低电平和高电平分别进行计数,该计数值和保持寄存器中存储的最小值比较,若前者小于后者,则保存寄存器中的最小值被该计数值取代,若前者大于后者,则保存寄存器中的最小值不变。经过一段时间比较迭代,最终得到设计需要的最小值,从而通过波特率发生器正确地输出串行数据的波特率。

通用异步收发器;波特率发生电路;ATD电路

1 UART设计概述

UART(Universal Asynchronous Receiver/Transmitter)通用异步收发器是用于控制微机系统(并行设备)与串行设备通信的芯片。

UART提供以下主要功能:发送功能(将由微机系统内部传送过来的并行数据转换为串行数据流输出,并在输出的串行数据流中加入奇偶校验位和启停标记),接收功能(将微机系统外部来的串行数据转换为字节供微机系统内部并行数据的器件使用,并对接收的数据流进行奇偶校验、删除启停标记)。

UART的异步收发是指在UART协议中,接收、发送数据不使用统一参考时钟,收发双方取得同步的方法是采用固定的串行数据格式,即通过在串行数据流中加入启停标记位来实现同步。串行数据格式如图1所示。

起始位:发出一个逻辑“0”的信号,表示传输字符的开始;数据位:紧接着起始位,其位数可以是5~8位;奇偶校验位:数据位后加上这一位,使得“1”的位数为偶数(偶校验)或奇数(奇校验),以此来校验数据传送的正确性;停止位:是一个字符数据的结束标志,可以是1位、1.5位、2位的高电平;空闲位:处于逻辑“1”状态,表示当前线路上没有数据传送。

2 “ATD+迭代法”的基本思想

UART链接典型的串口波特率有9600bit/s、19.2kbit/s、38.4kbit/s、57.6kbit/s和115.2kbit/s等。传统的UART在传输数据前,发送端与接收端需要事先协议好传输的波特率,而自适应UART可以通过“迭代法”正确地探测出串行数据的波特率[1]。

“迭代法”基本原理如图2所示。d表示串行数据中的一个下降沿,u表示紧接着下降沿d的一个上升沿,t表示相邻边沿d和u之间的时间间隔,等于一个或多个比特位的周期。采样计数器在下降沿d处开始从初始值0计数,每遇到系统时钟的上升沿递增一次,并在上升沿u处停止计数,得到的计数值和在保持寄存器中存放的所谓“最小值”比较,如果该计数值小于“最小值”,那么寄存器中“最小值”将被该计数值取代,通过不断地迭代,最终得到一个最小值。通过串行线路波特率的计算公式:波特率(bit/s)=系统时钟频率/min值,从而得到准确的串行数据波特率。

这种“迭代法”采用了简单固定的方法来计算波特率,即通过迭代计算出相邻下降沿和上升沿之间的“最小值”。不难发现,这种方法忽略了相邻上升沿和下降沿之间存在的“最小值”,加大了计算波特率的时间。我们提出一种快速有效地计算波特率的方法——“ATD+迭代法”,这种方法兼顾了相邻边沿(相邻下降沿和上升沿以及相邻上升沿和下降沿)之间存在的“最小值”。从理论上讲,“ATD+迭代法”的检测速度是“迭代法”的2倍。

“ATD+迭代法”的基本想法是:第一步,通过ATD电路监测串行数据的变化;第二步,通过波特率检测电路对ATD电路的输出信号进行迭代,最终得到最小值。

图3为ATD电路的输入信号RXD和输出信号ATDD的波形图,串行数据RXD经过ATD电路处理,在RXD每一次的0、1变化(上升沿或下降沿)都会产生一个低电平,ATD电路的输出波形见图3中的ATDD信号;在波特率检测电路中,两个采样计数器分别记录下ATDD信号低电平的最小系统时钟周期数min1和高电平的最小系统时钟周期数min2,min1、min2的和就是RXD中一位数据所占用的系统时钟周期数(也就是所谓的最小值),通过不断迭代,最终得到我们需要的最小值。通过公式:波特率=系统时钟频率/最小值,就可以确定串行数据的波特率。

3 UART波特率发生模块的设计

基于“ATD+迭代法”的基本想法,UART波特率发生模块分为三个部分,即ATD电路、波特率检测电路以及波特率产生电路。

3.1 ATD电路

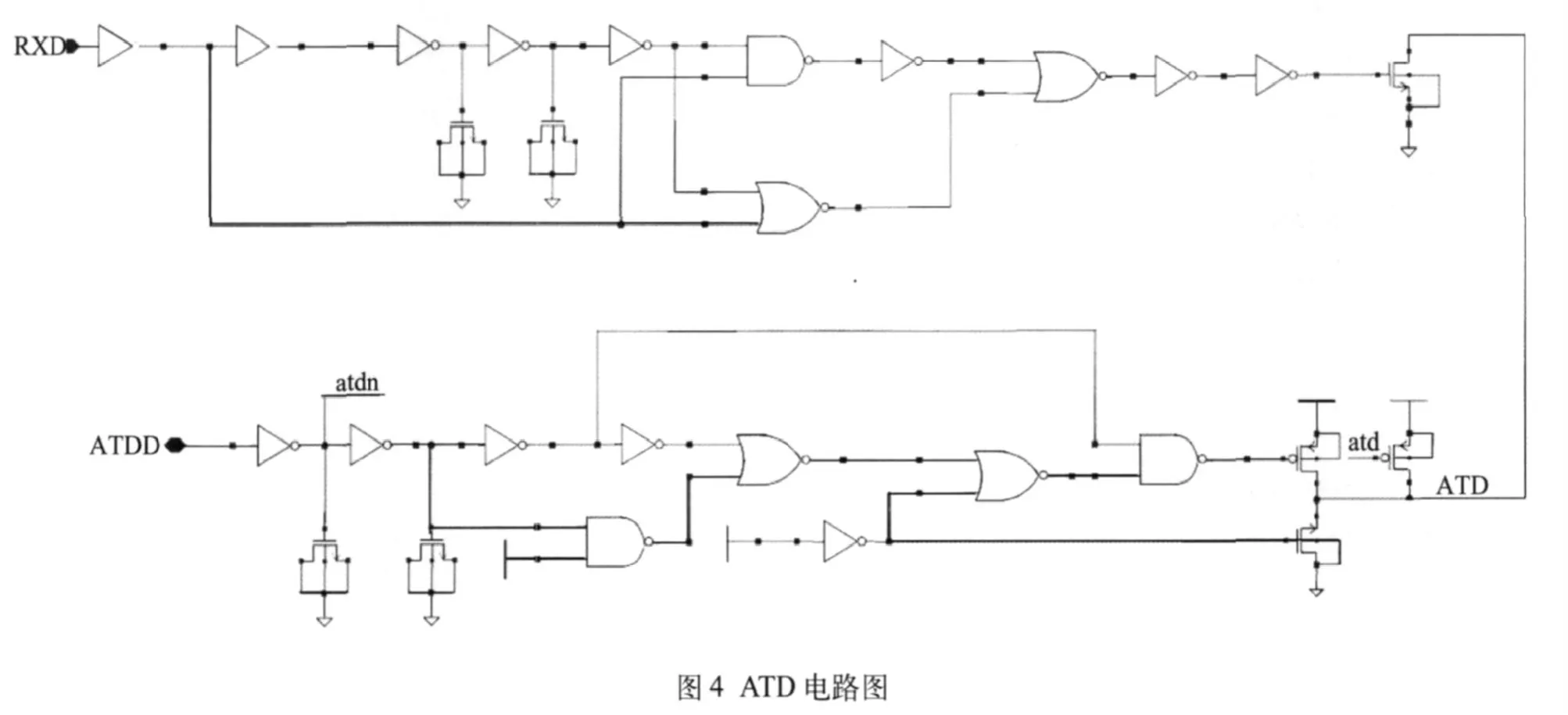

UART波特率发生模块中的ATD电路如图4所示,图中端口RXD为串行数据的输入端口,双向输入输出端口ATDD输出对串行数据的检测信号。使用Hspice软件对ATD电路进行仿真,仿真结果如图5所示。可见,串行数据的每次翻转(0→1或1→0)都会引起ATD电路输出信号下降到低电平并持续一段时间。

3.2 波特率检测电路

UART波特率发生模块中的波特率检测电路的设计采用的HDL(hardware description language)语言为Verilog,根据自顶向下的设计原则进行设计。

波特率检测电路设计流程图如图6所示。迭代的具体过程是:首先给最小值赋初值,高、低电平最小值g_min、l_min都设为40(对应于实际波特率,g_min应为40000000)。ATDD信号传输进来后,每遇到系统时钟的上升沿,采样计数器分别对高、低电平进行计数,计数结果分别与保持寄存器中存放的g_min和l_min进行比较,如果该计数值比g_min或l_min小那么就把计数结果赋值给g_min或l_min,否则,将保持寄存器中存放的g_min或l_min。如此迭代下去,最终得到最小值g_min和l_min,两个数之和就是我们所需的最小值,也就是传输一位数据所占用的系统时钟周期数。把该最小值传输给波特率发生器,就能产生相应的波特率。

波特率检测电路的verilog程序关键代码如下:

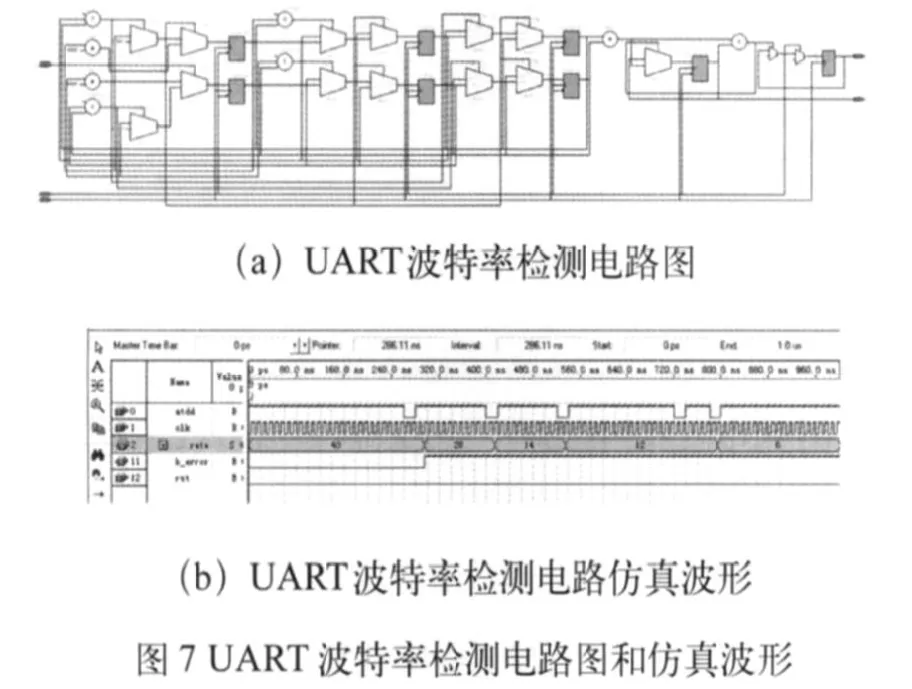

根据上述verilog程序,综合得到UART波特率检测电路的电路图,如图7(a)所示;其仿真波形如图7(b)所示,从图中可以看出,经过一段时间的迭代,最终得到一个最小值,从而准确地探测出RXD信号的波特率。

3.3 波特率发生器模块

波特率发生器实际上就是一个分频器。实现波特率时钟的基本思路就是设计一个计数器,该计数器工作在频率很高的系统时钟下,当计数到波特率检测电路输出的最小值一半时将输出置为高电平,再计数到该数值后将输出置为低电平,如此反复就能得到所需的波特率时钟[2]。

4 结束语

利用Quartus软件完成电路的物理设计、仿真及综合,结果表明采用“ATD+迭代法”设计的UART波特率发生电路能正确地输出串行数据波特率。

[1]周建华,万书芹,薛忠杰. 一种新颖的UART自适应波特率发生器的设计[J] . Semiconductor Technology,2007(12) ∶1052-1055.

[2]李秋菊,杨银堂,高海霞. 基于Verilog HDL的UART IP的设计[J] . Semiconductor Technology,2007 (6) ∶ 520-523.

A Design of Baud-rate Generator for UART

ZHAO Lin-na1, ZHAO Huang1, LI Hong-zheng2

(1.School of IT Engineering,Southern Yangtze University,Wuxi214036,China;2.China Electronic Technology Group Corporation No.58Research Institute,Wuxi214035,China)

In our paper we design a UART baud-rate Generator based on ATD (Address-Translate-Detector)circuit. The ATD circuit is used to monitor the changes of serial data, and experts the low level signals along the rising edges or falling edges of serial data. Two counters are used for counting the numbers of low and high level periods of ATD signal respectively. The value stored in counters has been compared with the minimum value stored in register. If the former is less than the latter, then the minimum value will be replaced by the value stored in counters, otherwise, maintaining the latter. Repeating this process, we get the accurate baud-rate.

UART; baud-rate generator; address-translate-detector (ATD) circuit

TN791

A

1681-1070(2010)09-0019-05

2010-06-13

赵琳娜(1979-),女,天津人,助教,研究方向为CMOS数字集成电路设计。