基于PLL和TA31136的调频接收机设计

2017-10-18吴家烜

吴家烜

(黎明职业大学 信息与电子工程学院,福建 泉州 362000)

基于PLL和TA31136的调频接收机设计

吴家烜

(黎明职业大学 信息与电子工程学院,福建 泉州 362000)

基于PLL锁相环频率合成方法,研究一种采用单片机和 TA31136 实现FM接收机的方法。电路设计采用超外差结构,电路控制采用STC12C5A60S2单片机,可通过按键直接设置接收频率,用LCD1602液晶显示频率,接收频率范围为 70~110 MHz,最终实现基于PLL和TA31136的FM接收机。经测试,两本振信号频率准确,接收效果良好,符合设计要求,具有一定的应用价值。

单片机;PLL;混频;FM接收机

调频接收机广泛应用于FM广播、无线监控、数据传输等民用和工业领域。接收机的主要指标有:噪声系数、灵敏度、互调失真、三阶截点、无杂散范围和内部杂散响应等,比发射机更多,设计要求更高[1]。随着技术的发展和器件的进步,调频接收机的方案从传统的超外差接收机方案发展到直接下变频方案、镜频抑制接收方案、数字零中频方案等。同时,芯片公司也设计了许多功能丰富的单片集成FM芯片,如RDA5807、TEA5990等,只要加上单片机控制和一些简单的外围电路即可实现民用公开频段的FM接收功能。但这种集成FM芯片存在低噪大、灵敏度低、频率范围被限定、电路设计不灵活等诸多问题,应用范围较为局限。而在工业领域应用较多的直接下变频方案、数字零中频方案硬件成本较高,电路复杂,较适合运用于在对电路成本不敏感的电子设备中。超外差接收机方案至今仍然是使用最为广泛和成熟的技术,且具有性价比高、指标好、频率范围大、杂散抑制特性好等特点。因此,本文所讨论的就是一种基于超外差接收机原理和 STC12C5A60S2单片机控制,通过采用PLL和 TA31136来实现 FM接收机的设计。

1 电路原理

典型的超外差调频接收机,将接收到的射频不失真地降低为一个固定的中频(一般为450 kHz或者455 KHz)。但寄生通道干扰,特别是镜像频率干扰,是这种一级混频的结构面临的严重问题。而唯一的解决办法就是提高中频,但仅仅提高中频亦会导致解调困难等问题出现,因此选取折中方案,即改进为超外差式二次混频结构[1-3],如图1所示。

图1 超外差式二次混频结构

这种结构主要是将RF射频信号在解调前利用二级混频和放大电路进行逐级变频和放大,最终达到可处理的低中频解调信号频率[2]。图1中包含两次混频,一次混频通常采用高中频,以提高镜像抗拒比,常见的高中频有10.7、21.4、38.4和45 MHz等[2];二次混频采用低中频,用于提高接收机的选择性,常用的有450、455或者465 kHz等。这种超外差式二次混频结构具有稳定性和灵敏度高等特点,其电路复杂度高、集成度差。

2 调频接收机设计

2.1系统框图

本设计主要是为了实现频率范围为70~110 MHz,步进0.1 MHz的调频接收机,系统带1602液晶显示和4×4键盘控制,频率可预设和步进调节。接收机采用超外差二次混频结构。系统框图如图2所示。

图2 调频接收机系统设计框图

当天线接收到RF射频信号后,经过第一级的低通滤波器和LNA放大弱小信号,再经过一级带通滤波器后进行第一级混频。第一中频为10.7 MHz,则第一级混频本振频率范围为59.3~99.3 MHz,本振信号由PLL频率合成器电路产生。锁相环部分主要由锁相环芯片MC145170和VCO芯片MC1648两个芯片组成的锁相环频率合成电路,而MCU部分由STC12C5A60S2单片机负责送控制命令和实现显示键盘功能。第一级的混频电路选用双栅mos管BF1212WR进行混频。混频输出10.7 MHz的第一中频,经过10.7 MHz的陶瓷带通滤波器和低噪放,抑制杂散信号,然后进入中频解调芯片TA31136进行二次混频。二次混频的本振频率为10.25 MHz,本振信号由无源晶振搭设的皮尔斯振荡器产生。二次混频后输出450 kHz的第二中频。经过中频解调芯片TA31136进行鉴频解调出低频信号,最后由低频功放放大输出。

2.2关键电路设计及实现

2.2.1 59.3~99.3 MHz的PLL频率合成器

在系统中,最重要也是核心部分就是PLL频率合成器,其作用是给系统的第一混频提供高质量的本振。频率合成器框图如图3所示。

图3 59.3~99.3 MHz PLL频率合成器

59.3~99.3 MHz的PLL频率合成器的锁相环的核心部分主要由两个芯片:MC145170锁相环芯片和VCO芯片MC1648组成的,而单片机MCU部分负责控制锁相环芯片MC145170和实现液晶显示键盘等功能。MC145170锁相环芯片是一片可用于最高工作频率185 MHz、可用SPI串行码输入编程的单模CMOS单片锁相环频率合成器芯片,而MC1648是最大输出频率为225 MHz的集成VCO芯片。12 MHz的晶振产生本振信号送到芯片MC145170内部的分频器和鉴相器处理;MC1648芯片负责产生压控振荡,同时送到MC145170芯片内部的分频器和鉴相器进行处理,在芯片MC145170的第13管脚输出一个信号,再经过环路滤波器,得到一个直流分量。该直流分量控制压控振荡器,从而达到锁相目的。

单片机控制芯片采用教学中经常使用的STC12C5A60S2单片机,其中P2为数据线,P1作为4×4的按键使用,而P0口作为LCD1602液晶的显示控制。主程序先对LCD1602进行初始化,再根据送来的数据进行拆分。之后设定一个初始频率值80 MHz,并且判断送来的频率是否在设计范围之内。在范围之内,则显示频率值,否则显示为“out of range..”。其程序流程如图4所示。

图4 主程序流程

为了保证该芯片正确工作,编程前应该对芯片进行复位操作。复位后, 就可以按照C、N、R的顺序进行3个寄存器的操作。这里取R 值等于100 ,选定鉴相器工作频率为晶振频率的1/100 ( 即100 kHz) 。N的值可按所需要的频率编程。由于频率合成器的输出频率范围是59.3~99.3 MHz, 因此,该数值的设定值应在593~993之间。

2.2.2 一次混频电路

混频器的构成一般为本振、非线性器件和滤波器。常用于混频的非线性器件有二极管、三极管和双栅场效应管等分立器件[2]。随着IC电路设计的发展,混频器也往往会集成到芯片中,成为芯片设计中的一部分。双栅场效应管相对于二极管、三极管混频电路,有增益大、噪声小,动态范围大,混频失真小等特点[2]。为了降低成本和便于调试测试,采用基于对讲机电路中常用的双栅极N沟道场效应管BF1212WR作为混频器。混频电路如图5所示。

图5 一次混频电路

在此混频电路中,射频信号(ANT)和59.3~99.3 MHz的本振信号分别输入两个栅极,利用双栅mos管的乘法运算特性进行混频。输出信号经过10.7 MHz的陶瓷滤波器滤除干扰后送到下一级。在上图中,R1~R4为电压偏置电阻,用来导通mos管。

2.2.3 10.25MHz皮尔斯振荡器

二次混频所采用的10.25 MHz本振信号有两种方案:一种是直接用10.25 MHz的有源晶振,另一种是用无源晶振去搭设一个皮尔斯振荡器。相比较而言,有源晶振结构简单,但成本高;皮尔斯振荡器有低功耗、低成本及良好的稳定性等特点,完全可以取代有源晶振。而皮尔斯电路是一种设计接地的并联型晶体振荡电路,如图6所示。

图6 10.25 MHz皮尔斯振荡器

图6中V1是用于振荡晶体管,晶体12.25 MHz位于c极和b极之间,与C1和C2构成并联型振荡电路。晶体管V2用来当做一个输出缓冲器,提高输出带载能力。

2.2.4 基于芯片TA31136的二次混频和鉴频输出

本接收机的关键芯片是中频解调芯片TA21136fn,它的作用是用于第二中频的混频和解调基频信号。一中频IF-IN的10.7 MHz经过放大后送到中频解调芯片TA21136fn,与10.25 MHz皮尔斯振荡器产生的二本振混频LO2混出450 kHz的二中频,经过450 kHz的陶瓷滤波器二次滤波后,再经过中频放大后用CF1陶瓷鉴频器450 kHz进行鉴频解调信号,最后从AF脚输出低频语音信号,经过下一级低频放大器放大后输出。电路如图7所示。

图7 基于芯片TA31136的二次混频和鉴频输出

2.3电路测试

由于使用的都是无源晶振,频率会偏差几kHz,可以通过调整晶振的补偿电容,用频谱仪来标定频率,最终使LO1和LO2的频率准确度达到要求。采用北京RIGOL公司的DSA815频谱分析仪进行测试LO1和LO2的输出特性。单片机设置LO1的中间输出频率为85 MHz,DSA815频谱仪设置中心频率85 MHz,SPAN为100 kHz,RBW为1 kHz,观察并截频,频谱如图8所示。

图8 LO1在输出85MHz时的输出频谱特性

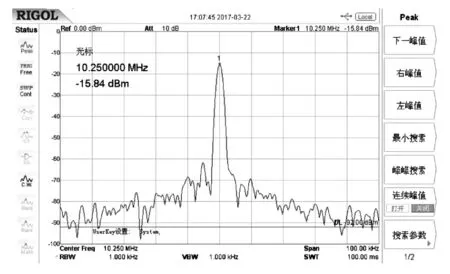

用频谱分析仪直接观察LO2的输出特性,设置中心频率10.25 MHz、SPAN为100 kHz、RBW为1 kHz,观察并截频,如图9所示。

图9 LO2 的输出频谱特性

结果表明:频率与设置值一致,且可在设计范围内更改,符合设计要求。LO2的10.25 MHz频率也符合设计要求。

3 结 论

研究一种采用PLL和 TA31136 实现FM接收机的方法。提出电路设计,采用超外差结构,给出关键电路的设计和测试结果。该电路结构简单,工作可靠高,成本较为低廉,便于调试。测试表明:频率设置范围为70~110 MHz,两本振信号频率准确,接收效果良好,符合设计要求。因此,该设计方法在无线电通信和工业控制领域具有一定的应用价值。

[1] 陈飞.小型化短波接收机低噪声射频前端研究与实现[D].西安电子科技大学, 2014:20.

[2] 耿永端.超短波接收机射频前端电路的研究与设计[D].大连海事大学,2014:14.

[3] 赵秋明.VHF波段频率合成器的设计与实现[J].大众科技,2012(4):26.

Abstract: A circuit realization method of FM receiver by using MCU and TA31136 has been discussed in his paper based on the phase-locked loop frequency synthesis method. Adopting super heterodyne structure as the circuit design, and using STC12C5A60S2 microcontroller as the control circuit, the receiver has been devised and receive frequency, whose range is from 70 MHz to 110 MHz can be set up by keys and displayed on LCD1602. Based on PLL and TA31136, the VHF FM receiver has been realized at length with accurate frequency of the local oscillator 2 signal, good receiving effect, and the receiver meets the requirements of the design with certain application value after testing.

KeyWords: MCU;PLL;mixing; FM receiver

(责任编辑:黄韡 英文审校:杨德权)

DesignofFMReceiverBasedonPLLandTA31136

WU Jiaxuan

(College of Information and Electronic Engineering, Liming Vocational University, Quanzhou 362000, China)

TN 74

A

2017-02-17

吴家烜(1980-),男,讲师,主要从事无线电通信和微波电路研究。

泉州市科技局科技项目(2016G053);黎明职业大学规划项目(LZ2013101)

1008-8075(2017)03-0083-06

10.13446/j.cnki.jlvu.20170048