内存空间在双空间存储器上的推移技术实验

2017-05-24展豪君金翊欧阳山石也强

展豪君,金翊,欧阳山,石也强

(上海大学计算机工程与科学学院,上海 200444)

内存空间在双空间存储器上的推移技术实验

展豪君,金翊,欧阳山,石也强

(上海大学计算机工程与科学学院,上海 200444)

详细介绍双空间存储器理论和其核心技术——内存空间推移技术的仿真实验.证实了用非易失性随机存储器(non-volatile random access memory,NVRAM)构建双空间存储器的可行性,同时通过对8086CPU系统的仿真实验,证实了将内存空间在双空间存储器上推移之技术的正确性.实验设置的目标系统包含一个8086CPU,16 MB的双空间存储器和16个8位的推移锁存器.目标系统中设置了2个不可闭窗和14个可推移的窗框,在不可闭的255号窗壁中设置了8086CPU的首指令和初始化程序,在不可闭的254号窗壁设置了8086CPU的中断向量表和双空间存储器的推移向量表.实验完成了8086CPU的上电过程、自动执行初始化程序、正确执行中断命令、正确执行数据读写命令等操作,并将CPU对其1 MB内存空间的随机读写访问自动落实为对16 MB双空间存储器指定位置的实时随机访问;实验还完成了随时修改推移锁存器的操作,并以此将对应的窗框推移到了双空间存储器的任意位置.实验结果为双空间存储器理论和内存空间推移技术奠定了基础.

双空间存储器;非易失性随机存储器(non-volatile random access memory, NVRAM);内存推移

三值光学计算机[1-3]有众多的数据位,因而适合于处理大批量的数据[4-7].这一特征不仅要求三值光学计算机的存储器具有较大的存储容量,而且能被处理器快速地随机读写大量数据.一方面电子计算机的内存容量受到CPU地址线数目的限制,无法达到三值光学计算机的要求;另一方面,计算机外存上的数据不能直接被处理器随机读写,必须先以顺序方式拷贝进内存才能被处理器随机读写,因此外存也不能满足三值光学计算机的要求.鉴于此,研发大容量、高访问速度、非易失且可以被随机读写的存储器成为三值光学计算机研究者的重要任务之一.

固态盘兼有可随机读写、非易失、体积小、速度快的特点,适用于构造三值光学计算机需要的存储系统,特别是结合闪存与随机存储器特点于一体的非易失随机存储器(non-volatile random access memory,NVRAM),例如相变存储器[8-10]、铁电存储器[11-12]、磁阻式存储器[13-14]等.文献[15-16]提供的数据表明,NVRAM的读写速度和性能已经达到了当前计算机系统中使用的DRAM和SRAM的水平,而AGIGA Tech公司更是制造出了性能达到DDR4[17]标准的非易失随机存储器—–NVDIMM[18],这为实现三值光学计算机的高速度、大容量存储系统奠定了物质基础.由此,本工作提出了同时具有非易失性和随机访问性的双空间存储器概念和理论,并建立了将内存空间分区映射到双空间存储器上的技术——内存推移技术[19].在这项存储器新理论和技术中,双空间存储器的容量取决于推移锁存器的位数,而该锁存器的位数可以随意设置,因此双空间存储器的容量足以达到三值光学计算机的要求;同时,利用双空间存储器的非易失性建立的块空间可以用作外存,利用其可随机访问性建立的字空间可以与内存空间对接(映射),因此块空间(外存)上的所有数据都可以通过字空间(内存映射之后)直接被处理器快速地随机读写.相比于传统的存储体系结构,本工作提出的理论和技术优势如下:消除数据/程序在内存与外存之间的拷贝过程,消除开机和启动程序的等待过程,利用推移锁存器能够将内存空间完整地分时映射到很大的双空间存储器的各个区域,从而使CPU可以自动地随时随机访问双空间存储器的任何单元,且读写速度不会低于当前的内存速度.目前,双空间存储器和内存推移技术的理论推证已得到完善[19],通过实验证实双空间存储器和推移技术的正确性,不仅已成为该研究方向的焦点,也是将这项新理论和技术应用于计算机系统的桥梁.

1 双空间存储器原理及内存推移技术

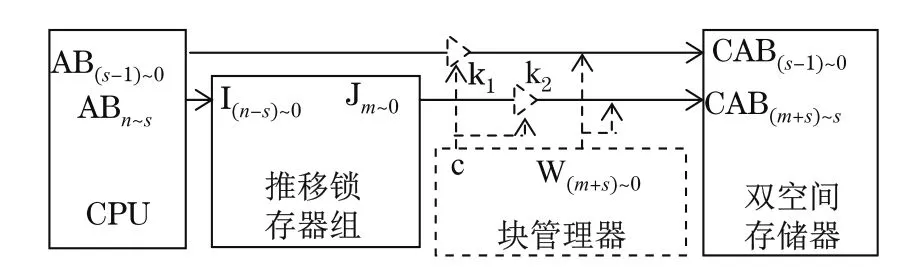

作为双空间存储器和推移技术的硬件基础,双空间存储器的地址总线配置如图1所示.该地址总线共有如下4个特征.

图1 双空间存储器地址总线Fig.1 Address bus of double-space storage

(1)双空间存储器的地址总线CAB(m+s)~0与块管理器的输出线W(m+s)~0直接相连,而系统通过块管理器访问存储系统时,总是以块为单位,块内采用顺序访问.因此,系统访问的是双空间存储器的块空间.显然,此时的双空间存储器是系统的外存.

(2)双空间存储器地址线中的低序号部分CAB(s−1)~0与CPU输出的内存地址总线中的低序号部分AB(s−1)~0直接连接.而CPU通过内存地址总线访问存储器时,总是以字(或字节)为单位随机访问.因此,系统访问的是双空间存储器的字空间.显然,双空间存储器的这部分存储单元是系统当前内存的一部分.称AB(s−1)~0构成的内存空间为映射窗,而称CAB(s−1)~0在双空间存储器中对应的存储区间为窗壁.

(3)双空间存储器地址线的高序号部分CAB(m+s)~s与推移锁存器组的输出线Jm~0相连,而推移锁存器组的输入线I(n−s)~0与CPU输出的内存地址总线中的高序号部分ABn~s直接连接.因此,ABn~s的值(内存地址高位部分)将从推移锁存器组中选择一个推移锁存器,该推移锁存器的输出为双空间存储器的高位地址CAB(m+s)~s.由于此时CAB(m+s)~s的值源于ABn~s,因此CAB(m+s)~s是字空间的高位地址,它给出了映射窗当前所对应的窗壁的起始地址,这个地址值正好可以用作该窗壁的编号.鉴于推移锁存器的输出Jm~0仅确定了字空间地址的高位部分CAB(m+s)~s,而字空间地址的低位部分CAB(s−1)~0仍可取任意值,因此不妨认为Jm~0给出了一个容量为2s个字(或字节)的虚拟随机访问空间,并可认为其地址为J−1~−s,称该虚拟空间为窗框.显然,每一个推移锁存器对应一个窗框,而每一个推移锁存器又对应ABn~s的一个取值,每个ABn~s的取值对应一个窗框,因此这个值可作为窗框的编号.

显然,映射窗、窗框和窗壁的大小相同,但有2(m+1)个窗壁,以CAB(m+s)~s(或Jm~0)的值为编号,所有窗壁组成双空间存储器;有2(n−s+1)个窗框,以ABn~s(或I(n−s)~0)的值为编号,每个推移锁存器对应一个窗框,所有窗框组成当前内存空间;系统中仅有一个映射窗,处理器只能透过映射窗随机访问双空间存储器.给一个推移锁存器赋值后,就将相应的窗框安放在该值指定的窗壁上,称该窗壁的状态为开窗,没有安放窗框的窗壁称为闭窗.窗框不能被移走的窗壁称为不可闭窗,显然不可闭窗的窗框不能被移动,即它所对应的推移锁存器的值不能被修改.由于映射窗只能通过改变ABn~s的值在窗框之间移动,所以映射窗只能位于某个开窗上,不可能位于闭窗上,因此处理器只能透过映射窗随机访问开窗上的存储单元,无法随机访问闭窗上的存储单元.再考虑到任何一个可移动的窗框都能被安置在任一个窗壁上,于是通过在窗壁间推移窗框和在窗框间推移映射窗,处理器就能访问整个双空间存储器.显然,处理器随时可以透过映射窗访问不可闭窗,因此数据和程序位于不可闭窗相当于在当前系统中驻留内存.

(4)双空间存储器的地址总线CAB(m+s)~0与ABn~0的连接受三态门k1和k2的控制,而块管理器的输出端c控制k1和k2状态.当访问外存时,处理器启动块管理器,则c控制k1和k2处于高阻态,从而断开CAB(m+s)~0与ABn~0的连接;当访问内存时,处理器停止块管理器,则c信号失效,k1和k2处于低阻态,则开通CAB(m+s)~0与ABn~0的连接.由于实际系统中处理器不会同时访问内存和外存,c,k1和k2的功能往往由处理器自动完成,实际系统中并不需要构造出来,所以图1中的c,k1和k2只是表明双空间存储器的字空间和块空间不会同时被访问.

2 推移技术实验方案设计

鉴于块空间可以直接用作外存,因此对块空间的实验验证没有重要意义[19],本工作暂不考虑块空间的问题,而将实验研究集中在验证内存空间的推移技术方面.实现推移技术的核心操作在于3点:①通过给推移锁存器赋值使窗框安置在指定的窗壁;②通过内存地址的高位部分将映射窗自动定位在选定的窗框上;③CPU透过映射窗随机访问到双空间存储器的任意单元.如果能够验证这3个核心操作,就可以确定整个推移技术.

为了有效、便捷地完成实验研究任务,选择硬件仿真软件Proteus 8.0进行系统模拟实验. Proteus 8.0有两个性能对本实验起到关键作用:①能够对8086CPU的工作过程进行仿真;②能对目标系统中设定的各种存储芯片的数据进行实时仿真[20].利用前者能够仿真8086CPU对内存空间的访问;利用后者能观察构成双空间存储器的每个芯片的内容,并以此来判断对内存空间的访问是否落实到双空间存储器的指定位置,从而判断推移技术是否正确和可行.

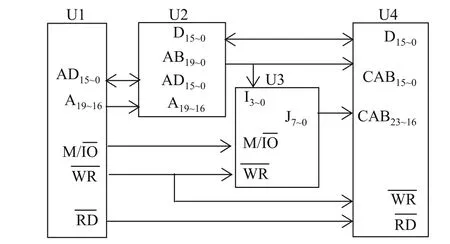

2.1 访问字空间系统的设计

8086 CPU是Intel公司生产的16位微处理器,它有20根内存地址线,故内存空间为220字节,即1 MB[21].结合8086的特点,依据图1所描述的双空间存储器地址线配置原理,本工作设计了如图2所示实验系统.在图2中,U1是8086处理器,U2是8086地址/数据复用引脚要求的外部信号分离器,U3是推移锁存器组,U4是双空间存储器.在这个设计中,8086地址线的高4根(AB19~16)接入推移锁存器组的输入端(I3~0),用于选择推移锁存器,故有16个推移锁存器;采用8位锁存器,故推移锁存器的输出线有8根(J7~0),它们接入双空间存储器的高位地址线(CAB23~16);8086地址线的其余16根(AB15~0)直接接入双空间存储器的低位地址线(CAB15~0),故映射窗为64 kB.所设计的双空间存储器共有24根地址线(CAB23~0),故容量为16 MB.若能按照推移技术的操作过程使8086CPU通过其1 MB内存地址及时访问到16 MB的双空间存储器的任何单元,则推移技术和相关理论的正确性将被验证.

图2 8086CPU的内存推移系统Fig.2 Memory space move unit of 8086CPU

2.2 不可闭窗的设置和应用

任何计算机系统在上电时执行的第一条指令和以这条指令为入口的初始化程序都必须始终处于内存空间中,否则计算机无法在上电后自动开始运行.为此,目前的计算机系统总是把第一条指令和初始程序放置在只读存储器中,并将第一条指令的地址设定为系统初始化后给出的第一个取指令地址.在以双空间存储器为基础的系统中,第一条指令和初始化程序也必须位于CPU可随时访问的随机存储器中,且保证第一条指令位于系统的第一个取指令地址上.由于双空间存储器具有非易失性,因此这种系统中不再需要只读存储器,而是将第一条指令和初始化程序放置在不可闭窗中即可.

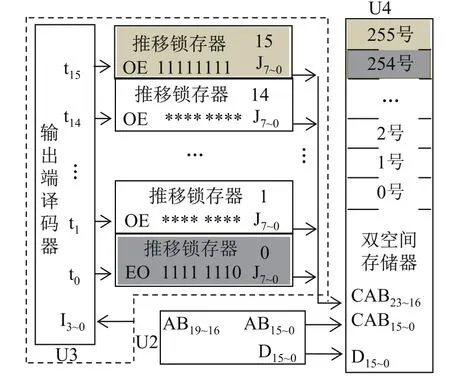

Intel公司设定8086芯片第一条指令的地址为0FFFF0H,即上电后8086CPU送出的第一个取指地址为0FFFF0H,这个地址的高4位为1111,于是AB19~16选中第15号推移锁存器.因此,本工作将第15号推移锁存器设定为不可修改,则15号窗框成为不可推移的.设计255号窗壁为不可闭窗,于是给15号推移锁存器置入固定值0FFH,则15号窗框被设定在255号窗壁上,如图3所示,其中的U2,U3和U4之含义同图2,则255号窗壁上的程序和数据在任意时刻都能被8086CPU随机访问.再考虑到第一条指令地址的低16位为0FFF0H,于是将第一条指令放置在255号窗内偏移量为0FFF0H处,如图4(b)所示.

图3 不可闭窗Fig.3 Unclosed window

图4 不可闭窗应用Fig.4 Application of unclosed window

第一条指令往往是转移到初始化程序的无条件长跳转指令,本实验将系统初始化程序放置在255号窗壁中偏移量为0000H处,于是位于OFFF0H的第一条长跳转指令是一个5字节指令:EA000000F0H,其中第一个字节EAH是长跳转指令的操作码,第二和三字节0000H是执行指令后IP寄存器的值,第四和五字节00F0H是执行指令后CS寄存器的值.当8086CPU启动执行第一条指令后CS为F000H,IP为0000H,即可跳转到设定的初始化程序继续运行.如图4(b)所示.

Intel公司还设定8086CPU的中断矢量表位于内存的00000H~3FFH区段(1 kB).由于中断发生的偶然性,中断矢量表也必须能够随时被CPU随机访问,因此现有的电子计算机系统中往往将中断矢量表驻留在内存中.本工作将中断矢量表安置在不可闭的254号窗壁上.由于8086CPU访问中断矢量表时给出的地址在00000H~003FFH区段,其高4位总是0000,于是AB19~16将选中第0号推移锁存器.鉴于此,本工作给0号推移锁存器也置入固定值0FEH,则0号窗框被固定在254号窗壁,如图3所示.考虑到中断矢量表的低16位为0000H~03FFH,本工作将中断矢量表安置在254号窗壁的开始位置,如图4(a)所示.

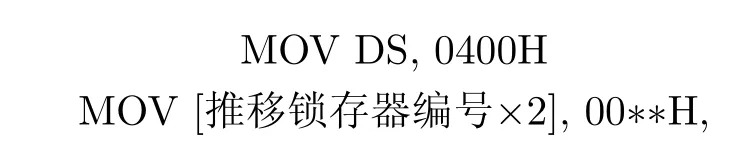

2.3 推移命令设计

图4(a)中,在254号窗壁的400H~4FFH地址范围内留了256个地址的推移向量表区域,该区域内的每一个地址都可以设置为一个推移锁存器的写入端口,称为推移锁存器写入端地址.给一个推移锁存器写入一个值,就将对应的窗框推移到新指定的窗壁上.因此,写推移锁存器的命令就是推移命令.

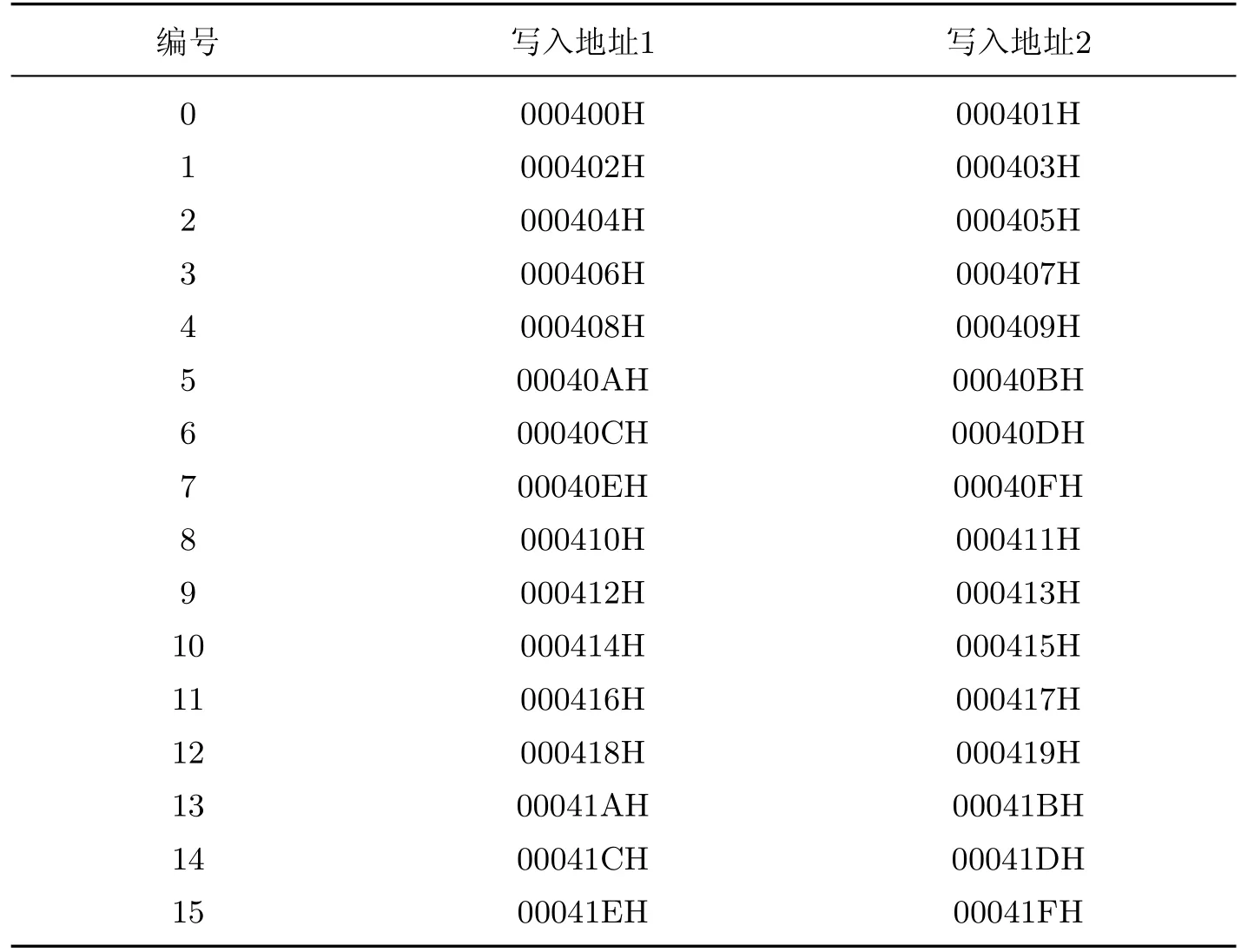

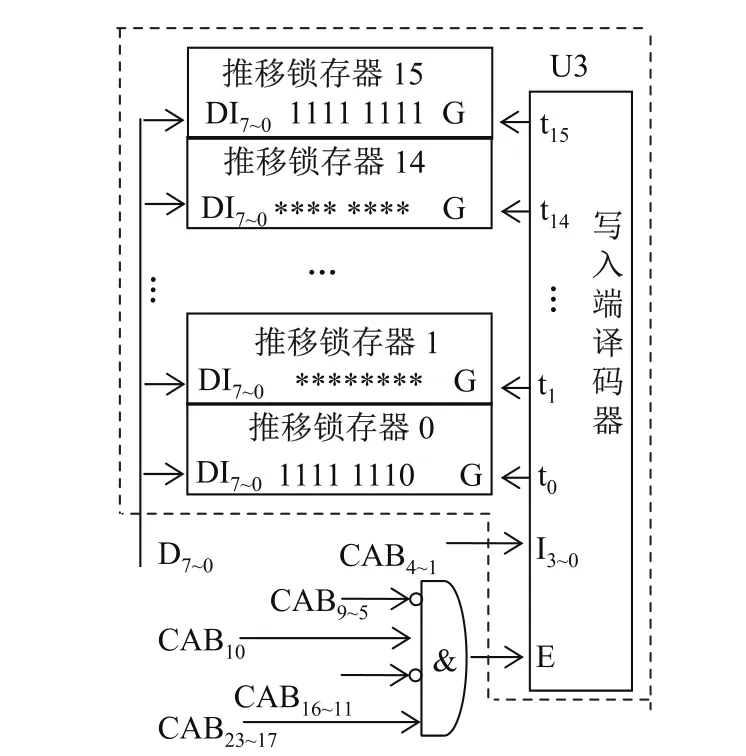

本实验系统仅设计了16个推移锁存器,因此只需要占用图4(a)中推移向量表区域的16个地址,具体占用的地址由推移锁存器写入端地址的布线决定.推移锁存器写入端地址的布线如图5所示,它决定了本实验系统的推移锁存器写入地址(见表1).由于图4中没有CAB0线,因此每个偶数地址和大于1的奇数地址访问同一个推移锁存器写入端.又由于各推移锁存器的写入数据线DI7~0连接系统数据线的D7~0,必须用字命令来写推移命令,且将推移锁存器的修改值放在低8位上,数据的高8位没有意义.由此可知,一个系统的推移命令可以有多种形式.本实验只采用如下形式:

其中∗为十六进制数.图5所示推移锁存写入端地址中的U3之含义同图2.

表1 推移锁存器写入端地址Table 1 Address of write in ports of the move latches

显然,主板制造商可以使各个主板产品具有不同的推移锁存器写入端地址,并使各个主板的初始化程序中包含相应的推移命令,而所有的推移操作必须调用这组推移命令,从而提高了主板的安全性.

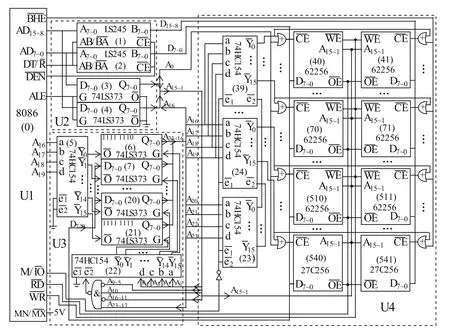

2.4 系统的线路连接结构

结合图2,3和5,并选择74LS373芯片用作各类锁存器,74LS245芯片为数据传输方向控制器,74HC154芯片为4-16译码器,27C256,62256芯片构成双空间存储器芯片,则形成本工作的线路连接原理图,如图6所示.图6中U1,U2,U3和U4之含义同图2.

图5 推移锁存器写入端地址总线Fig.5 Address bus of write in ports of the move latches

图6 实验系统电路原理图Fig.6 Electric schematic diagram of experiment system

需要说明的是,本工作没有使用NVRAM型存储芯片来构造双空间存储器,原因有二:一是Proteus软件中没有NVRAM芯片的模拟器;二是本实验的核心目标是验证内存空间在双空间存储器上进行推移的机制和技术,着重点并不在于双空间存储器的非易失性,因此用普通的随机存储芯片构造一个大于内存空间的可随机访问存储器就足以达到实验目标.对于系统中依靠双空间存储器的非易失性工作的部分,则用在目标系统启动前给相应窗壁先赋指定值的方法来模拟,如对不可闭窗255号窗壁中的8086CPU的初始化程序和首指令就采用这种模拟方式.因此,双空间存储器255窗壁用两片27C256(32 k×8 bit)ROM芯片实现,以便在系统启动之前就可以将初始化程序和首指令烧写到ROM中运行,其他窗壁用62256(32 k×8 bit)SRAM实现.

2.5 实验内容和实验过程设计

内存推移理论的核心技术有如下5个方面:①用非易失性随机存储器构造大容量的双空间存储器;②构造推移锁存器;③用推移命令在双空间存储器上移动窗框;④CPU透过映射窗随机访问窗壁的字单元;⑤不可闭窗的设置和应用.①和②两项技术是系统构造,它们的正确性体现在图5中,如果按图5构建的系统能够正常运行并可实现其余3项技术,则这两项技术的正确性被证实.③,④和⑤三项技术是操作,必须通过实施特定的操作才能证明其正确性和有效性,为此设计如下实验操作方案.

(1)绘制目标系统电路.启动Proteus 8.0,新建工程,根据图6编辑完成实验目标系统的电路并保存工程名为BispaceSimulation.DSN,该电路所需要的元件和图6一致.按图6构造实验目标系统.鉴于相应的工程图太大,此处省略.

(2)设置目标系统的初始化程序和首指令.将255号窗壁中的内容按图4(b)的要求设置.本过程将完成系统启动跳转首指令、初始化程序指令烧写到255窗壁的27C256 ROM芯片中.首先编写完成上述功能的汇编程序;然后将汇编程序编译成bin文件,之后将bin文件转换成能烧写到27C256芯片中的hex文件[22],命名为jvi.hex;最后在Proteus中分别双击255窗壁的两片27C256芯片配置其镜像文件(image file)为jvi.hex,注意偶(奇)体27C256即接低(高)8位数据线D7~0(D15~8)的芯片将其镜像文件基地址设成0(1),文件地址偏移都设成1.这样在本仿真系统启动时,255号窗壁中ROM芯片就保存如图4(b)所要求的程序.判定:若系统启动时,255号窗壁中ROM芯片保存了所要求的程序,则证明系统的初始化程序和首指令设置成功.

(3)模拟8086CPU启动过程.目的:检验目标系统启动后是否正确地执行第一条指令.操作设计:将第一条指令设计为跳转到初始化模拟程序设定的入口地址0FF 0000H.判定:若系统启动后跳转到初始化程序处执行,则证明第一条指令被正确执行并完成跳转.

(4)执行目标系统初始化推移矢量表模拟实验.目的:检验初始化推移矢量表是否被自动执行.操作设计:将8086CPU的初始化程序开始一段设计为给1~14号推移锁存器分别赋值01H~0EH的指令,通过考察254号窗壁推移向量表中相应单元值的变化来判断该初始化程序被执行的情况.判定:若各个推移锁存器具有了预设的值,证明初始化程序运行成功.

(5)透过映射窗访问双空间存储器字空间实验.目标:验证CPU对内存的访问被推移系统透过映射窗落实为对字空间的访问.操作设计:先将1号、2号推移锁存器的值设为01H和02H,即分别指定1号和2号窗壁;然后将数值45H写入0100FFH地址、将数值67H写入0200AAH地址;再执行读出0100FFH地址的内容,并将读出值送入0200ABH地址.判定:若1号推移锁存器所指向窗壁中,偏移地址为00FFH的存储单元中有值45H,在2号推移锁存器所指向的窗壁中,偏移地址为00AAH的存储单元中有值67H,偏移地址为00ABH的存储单元中有值45H,则证明达到实验目标.

(6)修改推移锁存器实验.目的:验证推移指令的正确性.操作设计:执行2.3节给出的推移命令,实现给指定的推移锁存器赋值.考虑到本实验设计的8086初始化程序是由给1~15号推移锁存器分别赋值的指令组成,因此如果方案(4)和(5)的实验成功,则本方案的实验就同时成功.但为了更好地验证推移操作,实验中执行烧写在ROM中的初始化程序的推移指令代码部分,给3号推移锁存器赋值2AH,给5号推移锁存器赋值55H,给14号推移锁存器赋值F3H.判定:若初始化程序执行完推移指令代码部分后各推移锁存器的值均正确,证明推移命令正确,即3,5和14号推移锁存器的值分别为2AH,55H和F3H,则修改推移锁存器成功.

(7)移动映射窗实验.目标:证明若改变一个推移锁存器的值,则对同一个内存地址的访问会落实到不同的窗壁上.设计:用方案(6)证实的技术修改1号和2号推移锁存器,然后再次执行方案(5).判定:若在1号和2号推移锁存器指向的新窗壁上方案(5)成功,则达到实验目标.

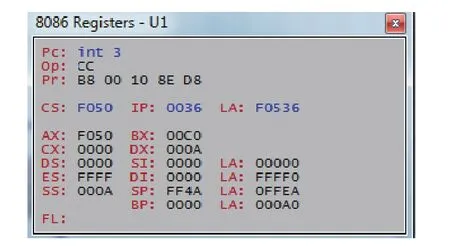

(8)中断系统实验.目标:验证CPU响应中断时能够从中断矢量号找到保存254号不可闭窗的中断矢量,并将中断矢量值正确地送入CS和IP寄存器.操作设计:给254号窗壁中30H号中断矢量的位置赋任意值,本工作中赋值为360050F0H,然后在IP为任意地址时执行中断指令INT 30H.判定:若执行INT 30 H指令后,CS为F050H,IP为0036H,则达到实验目的.本工作还同时验证了CPU可随时访问不可闭窗中的单元.

3 实验操作及结果分析

根据第2节的实验设计,实验操作可分为对硬件模拟软件的操作和对推移技术的验证操作两部分:前一部分是启动Proteus 8.0硬件仿真系统,并在仿真环境中建立目标系统,这部分的实验目的和操作设计见2.5节的方案(1)和(2);后一部分是在目标系统的仿真系统中验证双空间存储器理论的核心技术,其实验目的和操作设计见2.5节的方案(3)~(8).

3.1 建立目标系统仿真环境

仿真环境如下:CPU为Intel奔腾双核T3200,操作系统为Windows 7,仿真软件为Proteus 8.0.

操作一绘制目标仿真系统电路.

步骤(一)启动Proteus 8.0软件,进入建立工程界面.

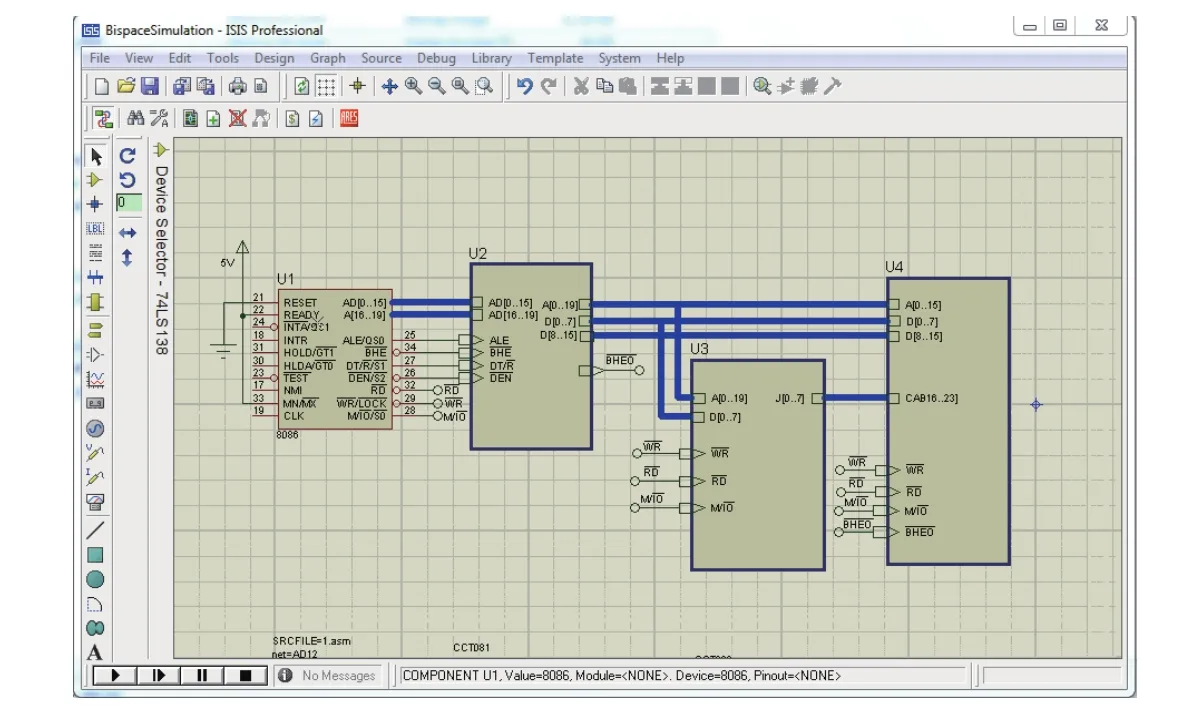

步骤(二)按2.4节的设计,选择目标系统的各种芯片,并连线绘制成目标系统,如图7所示.

图7 仿真系统线路图Fig.7 Circuit diagram of the simulation system

步骤(三)将绘制完成的目标系统存盘,文件名为BispaceSimulation.DSN.

说明:如果将仿真系统在Proteus一张图纸上完成,绘制的图会非常大.因为Proteus支持模块化、多层次、多图纸的设计,所以图7所示的BispaceSimulation.DSN工程是将仿真系统按图2分成的4个模块U1~U4分别绘制然后再组合而成.U1是8086CPU,U2~U4模块的内部细节可参见图6.将U4中双空间存储器每个窗壁中的偶、奇存储体分别命名为M∗.M0和M∗.M1,其中∗代表窗壁号.系统运行时如果想查看某一个窗壁存储器的内容,只需要选择“Debug”菜单下“Memory Contents-M∗.M∗”即可(见图8).另外,从图8中可以看出,在Proteus对目标系统模拟时,可以通过“Debug”对程序调试进行控制,并且可查看目标系统中8086CPU各寄存器状态和当前执行指令等操作.

图8 “Debug”菜单项Fig.8 Menu bar of“Debug”

操作二烧写目标仿真系统的实验程序.

步骤(一)编写系统首指令、初始化程序和30H中断服务子程序的汇编程序.

步骤(二)将汇编程序编译成可执行bin文件,然后利用bin2hex工具转换成能够烧写到ROM芯片的hex文件jvi.hex.

步骤(三)建立只读目标系统初始化程序和首指令的hex文件jvi.hex,将jvi.hex文件烧写到255号窗壁中.

实验结果:单击Proteus中“Debug”菜单下的“Start/Restart Debugging”选项启动仿真系统(见图8),这时再依次选择“Debug”菜单下的“Memory Contents M255-M0”和“MemoryContents M255-M1”查看芯片内容.这两个存储芯片在双空间存储器中的地址为00FF 0000~00FF FFFF(255号窗壁),M25-5M0为偶存储体,M25-5M1为奇存储体,该窗壁的0000位置开始为8086CPU初始化程序的机器指令代码,FFF0H位置为跳转指令EA000000F0H代码, 0536H位置为30H中断服务子程序的指令代码.因为这3个程序的偏移位置间隔太大,所以此处不再给出255窗壁的内容截图,但通过下节操作三到操作八的正确性可判断本操作二成功与否.

3.2 验证双空间存储器理论的核心技术

操作三模拟8086CPU启动过程.

步骤(一)在图8所示界面上点击“Start/Restart Debugging”复位启动系统,使系统恢复到上电状态.

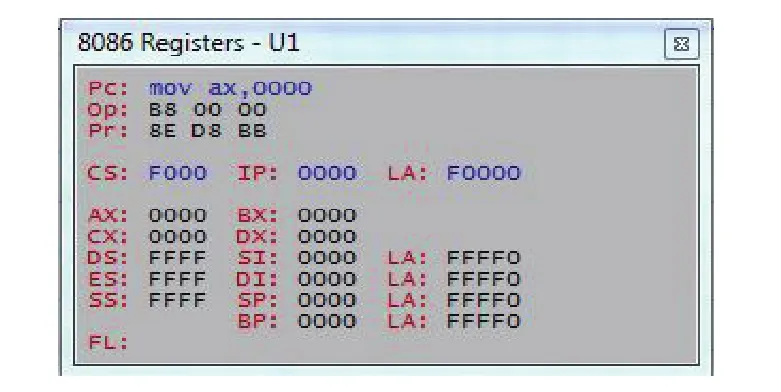

可观察到各寄存器的内容(见图9)如下:AX=0000H,BX=0000H,CX=0000H,DX=0000H, SI=0000H,DI=0000H,SP=0000H,BP=0000H,CS=FFFFH,DS=FFFFH,ES=FFFFH,SS= FFFFH,IP=0000H.

图9 系统复位后8086CPU状态Fig.9 Original state of 8086CPU after reseting system

图9中Op:EA000000F0H和Pc:jmp F000:0000表明了系统复位后要在0FFFF0H执行的第一条长跳转指令.

内存区域:0~254号窗壁(00 0000H~FF 0000H)上的存储单元的值均为00H;255号窗壁的ROM芯片除烧写的跳转指令、初始化程序和中断服务子程序外,其他存储单元的值均为FFH.通过图8所示界面上的“Debug”菜单,从下拉菜单中选择任意窗壁上的“Memory Contents M∗.M∗”芯片可以查看其内容.

步骤(二)基于步骤(一),在“Debug”菜单下选“Step Over”或按“F10”快捷键使处理器单步执行第一条指令.

可观察到各寄存器的内容(见图10)如下:AX=0000H,BX=0000H,CX=0000H,DX= 0000H,SI=0000H,DI=0000H,SP=0000H,BP=0000H,CS=F000H,DS=FFFFH,ES= FFFFH,SS=FFFFH,IP=0000H.

图10中Op:B80000H和Pc:mov ax,0000表明了系统复位后成功跳转到FF0000H处要执行的初始化程序的第一条指令.

实验结论:目标系统复位成功;目标系统利用15号推移矢量成功跳转到初始化程序位置上执行.

操作四执行目标系统初始化推移矢量表实验.

按“F10”键使处理器单步执行2.5节方案(4),该操作指令已经被烧写到ROM中.

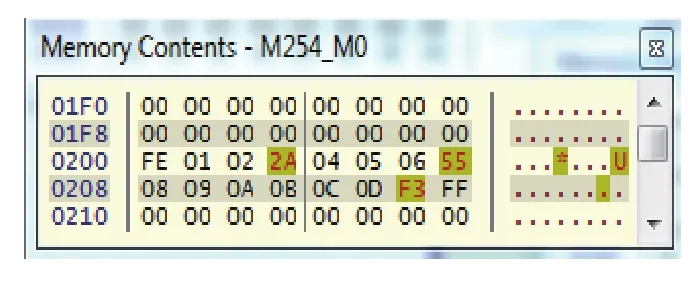

执行结果:双空间存储器区域FE0400H~FE04FFH的值为设定的窗壁地址,其余地址的存储单元值均为00H.通过“Debug”菜单查看254不可闭窗壁上0400H~041EH推移矢量表的内容(见图11),仅看偶存储体“Memory Contents-M254-M0”,因为所设计的电路图可以保证推移锁存器与推移矢量表内容同步,所以0~15推移锁存器的值依次初始化为FEH, 01H~0EH和FFH.需要说明的是,因为254号窗壁是由双8位存储体组成,所以图11中红色框的偏移地址0200H都需要乘以2.例如,图11左边0200H位置其实对应的254号窗壁的偏移地址中的0400H(低8位),右边0200H对应254号窗壁的偏移地址中的0401H(高8位).下面所述存储器的读法与此相同.

图10 系统正确启动状态Fig.10 Normal state after starting system

图11 推移锁存器初始化矢量Fig.11 Initial values of the move latches

实验结论:初始化程序执行后双空间存储器的FE0400~FE04FF的值与设定值相同.初始化程序正常执行,且推移矢量表初始化设置完成.

操作五透过映射窗访问双空间存储器字空间实验.

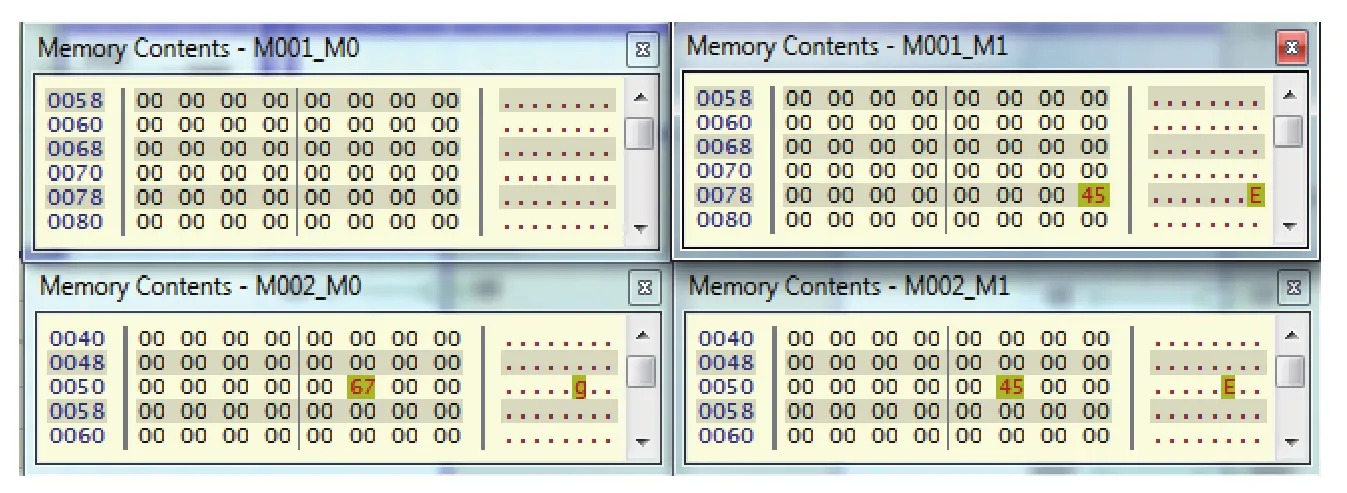

按“F10”键使处理器依次单步执行2.5节方案(5),执行结果如图12所示.图13是操作过程中将0100FFH地址的内容读取到AL中的处理器时各寄存器的状态.

图12 操作五后对应映射窗内容Fig.12 Digits in map window after operating by No.5

实验结论:图13是在DS=1000H,BX=00FFH时执行MOV AL,[BX]指令后的状态.可以看出,通过寄存器间接寻址,可成功读出1号窗壁的FFH位置的45H值到AL寄存器中.图12证明了整个操作过程的成功,即8086CPU成功访问到双空间存储器指定地址.

图13 读取0100FFH地址Fig.13 Reading out digit from 0100FFH address

操作六修改推移锁存器实验.

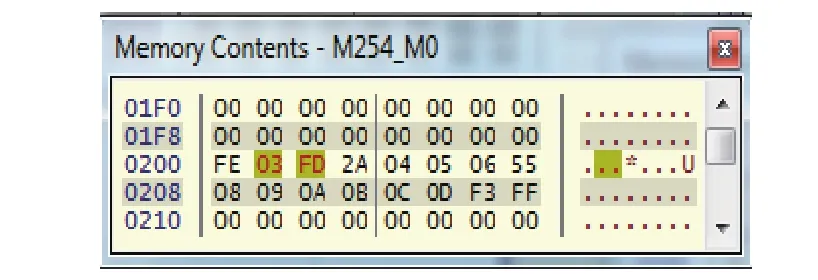

按“F10”键使处理器依次单步执行2.5节方案(6),执行结果如图14所示(仅给出有意义的低8位).执行后推移锁存器后3,5和14号推移锁存器的值分别更新为2AH,55HV和F3H.

图14 操作六结果Fig.14 Results after operating by No.6

实验结论:成功修改推移锁存器.

操作七修改推移锁存器及移动映射窗实验.

首先按2.5节方案(6)将V1,2V号推移矢量分别指向3号和253号窗壁,即推移锁存器分别更新为03H和FDH,然后执行与方案(5)相同偏移地址上的操作.

执行结果:修改推移锁存器结果如图15所示,移动映射窗如图16所示.

图15 修改推移锁存器Fig.15 Rewriting the move latches

图16 操作七后对应映射窗内容Fig.16 Digits in map window after operating by No.7

实验结论:图15说明成功修改推移锁存器,图12与16的对比说明已正确移动映射窗.另外,虽然Proteus 8.0没有提供直接查看锁存器当前锁存值的功能,通过操作六和七可以证明执行推移指令时会将推移锁存器和254号窗壁中推移矢量表中的值保持同步.

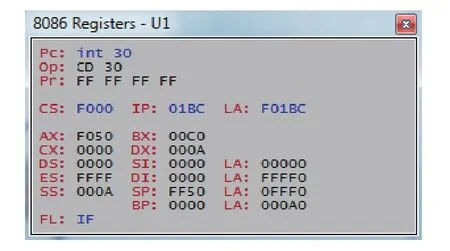

操作八中断系统实验.

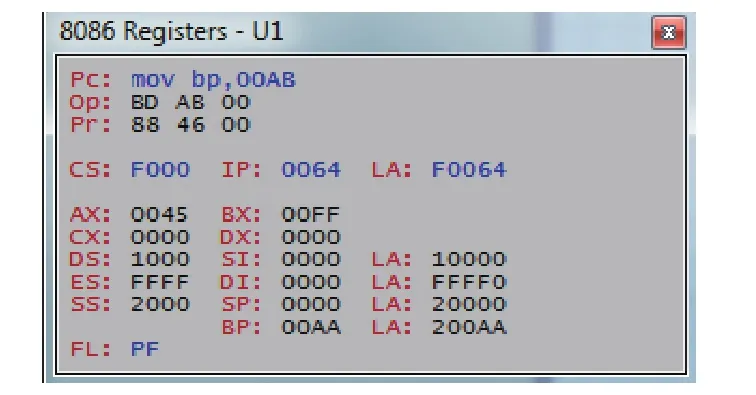

按“F10”键执行2.5节方案(8),即“INT 30H”指令(见图17),执行结果如图18所示.

图17 即将执行INT 30H前8086CPU状态Fig.17 8086CPU statebeforeexecutingin struct INT 30H

图18 执行中断服务程序Fig.18 Running interrupt service routine

实验结论:此时CS:F050H,IP:0036H可以验证处理器正确响应设置在254号不可闭窗的30H中断服务子程序的地址并执行该子程序.

对上述实验重复多次,每次给出不同的参数,均达到实验目的.实验结果证明内存空间推移理论和技术的核心内容的正确性.

4 结束语

基于Proteus 8.0硬件仿真系统完成的实验证实了内存空间在双空间存储器上推移的理论和核心技术.实验中8086CPU的1 MB内存空间依靠16个推移锁存器被分时映射到16 MB的双空间存储器的任意位置,从而使8086CPU对其1 MB内存空间的随机访问自动落实为对16 MB双空间存储器指定位置的随机实时访问.本工作通过设置不可闭窗,保证了CPU的正确启动过程、执行初始化程序和执行中断命令.本工作对推移锁存器进行了方便灵活的改写,并以此实现了内存空间在双空间存储器上的推移操作.

本工作的成功为双空间存储器理论和内存空间推移技术奠定了可靠基础,为研制基于双空间存储器的新型计算机系统勾勒出了设计思想.并可从实验结果推测出,未来的计算机系统中可以用一个大容量的双空间存储器来取代其内存储器和外存存储器,使CPU能实时随机访问的存储器范围达到双空间存储器的整个空间,不再存在内存和外存间的数据拷贝问题.

[1]JIN Y,HE H C,L¨U Y T.Ternary optical computer architecture[J].Physica Scripta,2005, T118:98-101.

[2]金翊.走近光学计算机[J].上海大学学报(自然科学版),2011,17(4):401-411.

[3]金翊,王宏健,欧阳山,等.可重构三值光学处理器的原理、基本结构和实现[J].中国科学:信息科学,2012,42(6):778-788.

[4]谌章义.千位三值光学处理器理论、结构和实现[D].上海:上海大学,2010.

[5]金翊.三值光计算机高数据宽度的管理策略[J].上海大学学报(自然科学版),2007,13(5):519-523.

[6]李梅,金翊,何华灿,等.基于三值逻辑光学处理器实现向量矩阵乘法[J].计算机应用研究,2009, 26(8):2839-2841.

[7]WANG,X C,PENG J J,JIN Y,et al.Vector-matrix multiplication based on a ternary optical computer[M]//High performance computing and applications.Berlin:Springer-Verlag,2009: 426-432.

[8]SIMPSON R E,FONS P,KOLOBOV A V,et al.Interfacial phase-change memory[J].Nature Nanotechnology,2011,6(8):501-505.

[9]WONG H S P,RAOUx S,KIM S B,et al.Phase change memory[J].Proceedings of the IEEE, 2010,98(12):2201-2227.

[10]LAI S.Current status of the phase change memory and its future[C]//Electron Devices Meeting. 2003,DOI:10.1109/IEDM.2003.1269271.

[11]TAKASHIMAD,KUNISHIMAI.High-density chain ferroelectric random access memory (CFRAM)[J].IEEE Journal of Solid-State Circuits,1998,33(5):787-792.

[12]EVANS J,MONTROSS N,SALAZAR G,et al.A discrete ferroelectric memory[C]//Non-Volatile Memory Technology Symposium.2012,DOI:10.1109/NVMTS.2013.6632857.

[13]TEHRANI S,SLAUGHTER J M,CHEN E,et al.Progress and outlook for MRAM technology[J]. IEEE Transactions on Magnetics,1999,35(5):2814-2819.

[14]YODA H,FUjITA S,SHIMOMURA N,et al.Progress of STT-MRAM technology and the effect on normally-off computing systems[C]//Electron Devices Meeting.2012,DOI: 10.1109/IEDM.2012.6479023.

[15]ZHUANG W W,PAN W,ULRICH B D,et al.Novel colossal magnetoresistive thin film nonvolatile resistance random access memory(RRAM)[C]//International Electron Devices Meeting.2002, DOI:10.1109/IEDM.2002.1175811.

[16]CHENY C,CHENC F,CHENC T,et al.An access-transistor-free(0T/1R)nonvolatile resistance random access memory(RRAM)using a novel threshold switching,selfrectifying chalcogenide device[C]//IEEE International Electron Devices Meeting.2004,DOI: 10.1109/IEDM.2003.1269425.

[17]Jedec.DDR4 SDRAM standard[EB/OL].(2015-03-20)[2017-01-15].http://www.jedec. org/standards-documents/docs/jesd79-4a.

[18]Agiga.AGIGARAM®DDR4 NVDIMM[EB/OL].(2015-05-20)[2017-01-15].http://www. agigatech.com/ddr4.php.

[19]金翊,欧阳山,沈云付,等.一种计算机系统和数据读写方法:201410199434.9[P].2012-04-05.

[20]顾晖,梁惺彦.微机原理与接口技术——基于8086和Proteus仿真[M].北京:电子工业出版社, 2011:177-288.

[21]BREY B B.Intel微处理器[M].金惠华,艾明晶,尚利宏,等译.北京:机械工业出版社,2010: 287-309.

[22]Intel.Hexadecimal object file format specification[EB/OL].(2015-01-18)[2017-01-15].http:// microsym.com/editor/assets/intelhex.pdf.

本文彩色版可登陆本刊网站查询:http://www.journal.shu.edu.cn

Experiment of memory space move technique for double-space storage

ZHAN Haojun,JIN Yi,OUYANG Shan,SHI Yeqiang

(School of Computer Engineering and Science,Shanghai University,Shanghai 200444,China)

This work presents an emulation experiment for double-space storage principle and the memory space move technique.The experiment validate feasibility of using nonvolatile random access memory(NVRAM)to build a double-space storage and correctness of the memory space movement technique.The experiment system consists of an 8086CPU, 16 MB double-space storage,and sixteen 8-bit move latches.Two unmovable and fourteen movable window frames are set up.The first instruction and initial program are set in the 255th window that cannot be closed.An interrupt vector table and a move vector table are set in the 254th unclosed window.It has been make sure that the 8086CPU is booted properly,and the initial program,interrupt service routine,read and write memory instruction are executed correctly.Further,access to the 8086CPU’s 1 MB memory can be automatically transformed to the 16 MB double-space memory unit,and the move latches can be modified to map the window frame into a new window wall of the double-spacestorage.The experimental results lay a foundation for the double-space memory principle and its memory space move technique.

double-space storage;non-volatile random access memory(NVRAM);memory space move

TP 333

A

1007-2861(2017)02-0201-15

10.3969/j.issn.1007-2861.2015.01.017

2015-04-18

国家自然科学基金青年科学基金资助项目(61103054);上海市自然科学基金资助项目(15ZR1415400, 13ZR1416000);上海市教委科研创新资助项目(13ZZ074,13YZ005)

金翊(1957—),男,教授,博士生导师,博士,研究方向为三值光学计算机.E-mail:yijin@shu.edu.cn