45 nmCMOS工艺三模冗余加固锁存器的性能评估

2020-04-08黄正峰李雪筠鲁迎春倪天明

黄正峰, 王 敏, 李雪筠, 鲁迎春, 倪天明

(1.合肥工业大学 电子科学与应用物理学院,安徽 合肥 230601; 2.安徽工程大学 电气工程学院,安徽 芜湖 241000)

0 引 言

随着空间技术和集成电路的高速发展,微处理器已广泛应用于航空航天领域,在太空辐射环境中,存在着大量的中子、α粒子等高能粒子[1-2]。当集成电路遭到高能粒子轰击时很容易发生单粒子翻转 (single event upset,SEU)和单粒子瞬态 (single event transient,SET)[3],导致芯片功能发生错误[4],从而造成严重的后果。

三模冗余(triple modular redundancy,TMR)系统是最简单有效的抗单粒子容错技术。3个模块同时执行相同的操作,以多数相同的输出作为表决系统的正确输出,通常称为“三中取二”。3个模块中只要不同时发生错误,就能掩蔽掉故障模块的错误,保证系统正确的输出。因为3个模块是互相独立的,2个模块同时出现错误是极小概率事件,所以可以大大提高系统的可靠性。但随着互补金属氧化物半导体(complementary metal oxide semiconductor,CMOS)工艺尺寸的日益减小,芯片中的延迟功耗对集成电路的影响日益突出。因此需要对传统的三模冗余结构进行简化,既要保证其抗单粒子翻转的能力,又能降低延迟、功耗和面积开销。三模冗余结构分为主、从两级,主级是3个同构的D锁存器,从级是多数表决器(Voter)。本文中所有TMR锁存器主级结构相同,从级表决器的结构有差异。利用Hspice仿真工具对相关TMR锁存器的延迟、功耗和面积开销进行测量,并且进行对比分析,综合评估性能。

1 三模冗余锁存器容错技术

1.1 三模冗余锁存器结构

TMR容错技术基于多数表决思想,即认为“多数者的意见是正确的”,具体的结构如图1所示。

图1 基本三模冗余锁存器

图1中,M1、M2、M3是3个相同的模块,同时执行相同的操作,以多数相同的输出作为表决系统的正确输出,通常称为“三中取二”,则只要三模冗余主级3个模块中不同时发生错误,就能掩蔽掉故障模块的错误,保证系统正确的输出。

本文将三模冗余锁存器分为主、从两级,在图1中,M1、M2、M3表示三模冗余锁存器的主级;表决器表示三模冗余锁存器的从级。本文分别对三模冗余锁存器的主从两级进行结构分析。

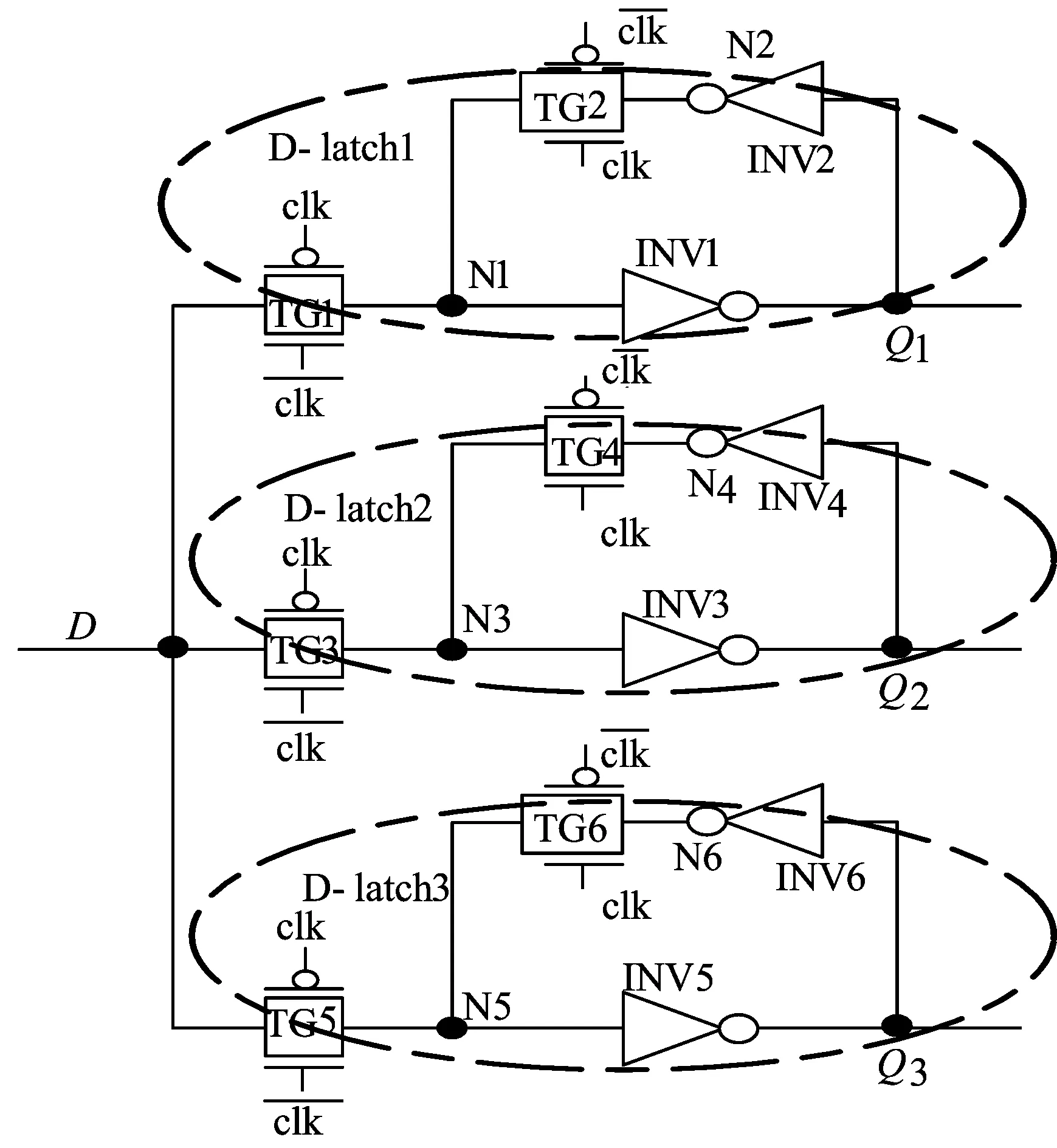

1.1.1 三模冗余锁存器主级

三模冗余锁存器主级如图2所示,由图2可知,本文中三模冗余主级是3个同构的D锁存器,输入信号同时经过锁存器主级产生3个反向信号,再同时进入多数表决器。

图2 三模冗余锁存器主级

1.1.2 三模冗余锁存器从级

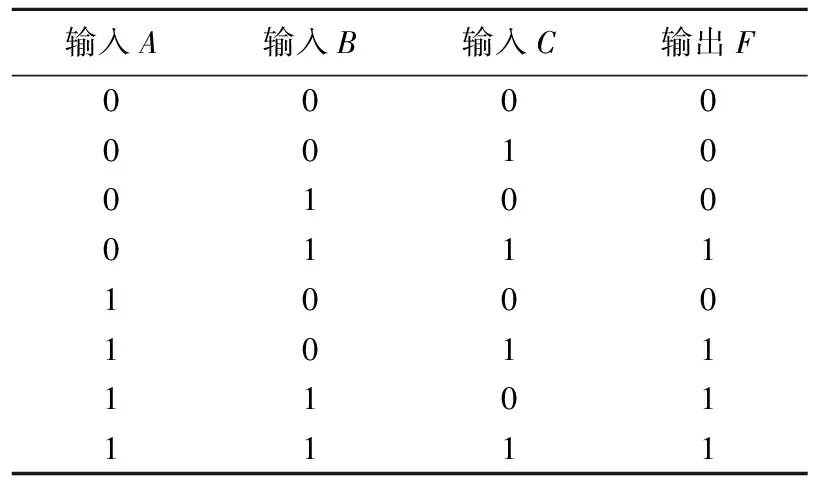

三模冗余锁存器主级有3个输出,对应的表决器有3个输入,假设3个输入分别为A、B、C,输出为F,则根据表决器的“三中取二”原理,其真值见表1所列。

表1 表决器的真值

由表1可以推出此表决器输出公式为:

F=AB+BC+AC

(1)

1.2 三模冗余系统的可靠性

三模冗余系统可以正常工作的条件是:三模都正常,或三模中有任意两模正常,因此三模冗余系统的可靠度RT为[5]:

(2)

其中,Rv、Rm分别表示表决器和模块的可靠度(假设表决器的可靠度为1,且各模块可靠度相同),已经证明,各功能模块有相同的可靠度时整个系统的可靠性最大[6]。

此时三模冗余的可靠度RT为:

(3)

2 三模冗余锁存器工作原理

三模冗余系统结构如图3所示。其工作原理是3个模块同时对输入信号进行运算处理,并将运算结果送往多数表决器。因此,一个模块发生故障并不影响系统的正常工作,只有两个模块同时发生故障时,输出结果才会发生错误。

图3 TMR锁存器

3 表决器结构

本文列举的11种三模冗余锁存器主级全部是由3个同构的D锁存器构成,从级是由不同类型的表决器构成,下面分析11种不同的表决器结构。

3.1 传统表决器

3.1.1 表决器1

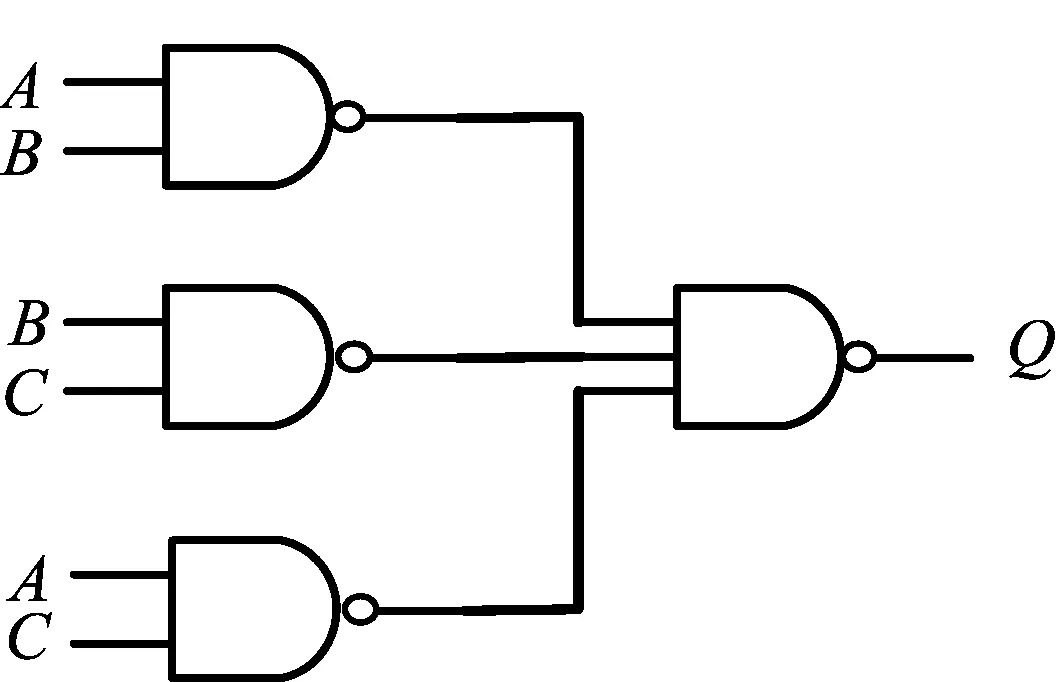

由表决器逻辑表达式(1)式可知[7],在门级上可以设计出由二输入“与”门和三输入“或”门构成的表决器1是由26个晶体管构成,结构如图4所示。

图4 表决器1

3.1.2 表决器2

由表达式F=AB+BC+AC=((AB)′(BC)′(AC)′)′可推出由二输入“与非”门和三输入“与非”门构成的同向表决器2,该表决器由18个晶体管构成,结构如图5所示。

图5 表决器2

3.2 晶体管级的表决器

晶体管级的表决器是由PMOS管和NMOS管组合构成,在本文的1.1节中介绍了“三中取二”表决器的逻辑表达式是F=AB+BC+AC,由于本文介绍的三模冗余锁存器主级输入输出是反向的,要使整体锁存器输入输出同向,则从级表决器也要是反向,因此可以直接写出反向“三中取二”表决器逻辑表达式F=A′B′+B′C′+C′A′,从而可以推导出表决器中P型网络的逻辑表达式为:

FP=A′B′+B′C′+C′A′。

N型网络的逻辑表达式为:

FN=(AB+BC+CA)′。

从而可以得到与之相对应的P型和N型网络结构图。同时本文又分别对P型和N型网络的逻辑表达式进行其他形式的化简,最终得到3种P型网络图和3种N型网络图。

本文对上述不同的晶体管结构进行自由组合,因此产生3*3=9种不同的表决器结构,如图6所示。9种不同的晶体管级表决器结构中,P1+N1型[8]、P1+N3型、P3+N1型3个表决器都由12个晶体管构成,P1+N2型、P2+N1型、P2+N3型、P3+N2型4个表决器由11个晶体管构成,P2+N2型表决器由10个晶体管构成。由此可以推断,由P2+N2型表决器构成的三模冗余锁存器的面积开销应该是最小的。

图6 自由组合过的晶体管级表决器示意图

从图6可以看出,P1+N1型、 P1+N2型、 P1+N3型、P2+N3型、P3+N3型5个表决器根据输入类型的不同,可能会经过2个或3个晶体管的延迟。以P1+N1型表决器结构为例,当输入ABC为000时,输入值是经过3个晶体管的延迟才能到达输出,当输入ABC为011时,输入值是经过2个N型晶体管的延迟到达输出。但P2+N1型、P2+N2型、P3+N1型、 P3+N2型4个表决器输入到输出都只经过2个晶体管的延迟,同时,在这4个结构之中,晶体管又分为串联和并联2种类型,2个并联的晶体管相当于增大了宽长比,延迟就会更大。因此可以得出,P2+N2型表决器结构的延迟是最小的,且由P2+N2型表决器构成的TMR锁存器性能最优。

4 三模冗余锁存器的仿真与分析

因为输入D通过3个相同的D锁存器后输出反向信号,为了保证TMR锁存器输出Q与输入D为同向信号,所以以下列举的锁存器中表决器都必须保持输入输出为反向。下面将上述列举的11种表决器结构与TMR锁存器主级进行连接,并使用Hspice仿真工具对这11种锁存器结构进行故障注入测试和功耗、延迟以及面积开销测试。

4.1 门级三模冗余锁存器

4.1.1 TMR1锁存器

TMR1锁存器从级是表决器1(结构如图4所示),由于该表决器同向,为了保证三模冗余锁存器的输入D与输出Q同向,可以将表决器中的“或”门改为“或非”门,此时表决器减少了2个晶体管。TMR1锁存器共由48个晶体管构成。结构如图7所示。

图7 TMR1锁存器

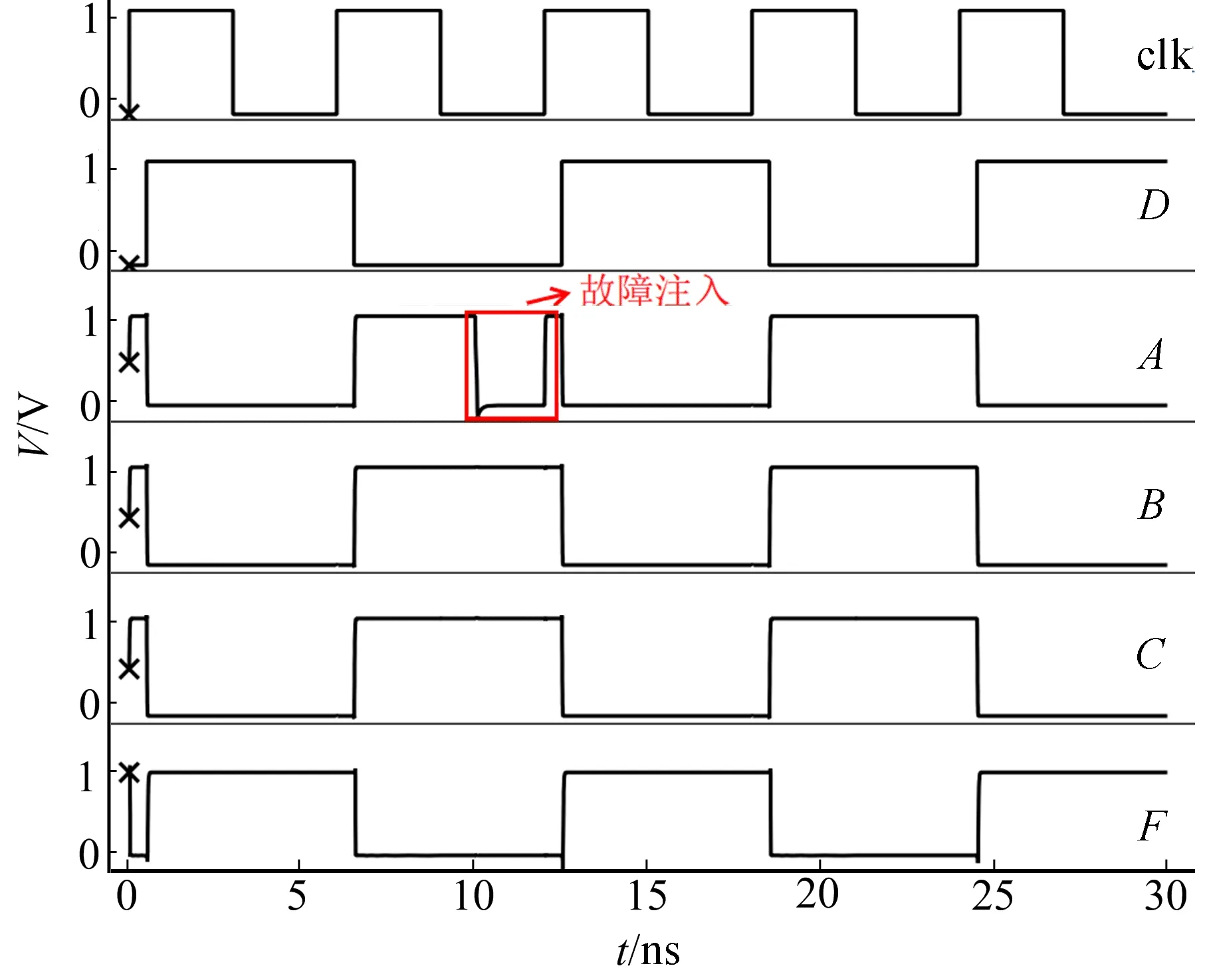

为了验证三模冗余锁存器的容错性能以及测试其延迟和功耗,从而计算出锁存器的面积开销和功耗延迟积(power delay product,PDP)。本文在PTM(predictive technology model) 45 nm工艺模型下[9],利用Hspice仿真工具,仿真环境设定为:电源电压1 V、温度25 ℃、时钟频率约167 MHz,采用双指数电流源模型模拟粒子轰击产生的瞬态脉冲。

应用Hspice进行仿真得到的波形图如图8所示。

图8 TMR1仿真波形图

从图8可以看出,在结构主级中,输入信号D经过一个反相器,输出3个反向信号A、B、C,再经过一个反向表决器,则得到与输入信号D同向的输出信号F。从图8可以看出,当输入信号D为高电平1时,A、B、C信号此时为低电平0,输出信号F为1。同样地,当输入信号为0时,输出信号也为0。

本文在节点A的10 ns处进行故障注入[10],从波形图可以看出,输出端Q并未受到影响,TMR锁存器完全容忍SEU。

4.1.2 TMR2锁存器

TMR2锁存器从级由表决器2构成(结构如图5所示),与TMR1锁存器一样,本结构的表决器也是同向的,因此将最后的三输入与非门改成了与门,此时增加了2个晶体管,共有44个晶体管。

该TMR2锁存器与TMR1锁存器波形图是一样的,也在10 ns时节点A处进行故障注入,能完全容忍SEU。

4.2 晶体管级三模冗余锁存器

由于都是三模冗余锁存器,本文中锁存器的主级都是一样的,从级是不同的表决器,相对应的节点都是与图8相同的波形。

晶体管级三模冗余主级和传统三模冗余锁存器的主级一致,从级是由图6所示的各种表决器构成的。按表决器的顺序分别记为TMR3~TMR11锁存器。与4.1节一致,在相同仿真条件下,对所有的锁存器进行Hspice仿真。

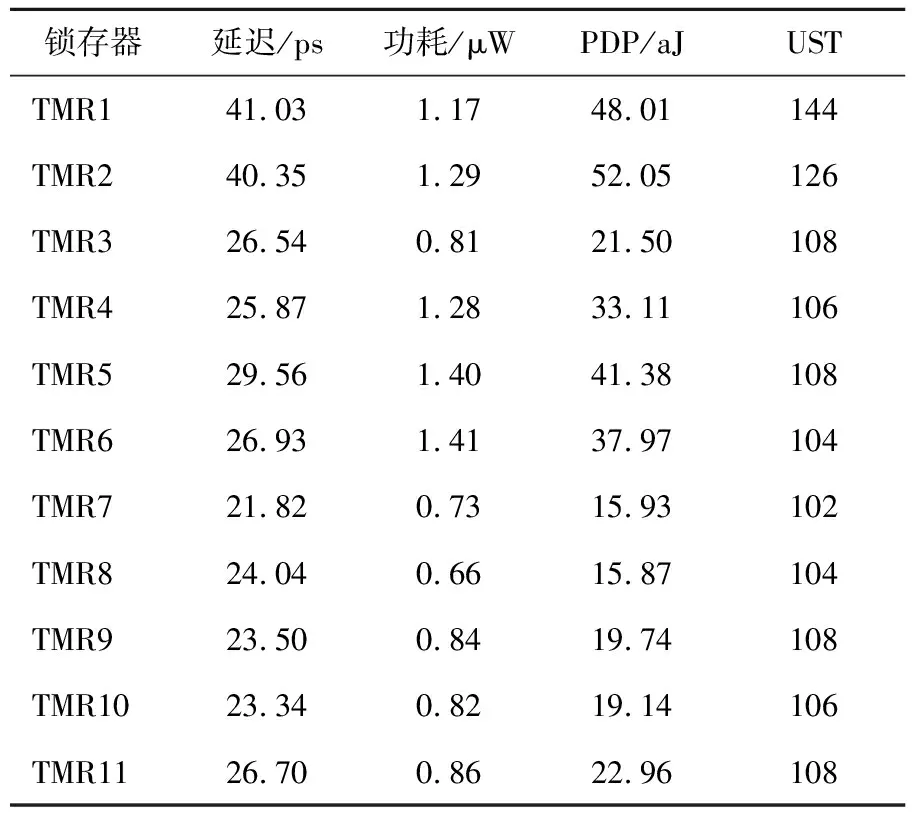

以下是各种TMR锁存器的仿真结果对比,见表2所列。

表2中,UST表示面积开销,UST、PDP的计算公式[11]如下:

由表2性能对比可知,在11种三模冗余表决器中,TMR7锁存器在延迟、功耗以及面积开销等性能上的指标都是最优的,由此也验证了3.2节中的理论分析,P2+N2型表决器的性能最优。

表2 TMR锁存器性能对比

5 结 论

本文对11种TMR锁存器进行了综合分析,介绍了三模冗余锁存器的构成、表决器的多种结构及思路来源,利用Hspice仿真工具测得各锁存器节点波形图、延迟和功耗;并且通过UST计算公式计算出TMR锁存器面积开销,通过PDP公式计算出功耗延迟积。经过综合对比发现,TMR7锁存器(使用P2+N2型表决器)的综合性能最优。