锁存器和触发器振荡问题分析

2015-07-04唐普英

唐普英

(电子科技大学光电信息学院,四川成都610054)

0 引言

时序逻辑电路是“数字逻辑设计及应用”课程的重要内容,也是数字系统的核心组成,锁存器和触发器则是时序逻辑电路的基本构件,而S-R锁存器是锁存器和触发器的构成基础。

锁存器和触发器振荡问题是指它们无法在某个规定时间段内达到一个可确认的状态。当它们进入振荡状态时,既无法预测其输出电平,也无法预测何时输出才能稳定。此时,这种无用的输出电平可以沿信号通道传播下去,从而扩大故障面,使问题难以处理[1]。

若要解决数字系统的振荡问题,则需探究S-R锁存器产生振荡问题的本质原因。

借助电路输入输出的时序关系,本文分析S-R锁存器出现振荡的原因,从而揭示锁存器和触发器产生振荡的本质机理。这一探讨有助于避免该问题的产生,也有助于数字系统的可靠性设计。

1 锁存器振荡问题剖析

1.1 S-R锁存器的振荡问题分析

由于S-R锁存器和S'-R'锁存器的功能等价关系,本文仅讨论S-R锁存器的振荡问题。为了方便分析,我们假设数字电路中各个门电路延时相同,均为2个单位时间并给定输入端信号时序,获得输出端信号时序,经电路延时和功能分析,得出结论。

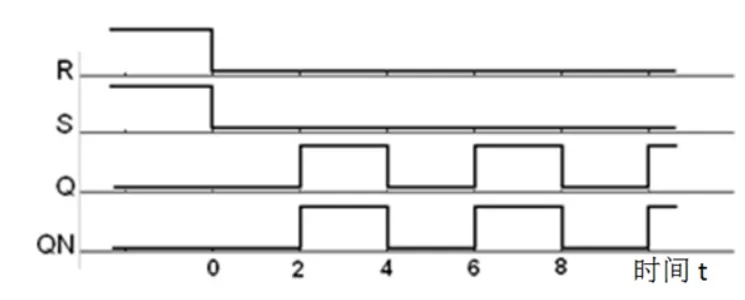

(1)从SR=11到SR=00时产生振荡状态

S-R锁存器如图1所示。当S=1,R=1时,即输入S和R同时有效,可得到Q=0,QN=0。在时间t=0+时,S=0,R=0,即输入S和R同时取消,R、S端同时为0,则经1个门延时后(即:时间t=2+时)Q=1,QN=1,并同时反馈到两个或非门的输入端,此时两个或非门的两个反馈输入端同时为1。再经过1个门延时后(即:时间t=4+时)Q=0,QN=0。锁存器输出Q和QN就这样振荡下去,在两个或非门的延时绝对相等的条件下,S-R触发器便进入振荡状态。

图1 S-R 锁存器[2]

图2 SR从11到00时出现振荡状态

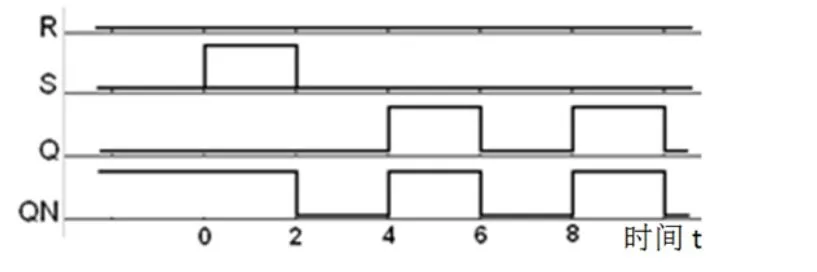

(2)窄脉宽时出现振荡状态

原始状态时如图3所示,输入R=S=0,锁存器Q=0,QN=1。时间t=0+时,S端输入一个宽度为2个单位时间(假设该脉冲宽度小于要求的最小脉冲宽度,应为门延时的2倍)的正脉冲,经过1个门延时后(时间t=2+)QN=0,此时由于R=0,经过1个门延时后(时间t=4+)Q=1。由于时间t=2+时S=0,并且此时Q=0,因此经过1个门延时后(时间t=4+)QN=1。故在时间t=4+时Q和QN同时等于1,此时输入S和R都已等于0。此后的时序图就与上述从SR=11到SR=00的情形一样,一直振荡下去。

图3 S端施加的窄脉宽时出现振荡

图4所示为在输入端S=0,在输入端R施加一个窄脉宽正脉冲时出现振荡状态的情形。表明:SR锁存器中,只要一个输入端保持低电平(即:该端输入电平无效),另一个输入窄脉宽脉冲时就会出现振荡。图5所示是输入S=0,输入R的脉冲宽度足够宽(即:大于要求的最小脉冲宽度)时不出现振荡状态的情形。

图4 R端施加窄脉宽脉冲时出现振荡

图5 R端施加的脉宽够宽时不出现振荡

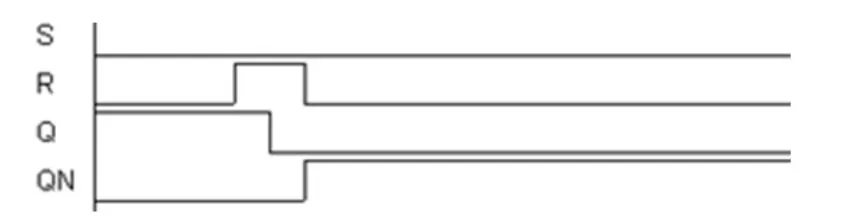

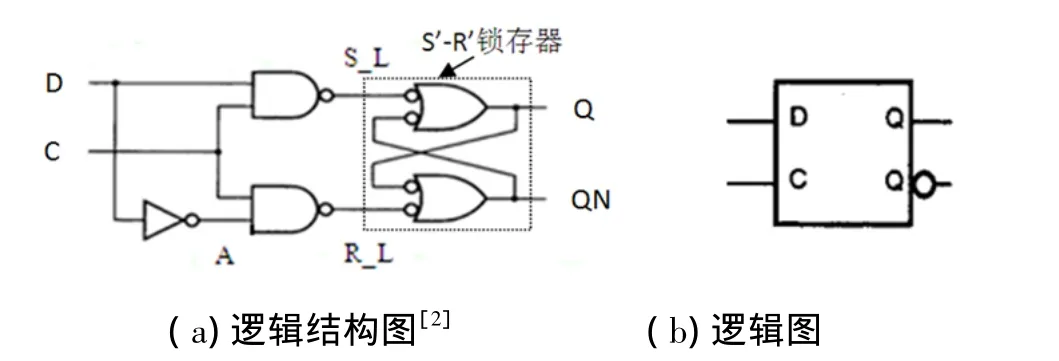

1.2 D锁存器的振荡问题分析

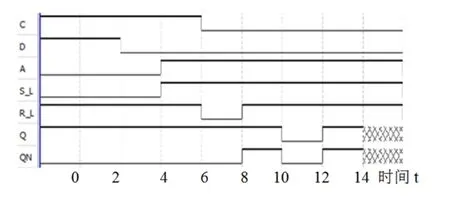

图6(a)是D锁存器的逻辑结构图,图6(b)是D锁存器的逻辑图。实际上,图6(a)右端虚线框内的两个非或门就是S'-R'锁存器(其实S'-R'锁存器与S-R锁存器的功能是一样的,前者表示低电平输入有效,后者表示高电平输入有效)。图7是图6(a)中各点的时序图,其中t=2时输入D由1→0,t=6时使能输入C由1→0。从图7可以看到,由于R_L的负脉冲宽度只有2个单位时间,不满足最小脉冲宽度的要求,导致图6(a)中S'-R'锁存器输出呈现振荡状态,图7中的阴影部分表示振荡状态一直持续下去。

图6 D锁存器

图7 D锁存器结构图中各点的时序图

图7之所以出现振荡状态,是因为D锁存器存在建立时间(setup time)的缘故,即:输入D在锁存器的使能输入C的下降沿之前的一小段时间(称为建立时间)内不能变化。因此,D锁存器输入端不满足建立时间关系,而造成振荡输出的本质原因是其中的S'-R'锁存器的输入脉冲宽度不满足要求。

由图6(a)可以看出,当使能信号C为低电平时,与C连接的两个与非门被关闭。考虑到该两个与非门的时延,C下降沿后再经历一小段时间(称为保持时间,hold time)才能彻底关闭两个与非门。因此,输入D在锁存器的保持时间内也不能变化,才能避免出现振荡状态。由此可见,在D锁存器的建立时间和保持时间内,输入信号D不能变化。

如图8所示,输入C的时序关系不变,而输入D由1→0的时刻提前到t=0,R_L的负脉冲宽度是4个单位时间,满足最小脉冲宽度的要求,锁存器的输出稳定。如图9所示,输入C的时序关系不变,而输入D由1→0的时刻移到t=8,R_L不存在负脉冲,锁存器的输出也稳定。

图8 t=0时D由1→0,输出稳定

图9 t=8时D由1→0,输出稳定

2 触发器振荡问题的剖析

触发器分为D、JK和T三种类型,由于JK触发器和T触发器均可通过D触发器转换得到[3]。因此下面仅讨论D触发器的振荡问题。

图10是D触发器(上升沿触发)内部结构图,它是由两个D锁存器构成。由上述讨论知道,当输入D不满足锁存器的建立时间和保持时间的关系时,将产生振荡。可见D触发器的输入时序不满足要求时也将出现振荡问题。但从触发器、锁存器和S-R锁存器的组成关系看,触发器的振荡问题归根结蒂还是S-R锁存器的振荡问题。

图10 D触发器内部结构图

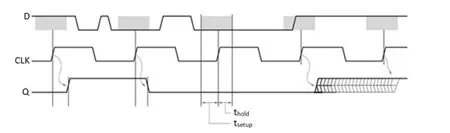

图11是D触发器(上升沿触发)的时序图,时钟CLK的前3个上升沿对应的输入满足了建立时间和保持时间的要求,输出稳定的状态;时钟CLK的第4个上升沿对应的输入不满足建立时间和保持时间的要求,输出呈现振荡状态(如图11中波形Q的阴影部分所示);时钟CLK的第5个上升沿对应的输入满足建立时间和保持时间的要求,输出稳定的状态。

图11 D触发器(上升沿触发)时序图

3 结语

从上述分析可以得出:触发器的振荡问题归根结蒂是S-R锁存器的振荡问题。S-R锁存器出现振荡有两种原因:①S-R锁存器输入端S和R从同时有效变为同时无效;②锁存器输入端S或R的脉冲宽度不够。

触发器出现振荡状态的原因是输入不满足建立时间和保持时间关系,其根本原因则是S-R锁存器输入端S或R的脉冲宽度不够。

[1]http://baike.baidu.com/view/931945.htm?fr=aladdin.

[2]John F.Wakerly.数字设计原理与实践(原书第4版)[M].林生,葛红,金京林 译,北京:机械工业出版社,2007年5月.

[3]杨方.对触发器逻辑功能转换的分析[J].长春:长春大学学报,2012,22(6):644-646.