平板式外延炉大尺寸硅外延层的均匀性调控

2017-03-30李明达李普生

李明达,陈 涛,李普生,薛 兵

平板式外延炉大尺寸硅外延层的均匀性调控

李明达,陈 涛,李普生,薛 兵

(中国电子科技集团公司 第四十六研究所,天津 300220)

硅外延层是在硅单晶抛光衬底上采用化学气相沉积方法生长的一层单晶硅薄膜。本实验以150 mm的大尺寸硅抛光片为衬底生长高均匀性外延层,结合傅里叶变换红外线光谱分析(FT-IR)、电阻率测试仪等测试设备对外延层电学参数进行了分析。对平板式外延炉的流场、热场与厚度、电阻率均匀性的相互作用规律进行了研究,最终制备出表面质量良好、片内和片间不均匀性小于1%的外延层。

硅外延层;化学气相沉积;厚度;电阻率;均匀性;缺陷

硅外延层是采用化学气相沉积法在硅抛光衬底上生长的一层单晶硅薄膜,具有厚度和掺杂浓度可精确调控、结晶完整性好等特点,在高端电力电子器件应用方面具有无可取代的优势[1-2]。由于外延层的质量管控水平与器件产出参数的一致性与可靠性密切相关,因此进一步提升外延层的性能已经成为极为迫切的研究课题。

当前随着高端电力电子器件向高频高压、低功耗、大电流、轻薄短小的方向发展,面临越来越快的更新速度,对所需外延层的性能要求愈高[3]。尤其在器件成本和良率的双重驱动下,外延层尺寸的主流供应规格已从125 mm扩大到150 mm,晶圆面积随之扩大1.44倍,同时器件加工过程中对边缘去除的区域不断减少,单位晶圆利用率不断提高,要求片内参数离散性越来越低,由此对外延层片内电参数的均匀性提出了严格的要求[4]。以单个VDMOS管为例,通常由成百上千个元胞并联而成,其中任何一个元胞的失效都会引发整个MOS管失效,进而导致电力工作系统的异常[5]。因此片内元胞工作电压的主流规格已从20 V的容限收严到10 V,相对应地要求外延层片内和片间不均匀性已经从≤2%的容限收严到≤1%[6-7]。外延层面积的扩大,均匀性要求的提高,对外延层特别对于MOS功率器件用厚层高阻外延片来说是极大的挑战[8]。基于厚层高阻外延本身生长时间较长,而且外延层与衬底掺杂浓度相差超过4个数量级,轻微的非主动掺杂效应就会影响对外延层电阻率均匀性的管控[9],因此不均匀性从2%的容限收严至1%的容限,这就需要对外延流场和热场进行更加精确的调控,同时还要避免外延层表面质量的下降。本文对平板式外延炉的热场、流场与外延层厚度、电阻率均匀性的作用规律分别进行了详细研究,通过对中间进气口的H2流量的精确调节和基片径向温度梯度的调节实现了MOS管用150 mm大尺寸硅外延层厚度和电阻率的片内和片间的不均匀性全部小于1%的目标要求。

1 实验

1.1 设备

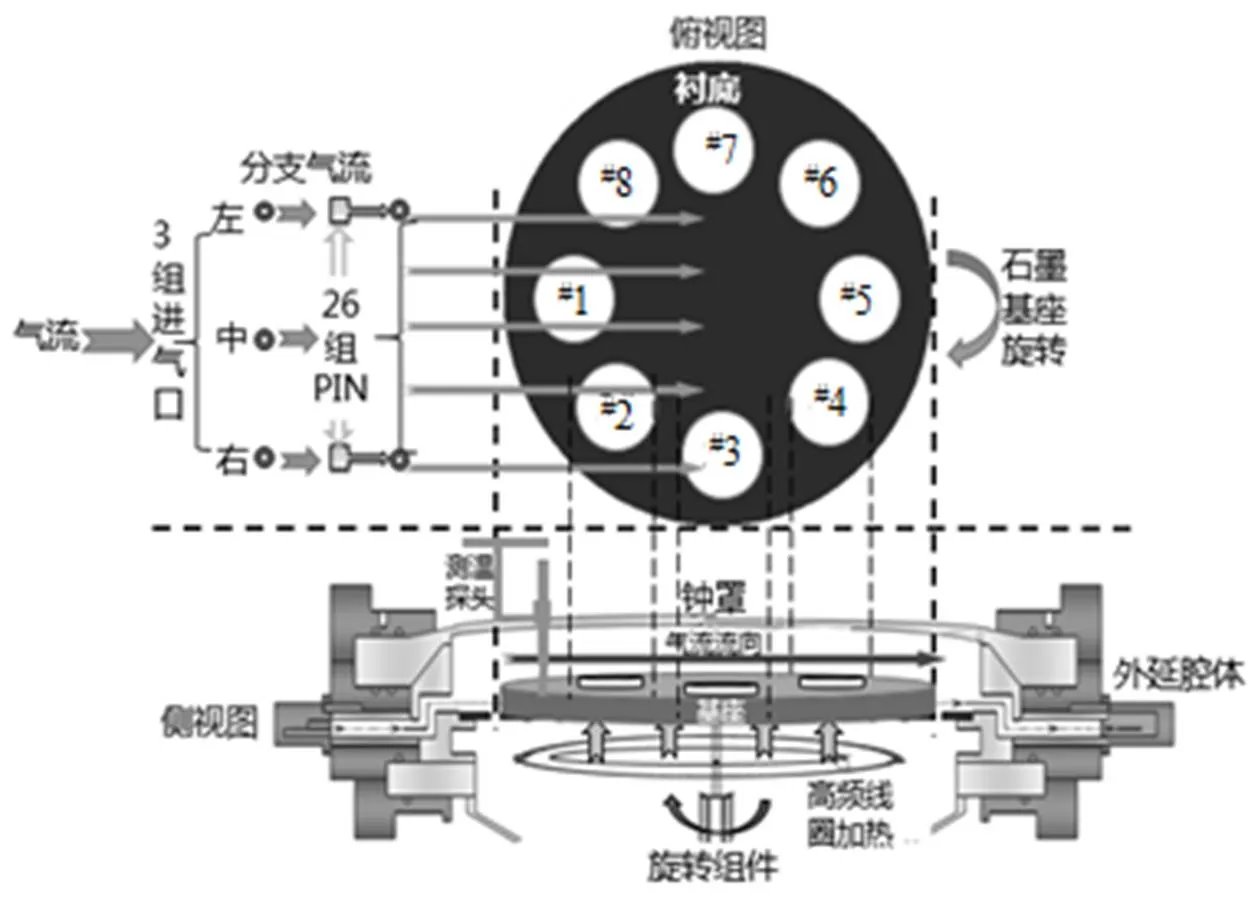

采用高频感应加热的平板式常压外延炉作为硅外延层的沉积设备。外延腔体由石墨基座、石英组件、镀金钟罩、进气管路、加热线圈等组成,基本结构如图1所示。单圈石墨基座可水平放置8片150 mm硅衬底片,设为#1~#8样片,生长过程中基座由底部的旋转组件带动可沿顺时针方向匀速转动。本实验中基座的旋转速度设定为4 r/min。基座下方均匀分布着五条螺旋排列的加热线圈,线圈底端设有高度调节杆,可精确控制线圈与基座的距离。外延炉内安装有沿基座径向运动的测温探头,可以精确测量温场分布,进而作为外延热场调节的监控手段。

图1 选用的外延炉结构示意图

反应气流从腔体左侧三个进气口(分为左、中、右)通入,进气口处安装有高精度的气体体积流量计,精度可达0.01 L/min,随后气流再从平行排列的26组喷嘴(PIN口)进入反应腔体。实验中主要通过调节三个进气口处的气流旋钮来控制进气流量,进而调控外延流场。反应气流的运动方向平行于基座表面,在硅衬底片表面反应并沉积生长外延层后,产生的尾气从右侧排出反应腔体。

1.2 生长原料及外延制备

使用的衬底材料为直径(150±0.2) mm硅单晶抛光片,厚度为(400±25) μm,电阻率为0.01~0.02 Ω•cm,导电类型为N型,衬底背面包覆有(500±50) nm的SiO2背封层。所制外延层的导电类型为N型,厚度为46.7×(1±1%) μm,电阻率为10.6×(1±1%) Ω•cm,片内不均匀性要求<1%,片间不均匀性要求≤1%,外延表面质量要求无滑移线、雾等缺陷。

沉积硅外延层所需化学气体主要包括三氯氢硅(SiHCl3)、磷烷(PH3)和氢气(H2)。SiHCl3纯度为5N,其本征电阻率高于1 000 Ω·cm。H2经纯化后纯度为6 N,其作用为通过高温化学反应将SiHCl3还原为单晶Si,同时作为载气将原料气体携带入反应腔室。PH3作为外延掺杂源,经H2稀释后的体积浓度为50×10–6。

1.3 材料性能表征

外延层表面质量首先在照度高于200 lux的白色聚光灯下目检。表面缺陷由日本Olympus公司的BH-2微分干涉相差显微镜观察。外延层的厚度由美国Thermo公司的Nicolet IS10型傅里叶变换红外光谱测试仪(FT-IR)扫描测试。外延层电阻率由匈牙利Semilab公司的MCV-530L型汞探针测试系统扫描测试。在测试前N型外延片首先在HF溶液中浸泡3 min以除去表面生成的自然氧化层,然后置于质量分数15%的85℃H2O2溶液中浸泡10 min,取出后经表面甩干、测试。外延层电参数测试过程中采用5点测试法,即选择硅片的中心点及4个距边缘10 mm的位置作为测试位置。

本文中厚度或电阻率的不均匀性STD(%)的定义为(Thkmax–Thkmin)/(Thkmax+Thkmin)×100%,其中Thkmax和Thkmin代表厚度或电阻率测试数据中的最大值和最小值。

2 结果与分析

2.1 厚度均匀性控制

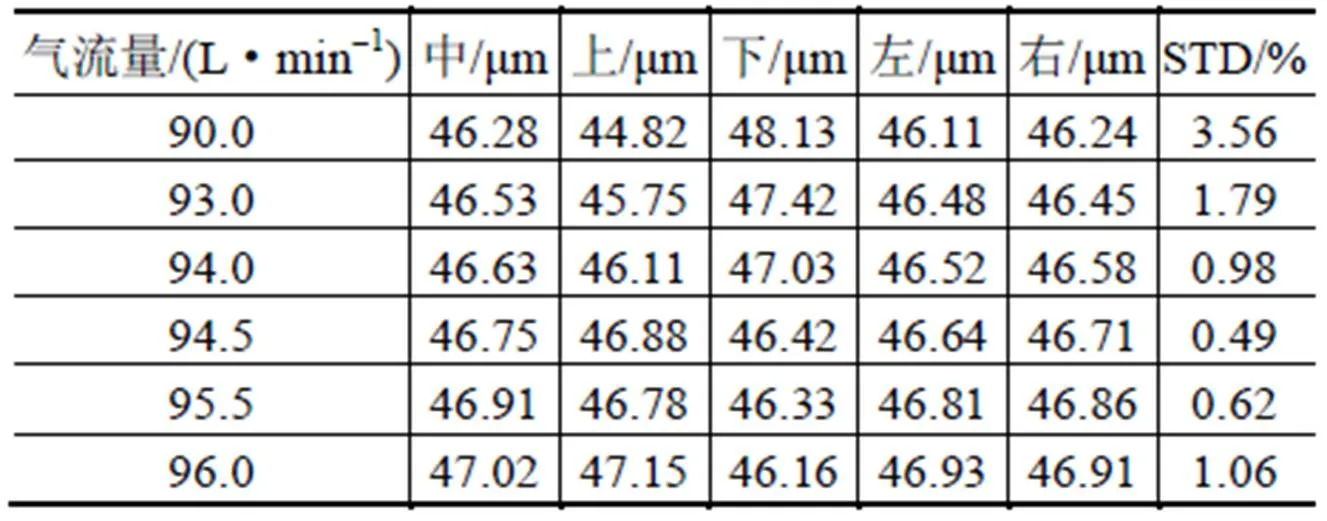

外延炉内的流场分布限定了气体分压,进而决定了外延层厚度及其均匀性。实验中通过调节主工艺气流H2在三个进气口的分配量,观察对厚度均匀性的影响。以中间进气口的流量为设定变量,左右两侧的气流量分别调节为(总工艺气流量-中间进气口的流量)/2。实验中主工艺气流H2的总流量设定为150 L/min,先后将中间进气口的H2流量分别设定为90.0,93.0,94.0,94.5,95.5和96.0 L/min,实验得到的片内厚度分布及不均匀性结果如表1所示。

表1 片内厚度不均匀性与工艺气流量的关系

Tab.1 Relation between the thickness non-uniformity in the chip and the process gas flow

由于H2流量在各个进气口的分配量影响SiHCl3气体在反应室内的携带量和分压,进而影响了基片内生长速率的分布,因此对厚度均匀性进行了调节。表1结果表明中间进气口的气体流量对厚度均匀性起重要的作用,随着中间进气口流量的增加,片内上点厚度随之增加,而厚度不均匀性呈现先减小后增大的趋势。当H2流量为94.5 L/min时得到的片内厚度不均匀性最小,为最佳工艺流量值,H2流量设定94.0~95.5 L/min都可以满足不均匀性小于1%的目标要求,在94.5 L/min的最优条件下得到的炉内8片测试片厚度分布如表2所示,各片的片内厚度的不均匀性均<1%,厚度均值偏差为0.17 μm,相应片间厚度均值的不均匀性仅0.18%,炉内点间不均匀性仅0.71%,均满足<1%的要求。

表2 炉内各外延片的片内厚度分布以及不均匀性

Tab.2 Thickness distribution and non-uniformity of the epitaxial wafers in the same furnace

2.2 电阻率均匀性控制

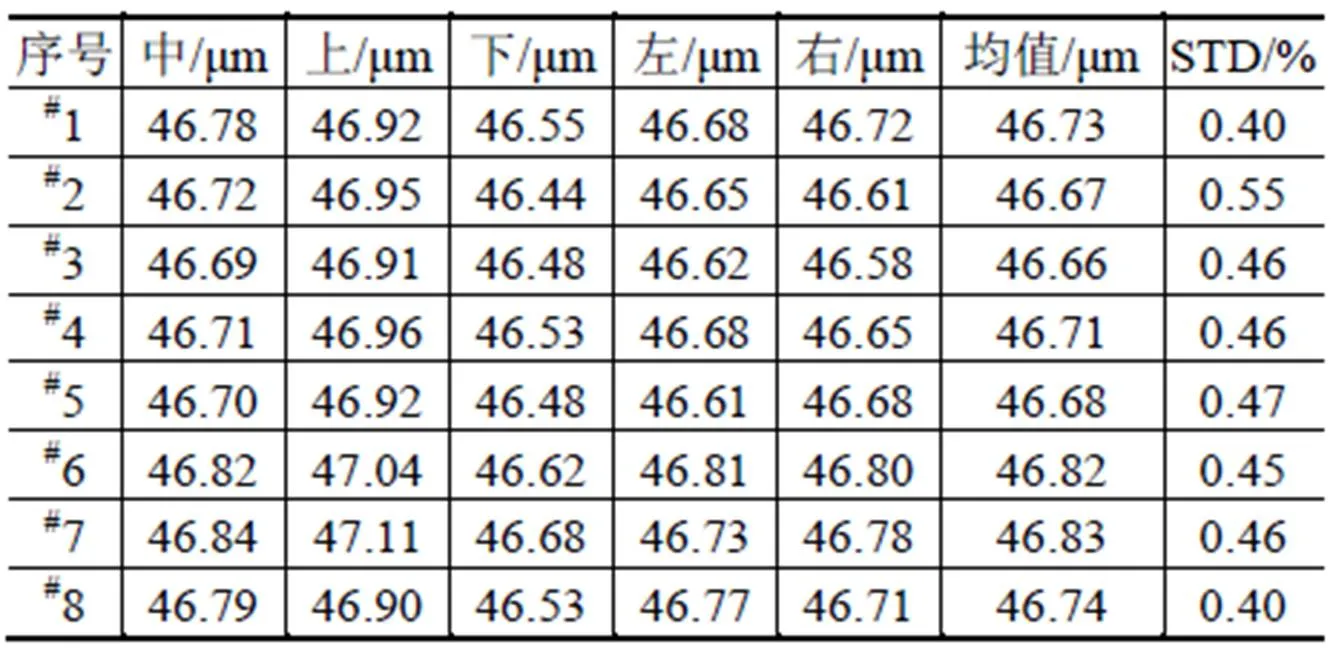

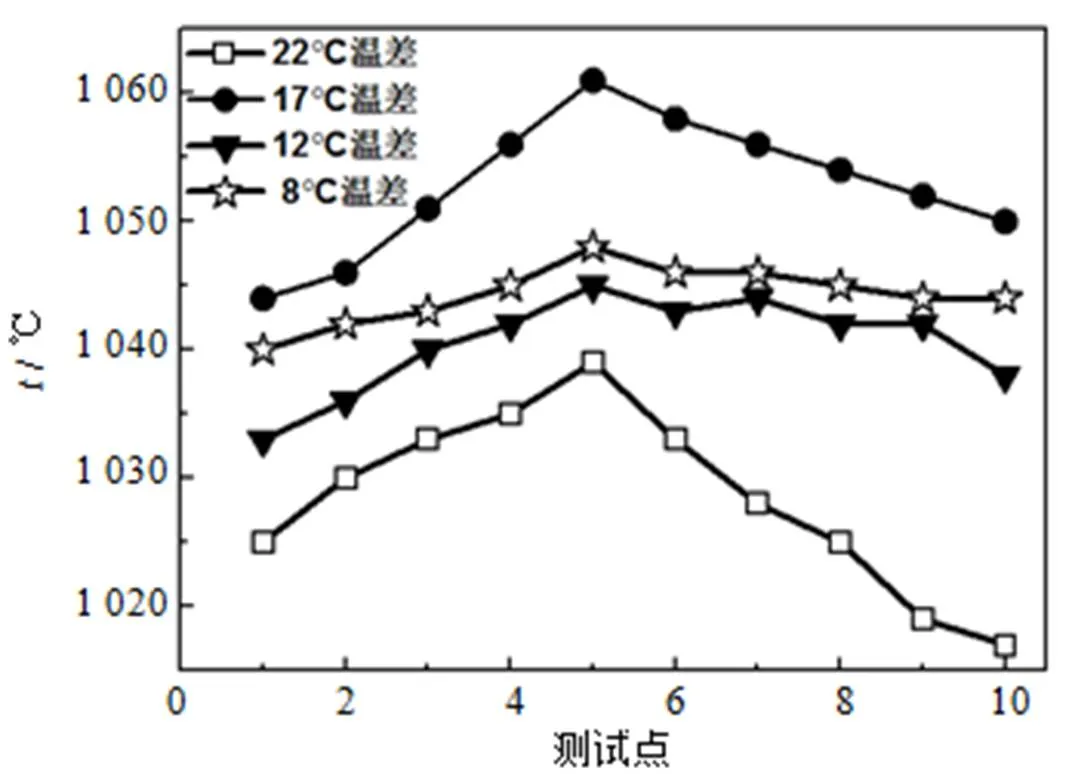

由于生长温度与掺杂剂的掺入效率密切相关,直接影响着外延层电阻率以及均匀性。图2为根据外延反应腔体的热场特点,推断外延层电阻率的5点测试点与#1~#5加热线圈的对应位置关系。根据使用的基座与线圈位置的特点,沿基座径向设置等距20 mm的10个测试点,用以实时测试基座温度。通过调节线圈的高度改变基座的工作温度,进而获取基座径向温度分布与电阻率均匀性的对应关系。实验研究了线圈在调节不同高度后得到的温度分布与电阻率不均匀性测试结果,分别如图3和表3所示。

图2 电阻率测试位置与线圈位置对应关系的示意图

图3 各测试点温场分布图

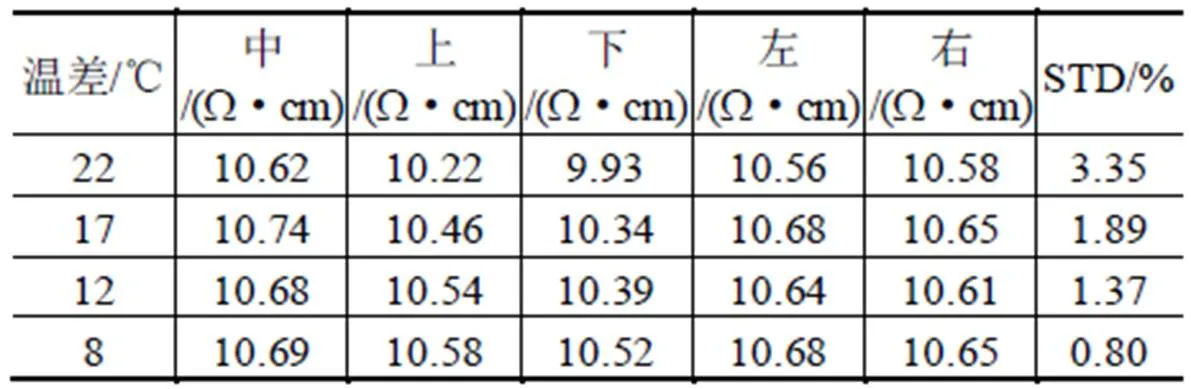

表3 采用不同径向温度分布的外延层电阻率及其不均匀性

Tab.3 The epitaxial layer resistivity and non-uniformity of the epitaxial wafers using different radial temperature distribution

当温度差为22,17,12,8℃进行实验时,结果表明,采用基座径向温度更趋均匀的分布对电阻率均匀性的改善效果越好,当10个测试点的温度偏差为8℃时,电阻率不均匀性可以实现小于1%的目标要求,而当测试点的温度偏差大于8℃时,电阻率不均匀性呈现逐渐增大趋势,不能满足目标要求。

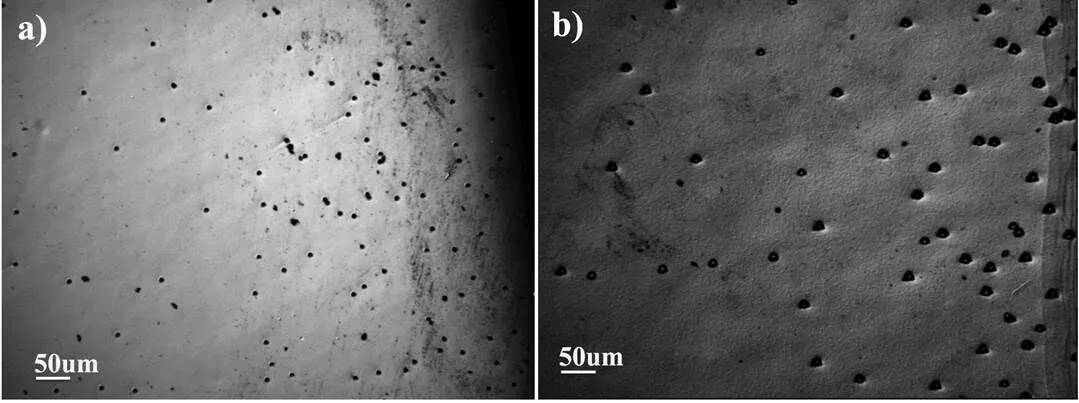

实验中发现工艺温度及其分布深刻影响外延表面质量。当温差较大出现低于1 020℃的温度时,在强光灯下发现该区域的外延表面分布红色的雾状缺陷,经Schimmel腐蚀液处理后在显微镜下可发现一些微缺陷蚀坑。当温差较大,出现高于1 060℃的温度时,在强光灯下发现该外延层区域存在滑移线缺陷,经同样腐蚀液处理后在显微镜下可发现一些尺寸较大的蚀坑。在200倍显微镜下观察到的雾和滑移线的典型缺陷形貌图分别如图4(a)和(b)所示。

图4 外延层上(a)雾和(b)滑移线缺陷的表面形貌

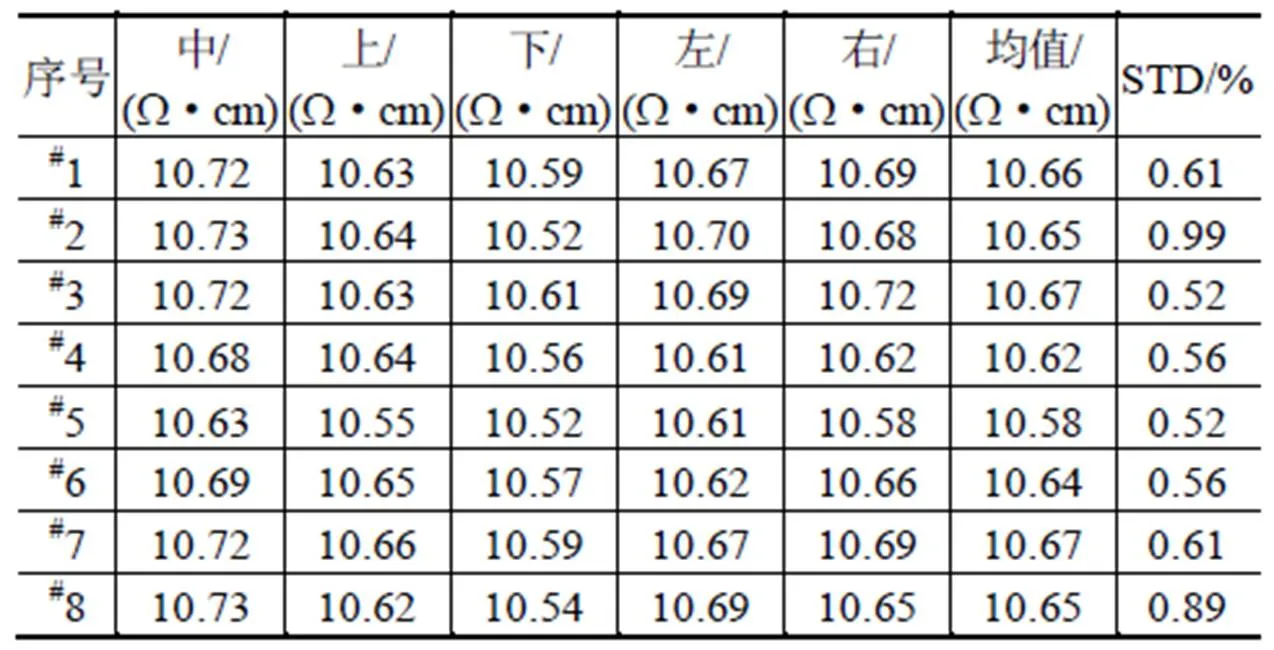

上述缺陷的出现原因可能与外延沉积温度有关,当外延温度过低,则造成气源反应不充分,表面微缺陷出现的概率增加,在强光灯下微缺陷发生散射形成观感上的雾状表面。相反,沉积温度过高,加之硅片各处温度不均,产生温度梯度,引入的热应力释放不力影响了晶格生长质量,便产生了滑移线缺陷。当采用的温差为8℃时表面观察无雾、无滑移线等缺陷,在该条件下得到的炉内8片测试片电阻率分布如表4所示,结果表明炉内各片的片内电阻率的不均匀性<1%,各片电阻率均值的偏差值为0.11 Ω·cm,相应片间均值不均匀性为0.52%,炉内各测试点的点间不均匀性为0.98%,均满足<1%的要求。上述厚度和电阻率测试结果表明在优化后的热场和流场条件下,本实验制备的厚层高阻外延层在片内和片间参数管控上呈现较好的一致性,提高了成品率和所制器件的良率。

表4 炉内各外延片的电阻率分布以及不均匀性

Tab.4 Resistivity distribution and non-uniformity of the epitaxial wafer in the furnace

3 结论

研究了基于平板式外延炉生长的150 mm大尺寸硅外延层的厚度、电阻率均匀性与外延流场和热场的作用规律。针对制备的厚层高阻外延层的参数特点,首先研究了进气流量的分布与厚度均匀性的关系,研究发现随着中间进气口H2流量的增加,片内上点厚度随之增加,而片内的厚度不均匀性呈现先减小后增大的趋势,最终优化的外延层流场实现了片内和片间厚度不均匀性全部小于1%的目标。其次研究了线圈高度对石墨基座温度的调节与电阻率均匀性的对应关系,片内电阻率测试值随对应线圈高度增加而降低,随线圈高度降低而增加,非主动掺杂效应在优化后的外延热场下得到了有效控制,从而实现硅外延层片内和片间电阻率不均匀性全部小于1%的目标。

[1] HABUKA H, TSUJI M. Silicon epitaxial growth rate and transport phenomena in a vertical stacked-type multi-wafer reactor [J]. Jpn J Appl Phys, 2012, 51: 026701.

[2] MATSUI M, HABUKA H. Numerical evaluation of silicon epitaxial growth on a 450 mm diameter substrate [J]. Phys Status Solid A, 2015, 212(7): 1539-1543.

[3] SHAHRJERDI D, HEKMATSHOAR B, BEDELL S W, et al. Low-temperature epitaxy of compressively strained silicon directly on silicon substrates [J]. J Electron Mater, 2012, 41(3): 494-497.

[4] SHINRIKI M, KEITH C, HASAKA S, et al. Gas phase particle formation and elimination on Si (100) in low temperature reduced pressure chemical vapor deposition silicon-based epitaxial layers [J]. Thin Solid Films, 2012, 520: 3190-3194.

[5] 徐非. VDMOS功率场效应管外延材料的研究[D]. 南京: 东南大学, 2010.

[6] 高航, 王文林, 薛兵, 等. 低功耗VDMOS器件用硅外延片工艺研究 [J]. 科技创新与应用, 2014, 31: 12-13.

[7] 干红林, 冯全源, 王丹. 高压功率VDMOS元胞的研制 [J]. 电子元件与材料, 2015, 34(2): 47-49.

[8] MARTIN I T, TEPLIN C W, DOYLE J R, et al.Physics and chemistry of hot-wire chemical vapor deposition from silane: measuring and modeling the silicon epitaxy deposition rate [J]. J Appl Phys, 2010, 107: 054906.

[9] LEE K S, YOO D H, HAN J J, et al. Selective epitaxial growth of silicon for vertical diode application [J]. Jpn J Appl Phys, 2010, 49: 08JF03.

(编辑:陈渝生)

Uniformity adjust and control of large-area Si epitaxial layer based on planar epitaxial furnace

LI Mingda, CHEN Tao, LI Pusheng, XUE Bing

(The 46th Research Institute of China Electronics Technology Group Corporation, Tianjin 300220, China)

Silicon epitaxial layer is a kind of mono crystalline silicon thin film, which deposites on the surface of the polished silicon substrate by using chemical vapor deposition method. In this study, using 150 mm large size silicon polished wafer as the substrate, with epitaxial layer high uniformity was deposited. Combining with epitaxial electrical parameters by using Fourier transform infrared spectroscopy (FT-IR) and resistivity testing apparatus, the relationship between flowing field, thermal field of the planar epitaxial furnance and uniformity of thickness, resistivity was studied. Finally, the epitaxial layer with good surface quality and non-uniformity less than 1% was prepared successfully.

Si epitaxial layer; chemical vapor deposition; thickness; resistivity; uniformity; defect

10.14106/j.cnki.1001-2028.2017.03.008

TN304

A

1001-2028(2017)03-0038-04

2016-12-20

李明达

李明达(1988-),男,天津人,工程师,主要从事硅外延材料的理论和工艺研究,E-mail: limingda@tju.edu.cn。

http://kns.cnki.net/kcms/detail/51.1241.TN.20170310.1142.008.html

网络出版时间:2017-03-10 11:42