应用于高速串行链路的噪声预测部分响应最大似然均衡

2017-02-09张银行胡庆生

张银行 胡庆生

(东南大学射频与光电集成电路研究所, 南京 210096)

应用于高速串行链路的噪声预测部分响应最大似然均衡

张银行 胡庆生

(东南大学射频与光电集成电路研究所, 南京 210096)

为了解决25 Gbit/s及以上的高速串行信号在背板信道传输中的信号完整性问题,研究了能够在高速率和低误码率(BER)之间取得折中效果的部分响应最大似然(PRML)均衡.基于噪声预测法,推导出能够有效降低硬件开销的噪声预测PRML均衡.在具有不同衰减特性的背板信道和不同调制方式下,采用判决反馈均衡(DFE)、PRML均衡和噪声预测PRML均衡3种均衡方式对误码率性能和硬件复杂度进行了研究分析.结果表明,对于25 Gbit/s 的非归零(NRZ)信号,噪声预测PRML均衡的误码率性能优于DFE和PRML均衡;而对于12.5 Gbit/s 的四电平脉冲振幅调制(4PAM)信号,PRML均衡的误码率性能优于DFE均衡;噪声预测PRML均衡的硬件复杂度优于PRML均衡,更适合应用于高速串行链路中.

信号完整性;噪声预测;硬件复杂度;串行链路

随着信息技术的快速发展,数据在背板的传输速度越来越高.高速并行传输时,信道间的串扰和时钟信号抖动的制约导致并行传输无法满足高速传输的要求.抗干扰强、传输速率高的串行传输逐渐成为高速背板通信的主流,但是由于背板的趋肤效应和介质损耗,高速串行传输时码间干扰(ISI)比较严重.目前,主要采用均衡技术和多电平调制技术来解决背板高频衰减导致的码间干扰问题.常用的均衡技术包括线性均衡(LE)和非线性均衡.线性均衡结构简单,既可消除前向ISI,也可消除后向ISI,因而得到了广泛应用,但是对于高速信号或者高损耗信道,其均衡效果较差[1-2].基于非线性均衡技术的判决反馈均衡(DFE)能够较好地消除后标,抗噪性能好,但是不能消除前标,且存在错误传播问题[3-4].多电平调制可以有效降低对信道带宽的要求,例如,当4PAM信号与NRZ信号的传输速率相同时,前者的比特率为后者的1/2,因而更利于高速信号的传输.然而,多电平信号存在噪声容限下降问题,为了获得与NRZ信号相同的电压裕度,4PAM信号需要额外增加9.54 dB的能量[5].

与传统均衡技术不同,作为一种折中技术,部分响应最大似然(PRML)均衡可以同时获得较高的电压裕度和较低的误码率.该技术并非尽可能消除码间干扰,而是将接收到的信号均衡为已知的部分响应信号,并通过最大似然序列检测(MLSD)技术恢复出可能的发送信息.本文研究了NRZ和4PAM两种调制方式下应用于高速背板的PRML均衡方案.

1 高速串行链路均衡系统

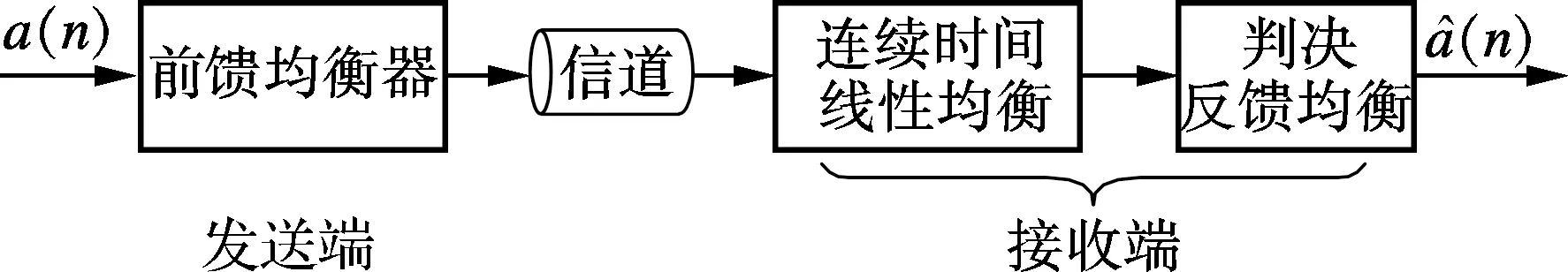

图1 高速串行链路均衡系统

发送端均衡可以采用预加重(提高数据a(n)的高频成分)或去加重(衰减数据a(n)的低频成分)方式实现,目的是使均衡后高低频比例调整到合理水平.然而,发送端均衡无法消除由于串扰和反射引起的码间干扰.速率较高时,串扰和反射引起的码间干扰特别严重,因此需要在发送和接收端联合采用均衡技术.

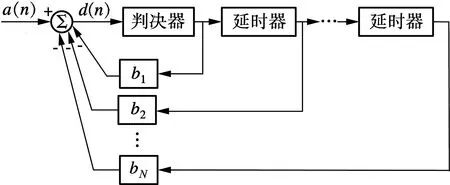

接收端均衡包括连续时间线性均衡(CTLE)和DFE.前者通过提高信号的高频成分来消除信道带宽受限引起的码间干扰,对消除前标和后标均有效;其缺点是会潜在地放大噪声和串扰,当信号频率高、信道衰减大时,效果不甚理想.后者属于非线性均衡,可有效消除后标,但不能消除前标,因而往往需要与CTLE配合使用.DFE的错误传播现象也是需要注意的问题[8].如图2所示,DFE主要由判决器、延时器和加法器组成.输出信号d(n)为

(1)

式中,N为抽头个数;bm为抽头系数,可通过信道的冲激响应获取,也可以通过自适应算法获得.

图2 DFE结构

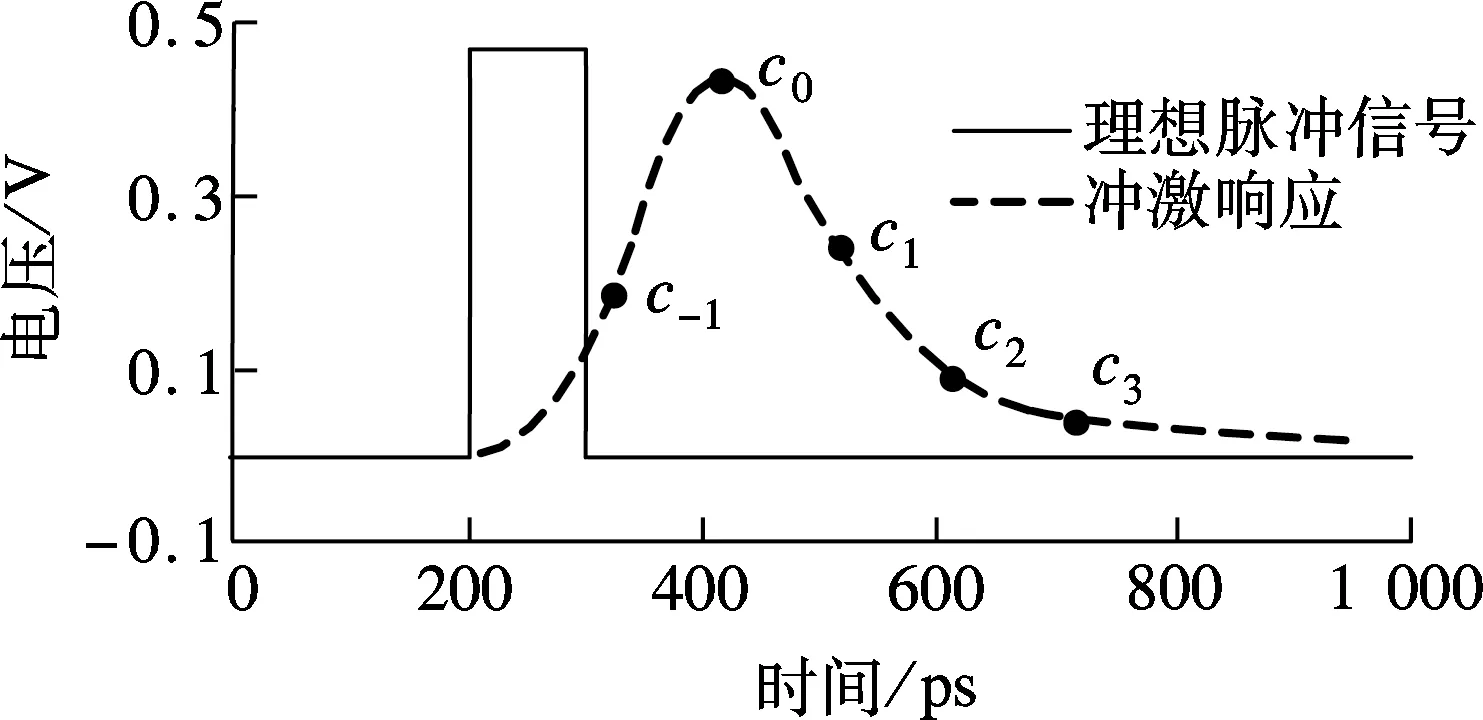

信道冲激响应如图3所示.图中,c-1为前标;cm(m=1,2,3)为后标.令式(1)中的抽头系数bm=cm(m=1,2,3),即可有效消除后向码间干扰.由图可知,理想脉冲信号经过信道被拓宽和衰减.

图3 信道冲激响应

2 PRML均衡

2.1 总体结构

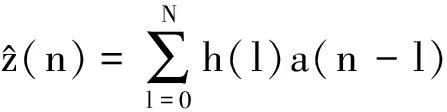

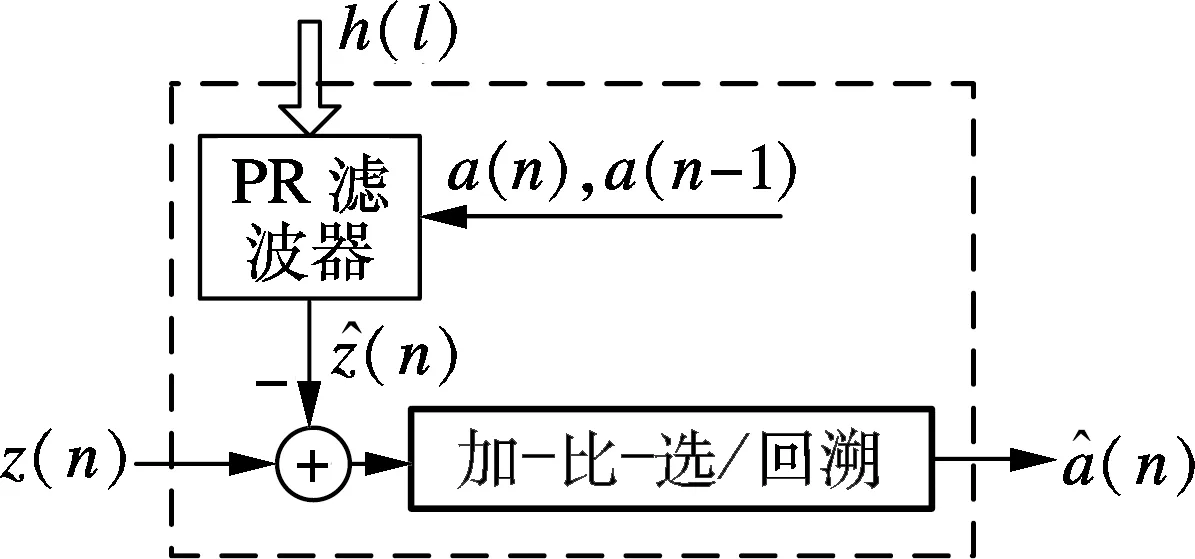

(2)

式中,h(l)为PR滤波器的系数,可通过自适应DFE获取.

图4 PRML均衡

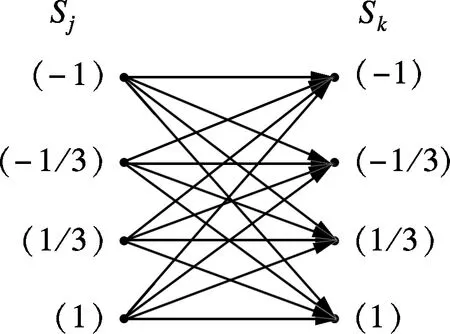

Viterbi译码是一种最佳的概率译码算法.它采用网格图的特殊结构,随着译码的不断深入,不断去除可能性最小的路径,从而逐渐获得最佳的可能路径.NRZ信号中8个状态和4PAM信号中4个状态的网格图分别如图5(a)和(b)所示.由图可知,n时刻j和k两个状态Sj和Sk的欧式距离为

(a) NRZ信号

(b) 4PAM信号

n时刻状态Sj的状态度量为

sm(j,n)=min[sm(k,n-1)+

bm(j,k,n),sm(l,n-1)+bm(j,l,n)]

(4)

式(4)实现了Viterbi译码中的加-比-选操作.随着时间的推移,状态度量不断累积,达到一定深度后便能进行回溯译码操作,发送端最可能发送的序列即为状态度量累计最小的序列.

与基于逐符号检测的DFE均衡相比,PRML均衡可以提供额外的均衡增益,且适用于NRZ和4PAM两种调制信号.

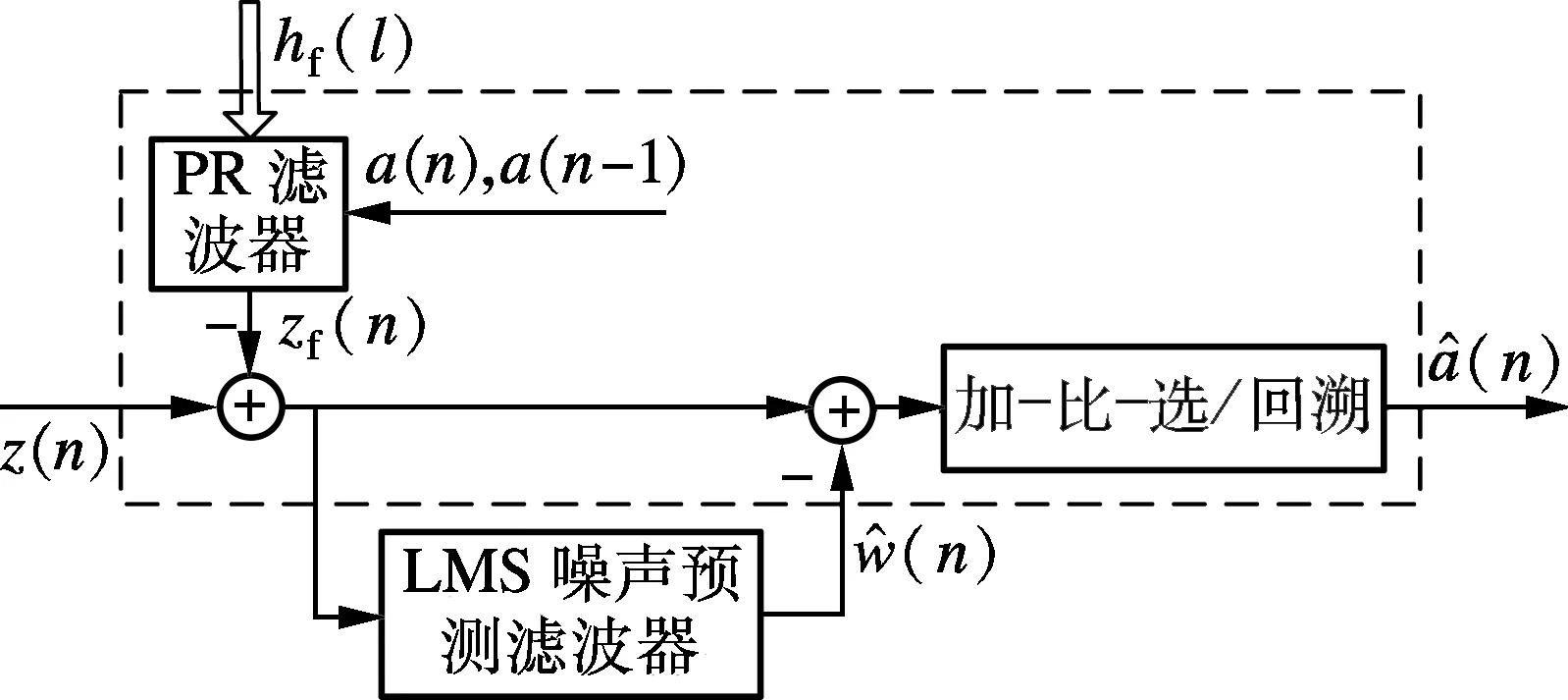

2.2 噪声预测PRML均衡

PRML均衡的性能取决于PR滤波器系数h(l)的准确性.通常令h(l)(l=1,2,…,N)等于针对同一信道优化的DFE抽头系数bm(m=1,2,…,N),因此,理论上只要获取了优化的DFE抽头系数,就能实现PR滤波器.为了适应实际背板系统的时变性,常采用自适应方式获取DFE抽头系数,但会导致硬件复杂度增加.

(5)

式中,zf(n)为n时刻PR滤波器的输出;hf(l)为滤波器系数;w(n)为残留的干扰和噪声成分.为了精确预测w(n),本文采用最小均方(LMS)算法.

图6 噪声预测PRML均衡

(6)

式中,pi(i=1,2,…,K)为噪声预测滤波器的抽头系数,可通过自适应LMS算法离线获得,即n+1时刻的pi(n+1)与n时刻的pi(n)有关,可表示为

pi(n+1)=pi(n)-μe(n)w(n-i)

(7)

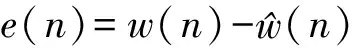

式中,μ为自适应步长,用来调节预测的速度;e(n)为n时刻预测噪声的误差,即

(8)

(9)

由式(9)可推导出如下分支度量表达式:

(10)

式(10)表明,噪声预测PRML均衡的分支度量由PR滤波器的固定系数hf(l)和噪声预测滤波器系数pi共同确定.当部分响应系统为PR2且噪声预测滤波器抽头数为2时,式(10)可表示为bm(j,k,n)=[z(n)-hf(0)a(n)-hf(1)a(n-1)-

p1[z(n-1)-hf(0)a(n-1)-hf(1)a(n-2)]-

p2[z(n-2)-hf(0)a(n-2)-hf(1)a(n-3)]]2

(11)

式中,hf(0)=hf(1).与p1和p2有关的项为预测的噪声,当p1和p2均为0时,式(11)退化为未采用噪声预测的分支度量表达式(3).

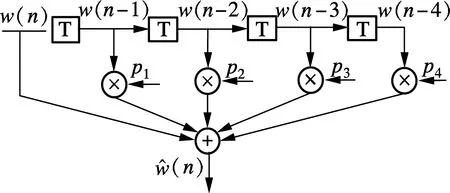

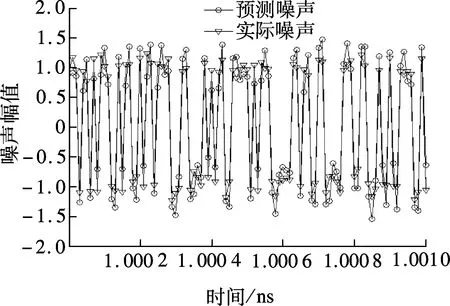

噪声预测滤波器的抽头数越多,预测的噪声越准确.图7给出了抽头数为4时的噪声预测滤波器及其预测结果.由图可知,预测噪声与实际噪声非常接近.当PR滤波器系数为N+1项,噪声预测系数为K项时,NRZ和4PAM两种调制方式下,噪声预测PRML均衡的状态数分别为2N+K和4N+K.由于状态数与系数个数呈指数增长关系,设计时应在复杂度和性能之间折中考虑[9-11].

(a) 4阶噪声预测滤波器

(b) 仿真结果

3 系统仿真

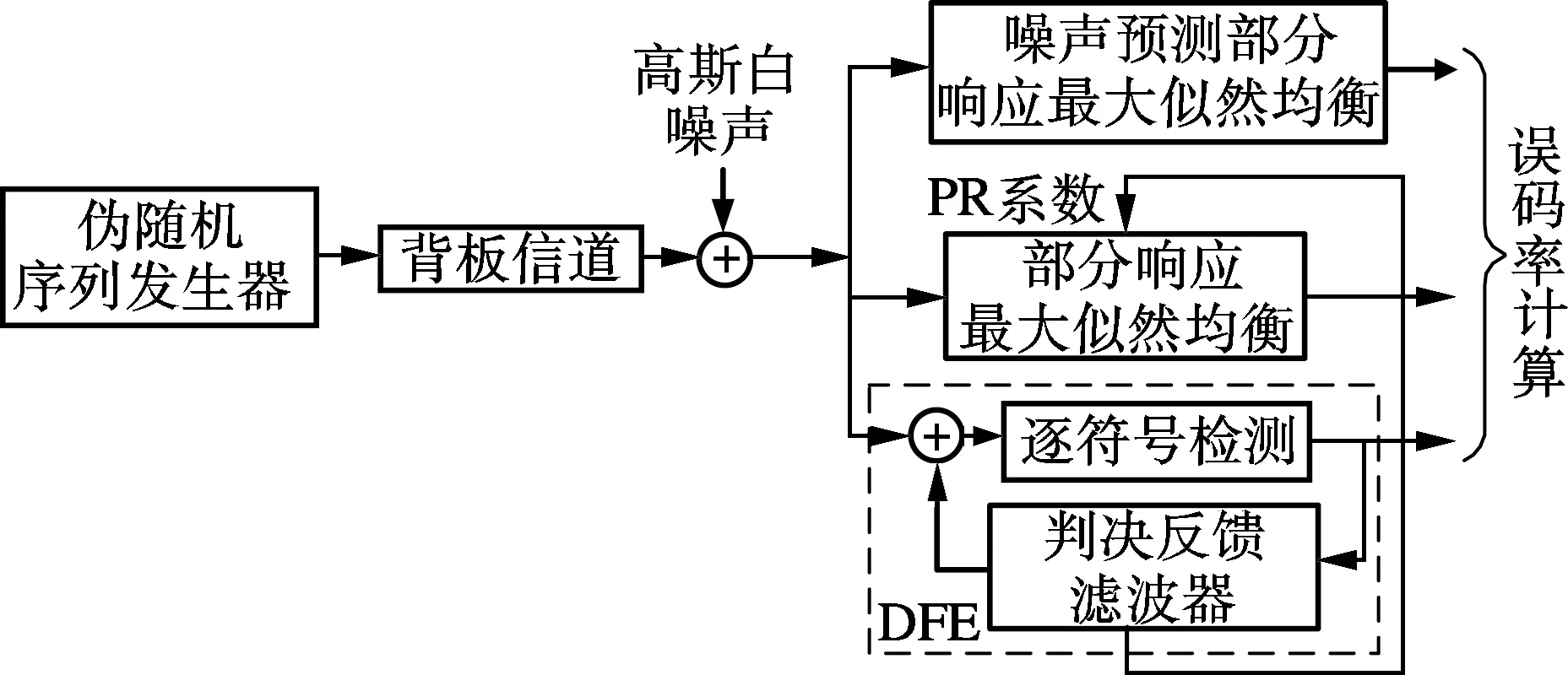

3.1 仿真平台

本文建立的仿真平台如图8所示,包括伪随机序列发生器、背板信道和均衡模块3个部分.对于NRZ信号,采用了DFE,PRML和噪声预测PRML三种均衡方案.对于4PAM信号,采用了DFE和PRML两种均衡方案,其中PRML均衡的PR系数与DFE均衡的抽头系数相同.3种均衡方案的均衡效果通过误码率(BER)性能来衡量.

图8 仿真平台

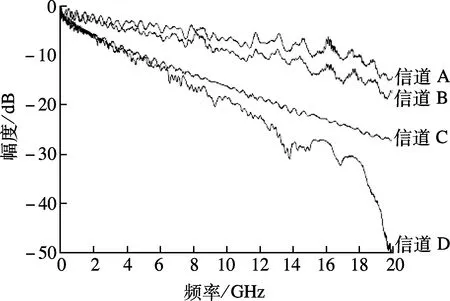

3.2 仿真信道

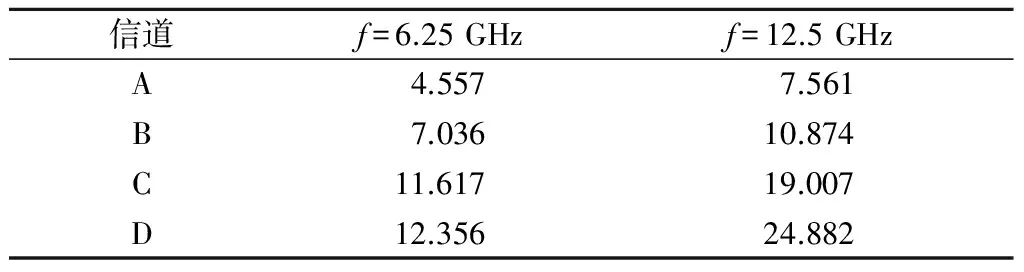

图9为IEEE 802.3ba工作组中4个背板信道的幅频响应曲线[12].频率f=6.25,12.5 GHz时的插入损耗如表1所示.由表可知,当频率增加时,4个信道的插入损耗均显著增加.对于信道D,频率为12.5 GHz时,插入损耗高达24.882 dB.

图9 信道幅频响应曲线

dB

3.3 仿真参数

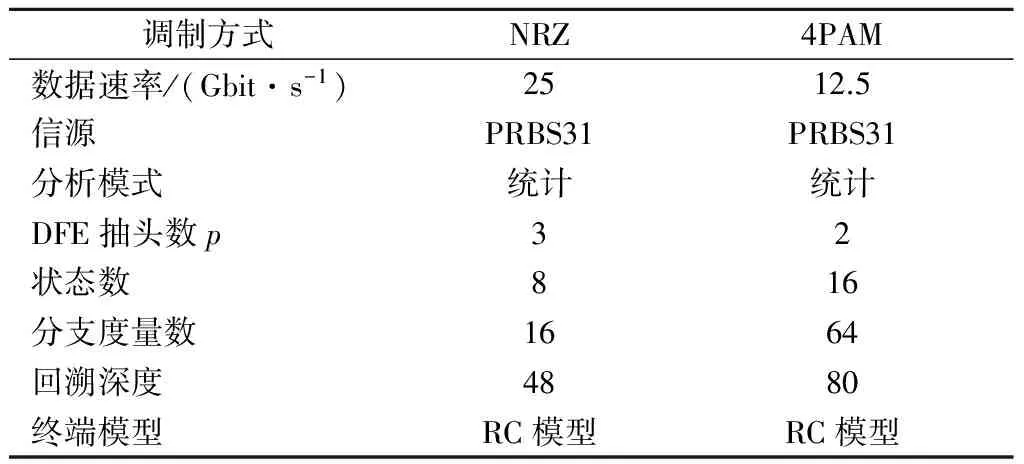

仿真参数设置见表2.由表可知,对于NRZ信号,发送数据为25 Gbit/s的伪随机序列PRBS31,DFE的抽头数为3,PRML和噪声预测PRML的状态数、分支度量数和回溯深度分别为8,16,48.对于4PAM信号,发送数据为12.5 Gbit/s的伪随机序列PRBS31,DFE的抽头数为2,PRML的状态数、分支度量数和回溯深度分别为16,64,80.

表2 仿真参数设置

3.4 仿真结果

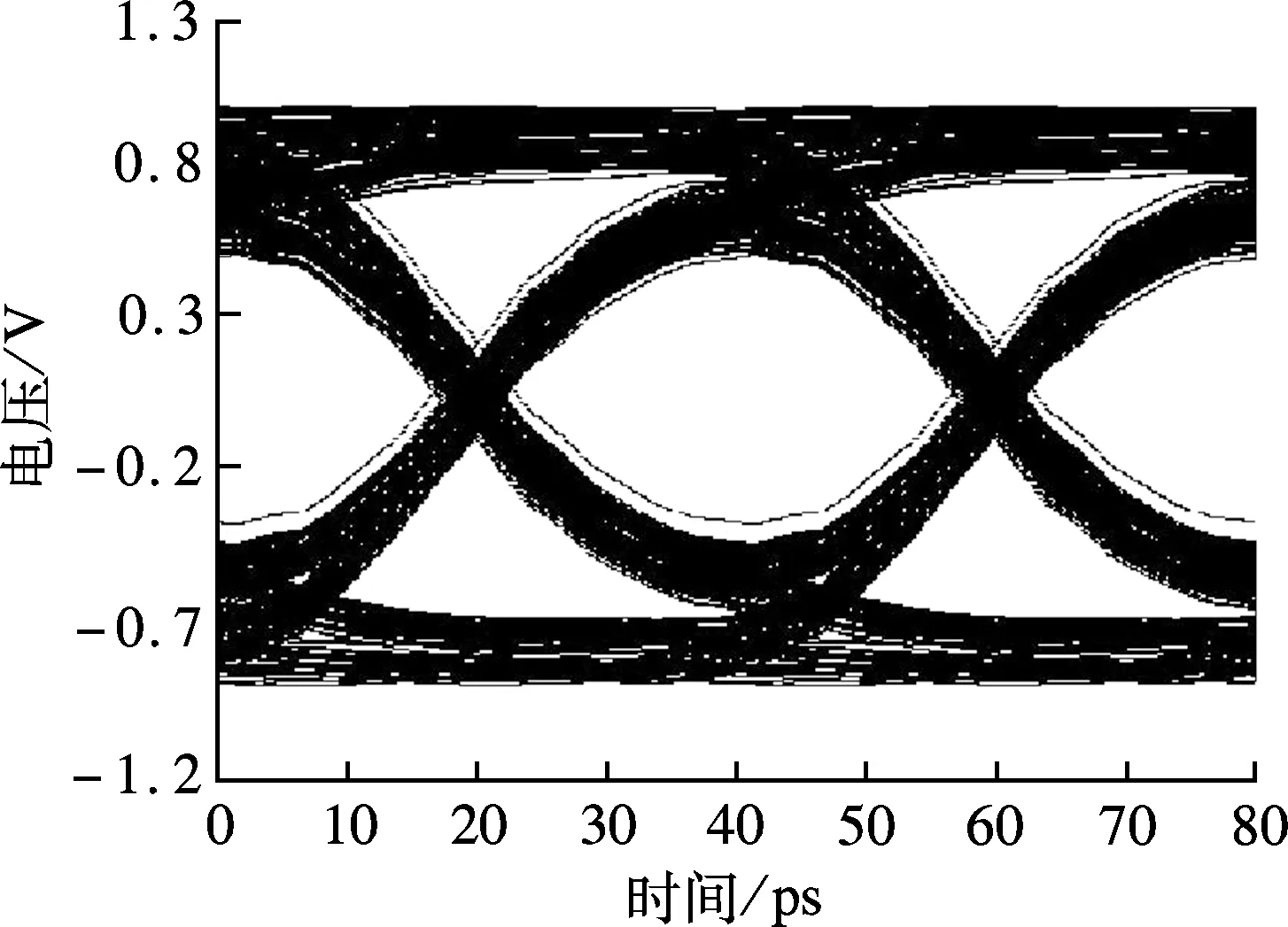

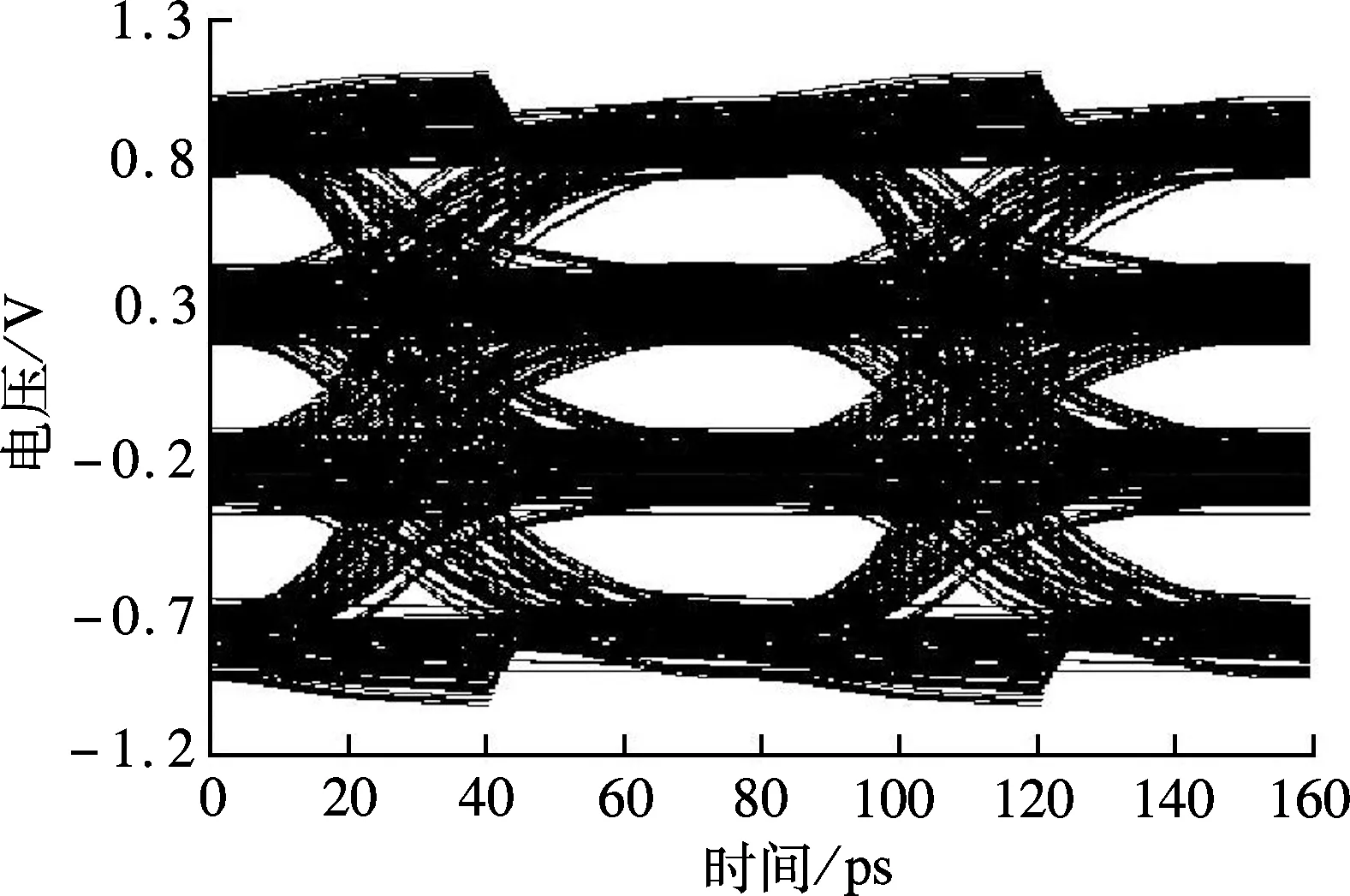

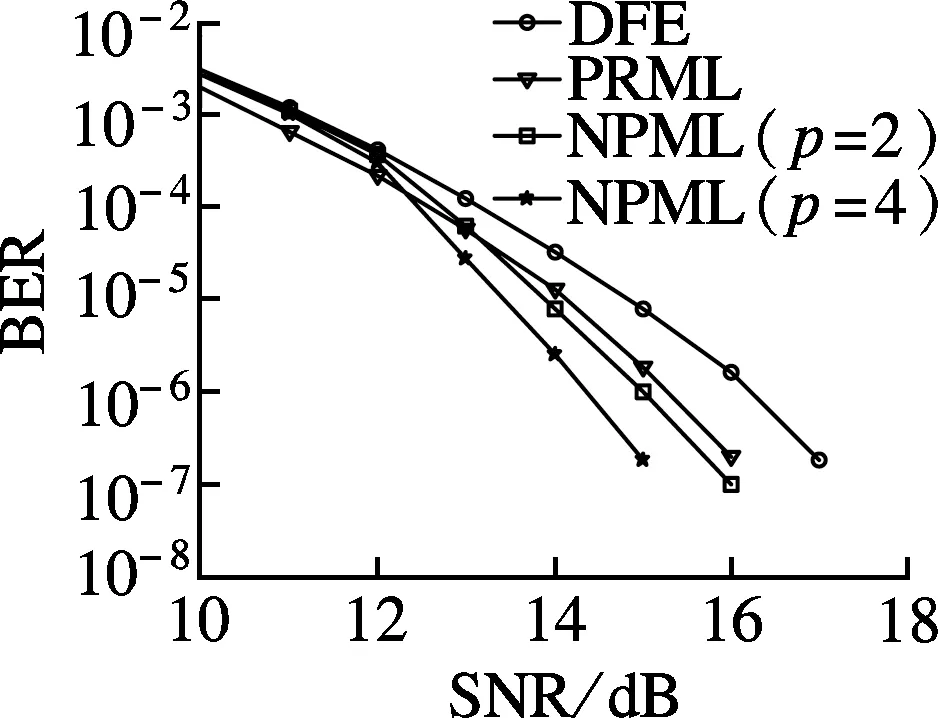

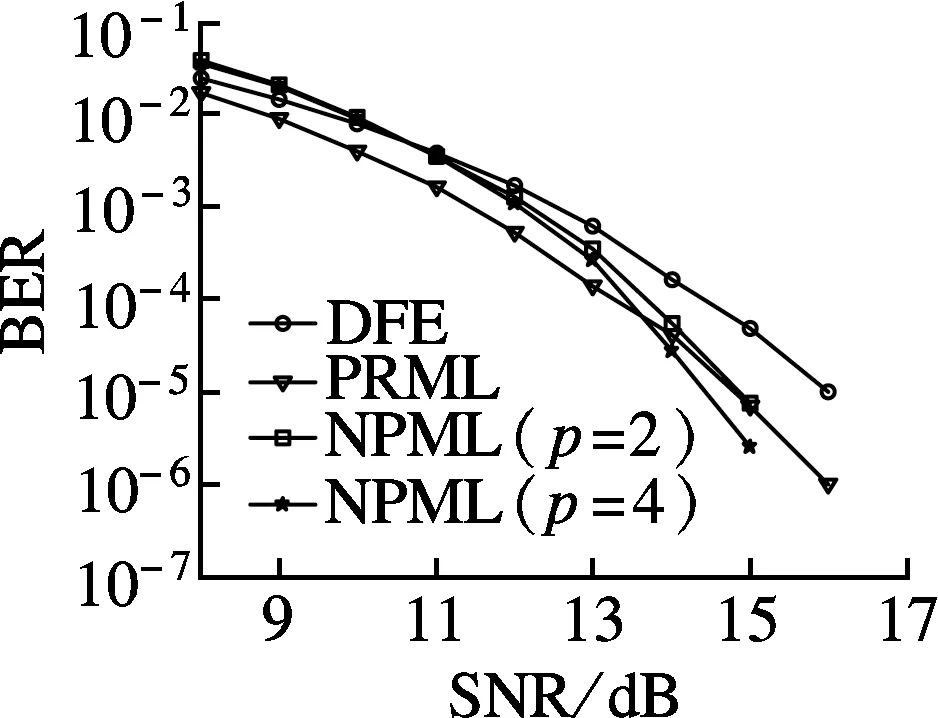

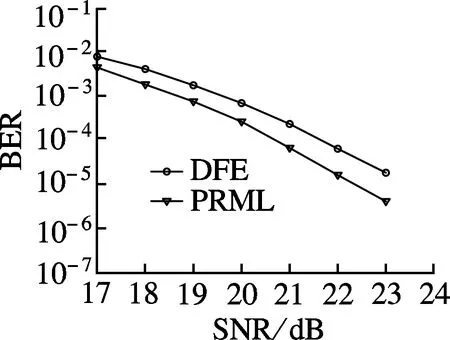

在ADS仿真平台下,NRZ信号和4PAM信号经DFE均衡后的眼图分别如图10(a)和(b)所示.NRZ调制下DFE,PRML和噪声预测PRML(以下简称NPML) 三种均衡方案在4个信道中的误码率曲线见图11.由图可知,3种均衡方案的误码率均随输入信噪比的增加而降低.对于信道A,当BER=10-6时,与DFE相比,NPML的均衡增益为2 dB;对于高损耗的信道D,在BER=10-3处,NPML的均衡增益为2.5 dB.由此表明,在NRZ调制下,与DFE和PRML相比,NPML能够获得较好的均衡增益,因而更适用于高损耗背板信道中.

(a) NRZ信号

(b) 4PAM信号

(a) 信道A

(b) 信道B

(c) 信道C

(d) 信道D

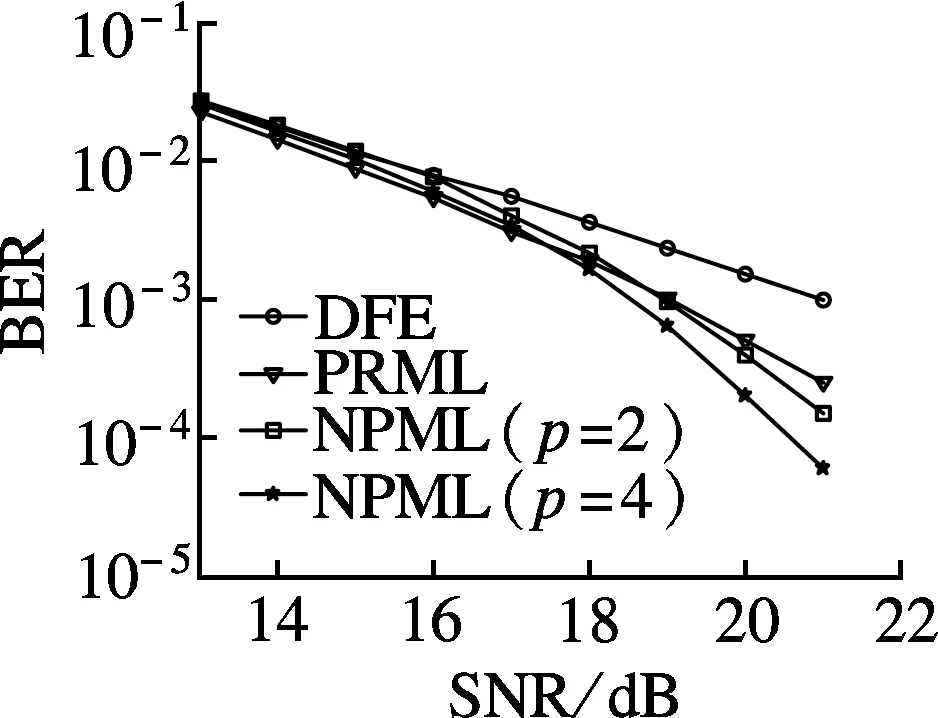

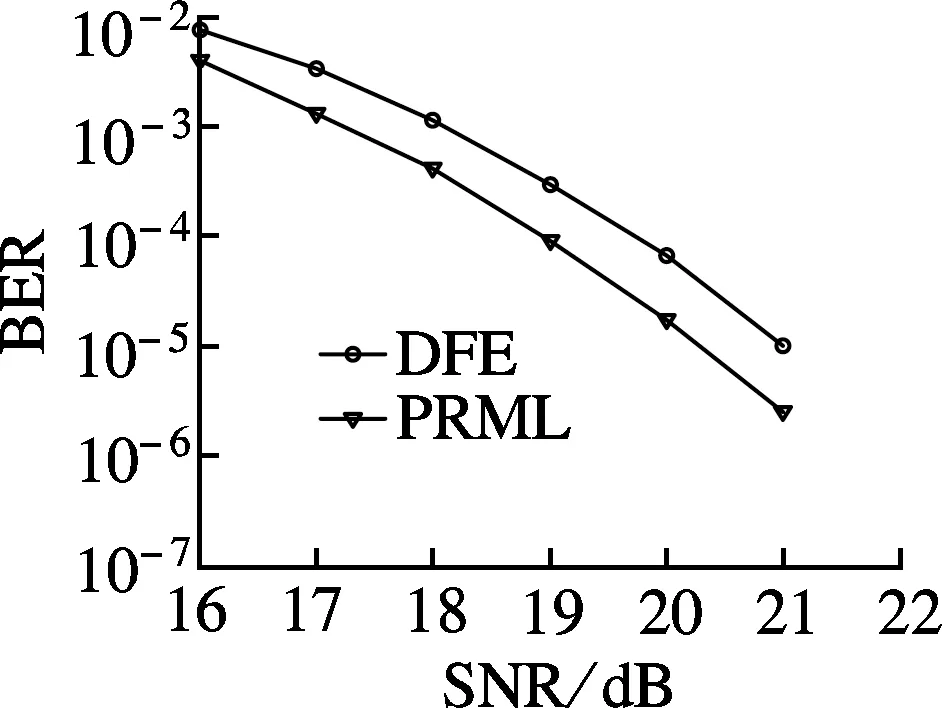

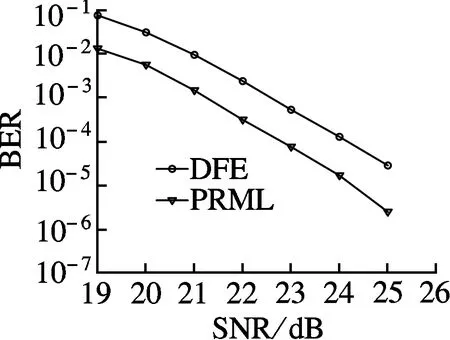

4PAM调制下DFE和PRML两种均衡方案在4个背板信道中的误码率曲线见图12.由图可知,对于信道A,在BER=10-5处,与DFE相比,PRML的均衡增益为0.7 dB;对于高损耗的信道D,在BER=10-4处,PRML的均衡增益为1.4 dB,说明在4PAM调制下,PRML的均衡效果优于DFE.

综上可知,无论是NRZ调制还是4PAM调制,PRML均衡均显示出良好的性能,适合应用于高速背板信道.

(a) 信道A

(b) 信道B

(c) 信道C

(d) 信道D

4 硬件复杂度分析

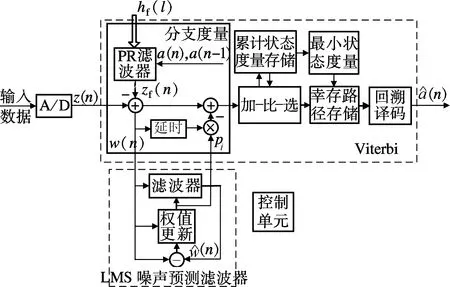

NPML均衡的硬件实现框图见图13,主要包括A/D转换、Viterbi译码模块、LMS噪声预测器及控制单元.A/D转换模块主要量化输入信号.

图13 NPML均衡实现框图

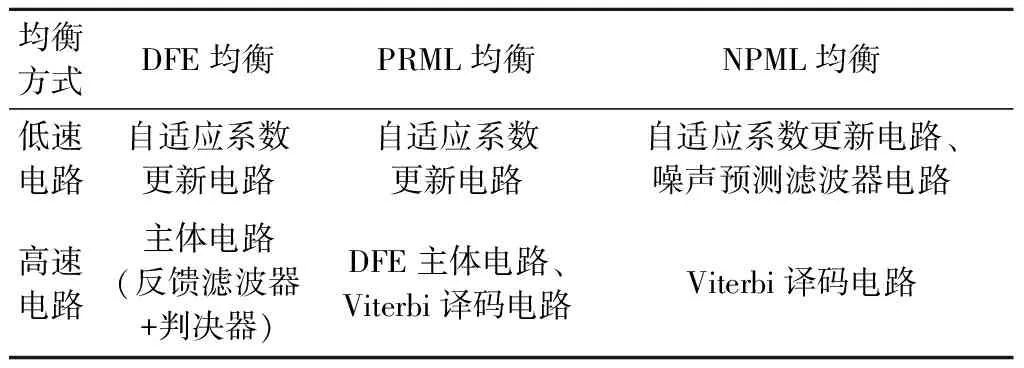

表3给出了DFE,PRML,NPML三种均衡方案的硬件复杂度比较.由图可知,3种方案不需要每个符号都更新抽头系数,因此系数更新电路的工作频率可适当降低,即系数更新电路为低速电路.DFE主体电路和Viterbi译码电路均为高速电路,其工作速率都应与信号速率一致.与DFE相比,PRML和NPML均以复杂的最大似然译码换取一定的均衡增益.对PRML和NPML两个方案进行进一步分析可知,NPML的噪声预测滤波器也可以工作在低速率下,其高速部分仅为Viterbi译码电路,因此无论在误码率性能方面还是在硬件复杂度方面,NPML均衡更优.

表3 NRZ调制下3种均衡方案硬件复杂度比较

5 结语

本文研究了应用于25 Gbit/s串行链路的NPML均衡技术.在NRZ调制下,给出了DFE,PRML和NPML三种均衡方案的统计仿真结果,并对其硬件复杂度进行分析和比较.结果表明,相对于DFE均衡,NPML均衡能够获得更好的均衡增益;与PRML均衡相比,NPML均衡降低了硬件复杂度.因此,NPML均衡更适合应用于高速串行链路系统中.基于4PAM的NPML均衡系统正处在进一步研究中.

References)

[1]Momtaz A, Green M. An 80 MW 40 Gb/s 7-tap T/2-spaced feed-forward equalizer in 65 nm CMOS [J].IEEEJournalofSolid-StateCircuits, 2010, 45(3): 629-639. DOI:10.1109/jssc.2009.2039268.

[2]Ali T, Rao L, Singh U. A 3.8 mW/Gbps quad-channel 8.5-13 Gbps serial link with a 5-tap DFE and a 4-tap transmit FFE in 28 nm CMOS[C]//2015SymposiumonVLSICircuits. Kyoto, Japanese, 2015: 348-349. DOI:10.1109/vlsic.2015.7231318.

[3]Francese A P, Toifl T, Braendli M, et al. 10.6 continuous-time linear equalization with programmable active-peaking transistor arrays in a 14nm FinFET 2mW/Gb/s 16Gb/s 2-Tap speculative DFE receiver[C]//2015IEEEInternationalSolid-StateCircuits. San Francisco, California, USA, 2015: 1-3. DOI:10.1109/isscc.2015.7062988.

[4]Zhang B, Khanoyan K, Hatamkhani H, et al. A 28 Gb/s multistandard serial link transceiver for backplane applications in 28 nm CMOS[J].IEEEJournalofSolid-StateCircuits, 2015, 50(12): 3089-3100. DOI:10.1109/jssc.2015.2475180.

[5]Alaa R, AL T, Yuan F, et al. Minimum jitter adaptive decision feedback equalizer for 4PAM serial links[C]//IEEEInternationalCircuitsandSystems. Lisbon, Germany, 2015: 2868-2871. DOI:10.1109/iscas.2015.7169285.

[6]Bulzaccheli F J. Equalization for electrical links: Current design techniques and future directions [J].IEEEJournalofSolid-StateCircuits, 2015, 7(4): 23-31. DOI:10.1109/mssc.2015.2475996.

[7]Toifl T, Buchmann P, Beukema T, et al. A 3.5pJ/bit 8-tap-feed-forward 8-tap-decision feedback digital equalizer for 16Gb/s I/Os[C]//EuropeanSolidStateCircuitsConference. Venice, Lido, 2014: 455-458. DOI:10.1109/esscirc.2014.6942120.

[8]Parikh S, Kao T, Hidaka Y, et al. A 32Gb/s wireline receiver with a low-frequency equalizer, CTLE and 2-tap DFE in 28nm CMOS [C]//IEEEInternationalSolid-StateCircuitsConferenceDigestofTechnicalPapers. San Francisco, California, USA, 2013: 28-29.

[9]Eleftheriou E, Ocler S, Hutchins R A. Adaptive noise-predictive maximum likelihood (NPML) data detection for magnetic tape storage systems[J].IBMJournalofResearchandDevelopment, 2010, 54(2): 7-1-7-10. DOI:10.1147/jrd.2010.2041034.

[10]Olcer S, Hutchins R A. NPML detection employing IIR noise-predictive with applications to magnetic tape storage[C]//2011IEEEGlobalTelecommunicationsConference. Houston, Texas, USA, 2011: 1-6. DOI:10.1109/glocom.2011.6133811.

[11]Arslan S S, Lee J, Goker T. Error event corrections using list-NPML decoding and error detection codes[J].IEEETransactionsonMagnetics, 2013, 49(7): 3775-3778. DOI:10.1109/tmag.2013.2249658.

[12]Megha S. Strada whisper measured backplane channel [EB/OL]. (2011-05-12)[2015-08-01]. http://www.ieee802. org/3/100GCU/public/channel.html.

[13]Veigel T, Alpert T, Lang F, et al. A Viterbi equalizer chip for 40 Gb/s optical communication links[C]//EuropeanMicrowaveIntegratedCircuitsConference. Nuremberg, Germany, 2013: 49-52.

Noise prediction partial response maximum likelihood equalization for high speed serial link

Zhang Yinhang Hu Qingsheng

(Institute of RF- & OE-ICs, Southeast University, Nanjing 210096, China)

To solve the problem of signal integrity of high speed serial signal transmission in the backplane channels at or above 25 Gbit/s, the partial response maximum likelihood (PRML) equalization scheme,which can achieve a tradeoff between the high speed and the low bit error rate (BER), is studied. The noise prediction PRML equalization, which can effectively reduce the hardware cost, is derived based on the noise prediction method. The BER performance and the hardware complexity are analyzed by the decision feedback equalization (DFE), the PRML equalization and the noise prediction PRML equalization, respectively, in the backplane channels with different attenuation characteristics and on the different modulation modes. The results show that for the 25 Gbit/s non return zero (NRZ) signal, the BER performance of the noise prediction PRML equalization is better than those of the DFE and the PRML equalization. For the 12.5 Gbit/s 4 level pulse amplitude modulation (4PAM) signal, the PRML equalization can obtain better BER performance than the DFE. The hardware complexity of the noise prediction PRML equalization is better than that of the PRML equalization, making it more suitable for high speed serial link.

signal integrity; noise prediction; hardware complexity; serial link

第47卷第1期2017年1月 东南大学学报(自然科学版)JOURNALOFSOUTHEASTUNIVERSITY(NaturalScienceEdition) Vol.47No.1Jan.2017DOI:10.3969/j.issn.1001-0505.2017.01.002

2016-05-27. 作者简介: 张银行(1982—), 男, 博士生; 胡庆生(联系人), 女, 博士, 教授, 博士生导师, qshu@seu.edu.cn.

国家自然科学基金资助项目(61471119).

张银行,胡庆生.应用于高速串行链路的噪声预测部分响应最大似然均衡[J].东南大学学报(自然科学版),2017,47(1):6-11.

10.3969/j.issn.1001-0505.2017.01.002.

TN919

A

1001-0505(2017)01-0006-06