DSP指令Cache的设计与实现

2016-12-26湘潭大学物理与光电工程学院吕华智黄嵩人

湘潭大学物理与光电工程学院 吕华智 黄嵩人

DSP指令Cache的设计与实现

湘潭大学物理与光电工程学院 吕华智 黄嵩人

为提高DSP处理器的执行效率,专门针对CPU指令处理速度与存储器指令存取速度不匹配问题,本文通过在CPU与主存储器之间设计了一款指令Cache,从而有效解决了上述问题。根据DSP四级流水线的特性,所设计的指令Cache采用直接映像机制;通过verilog实现指令Cache的编程,并使用ModelSim仿真软件对指令Cache进行了仿真验证,仿真结果表明指令Cache的效果符合预期。

DSP;指令Cache;Cache控制器

近年来,在国家的大力扶持下,集成电路产业发展异常迅速, CPU的处理速度越来越快,集成度也越来越高,然而相对于微处理器而言,存储器读写速度的提高却相对比较缓慢,两者之间的速度差距越来越大,以至于导致瓶颈问题的产生,从而制约着系统整体性能的提高。在现代计算机体系结构中,通常在CPU和主存储器之间插入一个容量小而速度快的存储器来满足性能要求,这一存储器被称为高速缓存(Cache)。

1 指令Cache的设计与实现

1.1 Cache的工作原理

在Cache的存储系统中,Cache和主存储器之间一般是用块来进行信息交互的。因此,Cache和主存都会被分割成一些大小相同的块,且块的大小通常为2的幂次方字节。

当CPU需要读Cache里面的内容时,CPU会发出一个物理地址,这个物理地址被放到主存地址寄存器中。紧接着地址变换部件会将主存地址中的块号B转换成Cache的块号b,并存储到Cache地址寄存器中。与此同时将主存地址中的块内地址W直接作为Cache的块内地址w装入到Cache地址寄存器中。如果转换成功(称为Hit),就用此Cache地址去寻址Cache_SRAM,并且将访问到的数据传给CPU。反之,则称为Cache Miss,CPU就直接访问主存储器,将主存储器的内容传给CPU,且同时将其复制到Cache_SRAM中。在拷贝的过程中如果发现Cache已经满了,那么就需要采取某种替换策略将一些不常用到的块替换出来,以此来装入新调入的块。由于程序具有局部性的特点,当发现Cache失效时,我们就将失效内容对应的整个块都装入Cache中,从而减少Cache的失误率。

1.2 指令Cache的基本结构设计

Cache容量的大小与映射的方式存在着一定的关系,被称为2:1 Cache的经验规律,即容量为N的直接映射Cache与容量为N/2的二路组相联Cache有着几乎相同的缺失率[2]。其中强制性失效率并不会受Cache容量的影响,然而容量失效率则与Cache的容量成反比关系;同时强制失效和容量失效有一个共同点,就是他们都不受相联度的影响。如果Cache容量过大,就会导致Cache的命中时间过长,进而会影响到CPU的执行效率;冲突失效率是随着Cache相联度的增加而下降。但是并不是说Cache的容量越大越好,当达到一定容量的时候,如果再继续增加Cache的块大小,反而会导致Cache的命中率降低。

在综合考虑了性能、功耗、面积等方面的因素,最终把指令Cache的容量大小设计为8KB,块大小为16个字节,采用直接映射。指令Cache主要由以下几个模块构成:ICache_CTR控制模块、I Cache_SRAM模块、TAG_SRAM模块,其中TAG_SRAM、ICache_ SRAM可以称为数据部分,ICache可以称为控制部分,在数据部分进行查找操作,将查找结果(hit或miss)送到控制部分,由控制部分依据查找结果进行下一步的操作。

由于直接映像是一种最简单,也是最直接的方法,所以在本款32位的DSP内核中,指令Cache采用直接地址映像的方式。其直接映像就是指主存中的一个块在Cache中具有唯一的位置。当CPU访问该主存块时,利用块索引查找对应的目录表项,如果其中保存的标识与主存块Tag相同,且"Valid"位为1,则说明该位置上的Cache块即是所要找的块。假设主存的块号为I。Cache的块号为J,则可按照一种循环分配的原则确定I、J之间的对应关系:

J=I mode M

其中,M为Cache的块数。

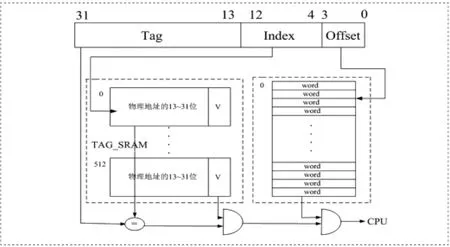

在本系统中,Tag表示存储器的区号,index表示块索引,offset表示块内偏移,通过每块中的offset就可以找到块中的每一个word。

TAG_SRAM总共有512个目录表项,每个表项包含Tag位和Valid位,其中取物理地址的高19位作为Tag位。ICache_SRAM存储的是指令Cache中的内容,ICache_SRAM中的4个表项(每个表项是一个word,其中一个word包含4个Byte)与TAG_SRAM中的一个表项组成ICache目录表中的一个line,比如:TAG_SRAM的第1个表项与ICache_ SRAM中位于4~7的word组成ICache目录表的line1.当要取指时需查找TAG_SRAM,利用要读取指令地址的4~12位的值作为索引查找TAG_ SRAM,得到TAG_SRAM对应的表项,将该表项返回给ICache模块,后者据此判断ICache是否命中。指令Cache的基本结构图如图1所示。

图1 指令Cache的基本结构图

1.3 指令Cache的实现

将指令Cache结构和Cache控制器进行整合后,采用verilog编程来实现指令Cache。ICache控制器的主体是一个状态机,有三个状态:IDLE、IC_FETCH和IC_MISS。处理器复位的时候处于IDLE状态,当需要取指时会进入IC_FETCH状态,在此状态下又分以下三种情况:①当Cache命中时,则直接从Cache取得指令返回给处理器②如果Cache未命中,则从内存中读取指令,且将指令读入Cache中③如果指令所在的内存块被禁止,则同样从相应的内存块中读取指令,并回到IDLE状态。

而ICache的存储体TAG_SRAM和ICache_SRAM直接用Memory Compiler生成。

2 指令Cache的仿真与验证

指令Cache的仿真在ModelSim中进行,例化程序的机器码由CCS运行产生,再将机器码导入存储器中。在系统上电复位的时候,指令Cache未被使能,ICache_SRAM中还没有数据,所以在初始化Cache之前,CPU取指是需要从内存中获取,该指令在流水线执行阶段用了多个时钟周期,仿真结果如图2.当Cache初始化完成之后,并且指令Cache被使能,此时CPU取指则可从Cache中直接获取,此时在流水线执行阶段只占用一个时钟周期。仿真结果如图3所示。