一种带有亚稳态消除电路的TDC设计方案*

2016-12-23艾国润刘俐宏杨赟秀甄少伟贺雅娟

尤 帅,艾国润,刘俐宏,杨赟秀,袁 菲,甄少伟*,贺雅娟,罗 萍

(1.电子科技大学电子薄膜与集成器件国家实验室,成都610054;2.西南技术物理研究所,成都610041)

一种带有亚稳态消除电路的TDC设计方案*

尤 帅1,艾国润1,刘俐宏1,杨赟秀2,袁 菲2,甄少伟1*,贺雅娟1,罗 萍1

(1.电子科技大学电子薄膜与集成器件国家实验室,成都610054;2.西南技术物理研究所,成都610041)

时间间隔测量技术在原子物理、激光测距、定位定时等方面有着重要的应用,因此,高精度的时间数字转换电路TDC(Time-to-Digital Converter)在科学研究和工程实践中扮演着重要的角色;本次提出的TDC设计方案功耗为400μW,工作在512 MHz,实现了250 ps的测量精度和1μs的测量范围,但是TDC在进行时间间隔测量量化时往往受到亚稳态制约。通过加入相位判断逻辑,TDC的积分非线性降低到0.25 LSB,而差分非线性降低到了0.5 LSB,可以完全消除TDC量化时间间隔时遇到的亚稳态问题。

科学研究和工程实践;亚稳态消除;相位判断逻辑;时间间隔测量;时间数字转换电路

时间间隔测量技术在原子物理、激光测距、定位定时等领域有着广泛的应用。此外,在工业控制以及视觉识别等领域中,时间间隔测量作为一种重要的鉴别和探测手段,对精度的要求非常严格,甚至达到了皮秒量级。因此,高精度的TDC电路有着重要的作用。

2008年,Minjae Lee[2],Asad A Abidi在90 nm COMS工艺下,采用基于时间放大器的双步测量法设计的TDC具有9 bit输出和1.25 ps的精度;2010年,Nan Xing,Jong-Kwan Woo,Woo-Yeol Shin,Hyunjoong Lee,Suhwan Kim在0.18μm CMOS工艺下,采用循环游标延迟线法的TDC具有14.6 ps的精度和50 ns的动态范围[3]。

而我国TDC的研究主要是基于FPGA来实现的。2006年,中国科技大学快电子学实验室使用基于FPGA进位链法[4]实现了50 ps精度的TDC电路[5],2011年,该实验室在Virtex-4 FPGA上实现了9通道、时间精度达到9 ps的TDC[6]。2012年,哈尔滨工业大学喻明艳[7]等人采用具有一阶噪声整形的过采样技术,设计的基于多路可控环形振荡器的TDC,有效分辨率能达到5 ps,且其温度稳定性较好。

TDC在全数字锁相环ADPLL(All-Digital Phase-Locked Loop)中也有着重要的应用,文献[8]设计的基于TDC的ADPLL实现了250 MHz的输出频率,锁定时间为2μs,峰峰抖动为76 ps。本文的全数字时间数字转换器TDC(Time-to-Digital Converter)设计方案采用延迟线和计数器两级结构对时间间隔进行量化。其中延迟线的设计引入了非线性性优化技术[1],使得TDC的积分非线性得到显著的改善。TDC的分辨率主要决定于延迟线,而量程则主要由计数器的计数范围来决定。本设计采用18μm工艺,实现了250 ps的精度,1μs的量程且具有良好的线性度。

1 TDC的时间间隔原理

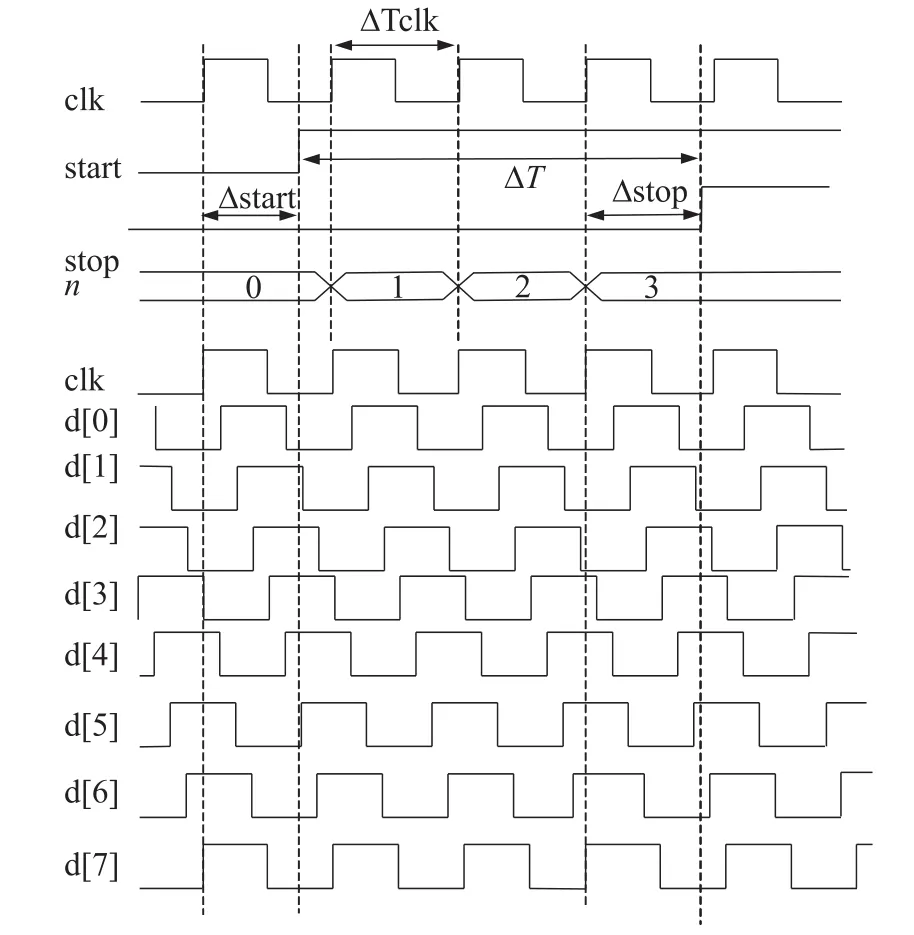

本文的TDC设计采用延迟线和计数器两级结构,图1为时间数字转换原理时序图。

图1 时间数字转换原理时序图

时间到数字的转换最基本的思想是在一段时间内用一个时钟对其进行数,图1是这种思想的原理图,由图1可得:

式中,ΔT为要转换的时间,Tclk为时钟周期,ΔTstart和ΔTstop为开始和结束的时间测量误差,n为ΔT内计数器的计数值。则时间到数字的转换误差为

可得

两级结构中的延迟线量化ΔTstart和ΔTstop,如图1中的d[0]~d[7]为延迟线的输出,通过start和stop采样d[0]~d[7]即可量化ΔTstart、ΔTstop;计数器量化nTclk。

2 TDC的电路结构

图2所示为TDC的电路结构。

图2 TDC的电路结构

采样编码模块实现ΔTstart和ΔTstop两部分的计时;减法模块实现ε=ΔTstop-ΔTstart;使能模块提供计数器的使能信号;计数器实现nTclk的计时;处理单元模块把nTclk和ε=ΔTstop-ΔTstart两部分计时时间合并成单总线信号。

3 TDC的时序分析

3.1 计数器部分的时序

图3所示为计数器部分的时序。

图3 计数器部分的时序

(1)clk是系统时钟512 MHz;

(2)start(随机信号)是计数开始信号;

(3)stop(随机信号)是计数停止信号;

(4)start_clk是start经过边沿同步后产生的信号;

(5)stop_clk是stop经过边沿同步后产生的信号;

(6)start_stop是start_clk和stop_clk经过使能模块后产生的信号,作为计数器的使能信号;

(7)clk_dealy是clk经过延迟的信号

(8)gated_clk_delay是start_stop和clk_dealy经过两输入与门后的信号,作为计数器的计数信号。

3.2 采样的时序

3.2.1 start信号采样时序

如图4所示,start特殊采样位置可能出现亚稳态的问题。理想情况下,各个相位相对前一级都是250 ps的延迟,实际上由于占空比畸变、延迟偏差、信号抖动等原因会稍有偏差。

start的采样时间决定着ΔTstart的大小,ΔTstart的计算方式如图1所示,只与d[7:0]的上升沿有关,所以只考虑在start来到时,d[7:0]信号上升沿的位置。①②为一对采样位置,③④为另一对采样位置。

由于D触发器存在建立和保持时间,在①②位置时,start对d[7:0]采样,由于d[7]处于翻转的状态,有可能出现亚稳态,导致采样结果错误。从而ΔTstart有可能从2 ns到0 ns的跳变;或者相反,有可能从0 ns到2 ns的跳变,致使TDC的计数出现很大的偏差。

start在③④位置对d[7:0]采样时,由于d[2]处于翻转的状态,虽然也可能产生亚稳态,但是会在d[1]和d[3]处采样到正确的值,所以ΔTstart只有250 ps的误差。

图4 start特殊采样位置可能出现亚稳态的问题

3.2.2 stop信号采样时序

stop和start同为随机信号,只是到来的时刻不同,所以stop的采样时序与start相同。

3.3 亚稳态的消除

start对d[7:0]采样,当采样位置是①②时,会出现巨大偏差;本论文提出的亚稳态消除电路,就是消除当采样位置是①②时出现的偏差;如图5所示,相位判断逻辑;图6为采样位置①的时序,图7为采样位置②的时序。由于不满足D触发器建立时间,start_clk信号同步错误,即为start_clk_wrong。s_out_wrong为start_clk_wrong采样start_nclk得到的信号。

图5 相位判断逻辑

图6 采样位置①的时序

图7 采样位置②的时序

(1)在采样位置①或②时,不会出现d[x:x-1]= 01(x=6~1)的情况,由此区分start(或stop)是否出现在采样位置①或②;

(2)①当s_out=0时,ΔTstart赋值为2 ns;②当s_out=1时,ΔTstart赋值为0 ns;

(3)结合图4和ΔT=nTclk-ΔTstart+ΔTstop,可以发现ΔTstart产生的误差由nTclk处调整后被消除;同理:ΔTstop产生的误差也可被消除,从而消除了由于亚稳态的出现导致的计时误差。

4 TDC的线性度

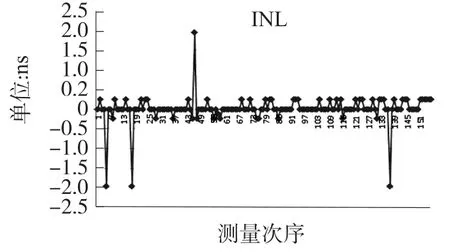

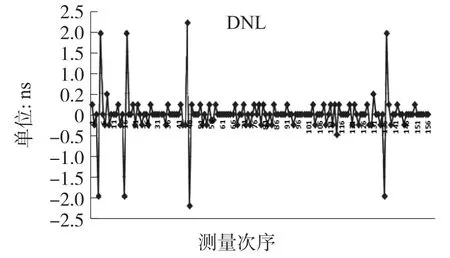

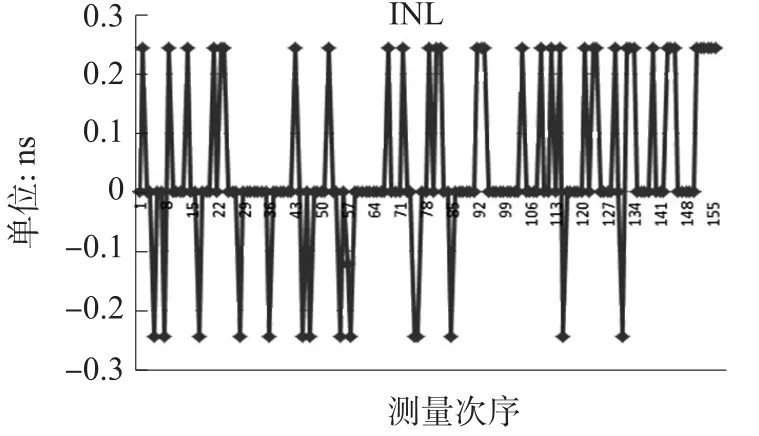

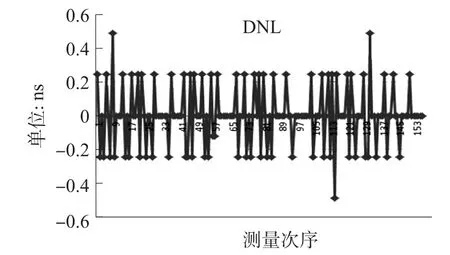

未加相位判断逻辑和加入相位判断逻辑后TDC的积分非线性(INL)和差分非线性(DNL)如图8~图11所示;测试激励start和stop之间的时间间隔以50 ps为步长步进,步进次数为156次。

从图8、图9可以看出,没有加入相位判断逻辑时,在个别位置上TDC的测量码有较大的积分非线性和差分非线性。INL最大可达2 LSB,DNL最大可达2.3 LSB。

图8 积分非线性(未加入相位判断逻辑)

图9 差分非线性(未加入相位判断逻辑)

但是,加入了相位判断逻辑后,从图10、图11中可以看出TDC的积分非线性和差分非线性都得到很大的改善。INL降低到0.25 LSB,而DNL降低到了0.5 LSB。说明TDC有着良好的线性度且分辨率达到设计要求。

由此说明,加入了相位判断逻辑后,亚稳态引起TDC跳码的问题得到了完全的解决。

图10 积分非线性(加入了相位判断逻辑)

图11 差分非线性(加入了相位判断逻辑)

5 结论

本论文在基于延迟线的基础之上提出了全新的TDC计时算法,解决了由于采样时出现的亚稳态而导致TDC计时出现很大偏差的问题。在0.18μm工艺下,采用全数字流程,完成了整个TDC电路的设计;本文设计TDC,工作在512 MHz的时钟频率下;从仿真结果来看,TDC具有很好的线性度,没有出现跳码现象,与预期符合的很好。

[1]甘武兵,夏婷婷,甄少伟,等.一种新颖的低非线性全数字多相时钟产生电路[J].微电子学,2014,44(4):467-471.

[2]Minjae Lee,Asad A.bidi.A 9b,1.25 ps Resolution Coarse-Fine Time-to-Digital Converter in 90 nm CMOS that Amplifies a Time Testidue[J].IEEE Journal of Solid-State Circuits,2008,43(4):769-777.

[3]Ping Lu,Pietro Andreani.A High-Resolution Vernier Gated-Ring-Oscillator TDC in 90 nm CMOS[C]//Tampere:IEEE NORCHIP,2010:1-4.

[4]Nan Xing,Jong-Kwan Woo,Woo-Yeol Shin,et al.A 14.6 ps Reso⁃lution 50 ns Input-Range Cyclic Time-to-Digital converter Using Fractional Difference Conversion Method[J].IEEE Transactions on Circuits and SystemsⅠ,2010,57(12):3064-3072.

[5]张家玮.基于FPGA软核处理器NIOSII的高精度时间间隔测量仪[D].天津:天津工业大学,2008:2-3.

[6]Wang J,Liu S,Zhao L,et al.The 10 ps Multitime Measurements Averaging TDC Implemented in an FPGA[J].IEEE Transactions on Nuclear Science,2011,58(4):2011-2018.

[7]Yu Mingyan,Zong Shixin,Tang Xiaochen.A Temperature Stabi⁃lized Multi-Path Gated Ring Oscillator Based TDC[C]//Xi’an Shanxi:Computer Science and Information Processing(CSIP),2012:24-26.

[8]徐洪闪,甘武兵,甄少伟,等.一种基于线性增强TDC的AD⁃PLL的设计[J].微电子学,2015,45(4):507-511.

尤 帅(1989-),硕士,现就读于电子科大学微电子与固体电子学院,主要从事高精度TDC设计研究工作;

甄少伟(1982-),男,汉,河北人,博士,现任电子科技大学微电子与固体电子学院副教授,主要从事信息功率半导体器件与集成电路和系统的研究工作,swzhen@uestc.edu.cn。

A Design Scheme of TDC with Metastability-Elimination Circuits*

YOU Shuai1,AI Guorun1,LIU Lihong1,YANG Yunxiu2,YUAN Fei2,ZHEN Shaowei1*,HE Yajuan1,LUO Ping1

(1.State Key Lab of Electronic Thin Films and Integrated Device,Univ of Electronic Science&Technology of China,Chengdu 610054,China;2.Southwest Technical Physics Institution,Chengdu 610041,China)

The technology of time interval measurement is of a great importance role in the atomicphysics,laserrang⁃ing,positioning and timing,and so on.As a result,the high precision Time-to-Digital Converter plays an important role in the scientific research and engineering practice.The power of TDC is 400μW,it works on 512 MHz,and it’s measurement resolution is 250 ps,accuracy of measurement is 1μs;However,time interval measurement of TDC is often subject to metastability.Integral nonlinearity of TDC reduce to 0.25 LSB,and Differential nonlinearity reduce to 0.5 LSB by adding a phase judgment logic circuit.We can completely eliminate the metastability when TDC time in⁃terval.

scientific research and engineering practice;metastability elimination;phase judgment logic circuit;time interval measurement;Time-to-Digital Converter[TDC]

TN432

A

1005-9490(2016)06-1527-04

8360

10.3969/j.issn.1005-9490.2016.06.047

项目来源:中央高校基本科研业务费项目(ZYGX2014J024);国家自然科学基金项目(61404025)

2015-12-07 修改日期:2016-01-04