FPGA设计中跨时钟域的问题与方法

2018-01-17王利祥

摘 要

随着科学技术的发展,在FPGA设计中多时钟设计是一个经常遇到而且因为功能的需要无法避免问题。在不同时钟域之间传输数据或者控制信号,如果对其中出现的特殊情况估计不足,将会对设计造成灾难性的后果。因此,设计人员在设计电路时必须加入相应的同步机制,确保信号在跨时钟域传输时能够可靠进行。本文从触发器时序理论基础为出发点,分析研究数字化电路设计中跨时钟域传输信号时亚稳态现象产生的原因以及危害,然后分析和研究了解决跨时钟域传输过程中遇到的各种同步技术,分析和比较在不同场合的应用以及各自的优缺点。

【关键词】FPGA 跨时钟域 亚稳态

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程期间的基础上进一步发展起来的一种可编程门阵列。它是作為专用集成电路(ASIC)领用中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程期间门电路数目有限的缺点。

随着计算机硬件以及电子技术飞速发展,FPGA设计中需要用到的逻辑门数目急速增长,其中难免会遇到亚稳态以及电路中存在毛刺的现象,本文在通过深入分析研究,现将在FPGA设计中经常会遇到和用到的方法进行讲述。

1 应用领域

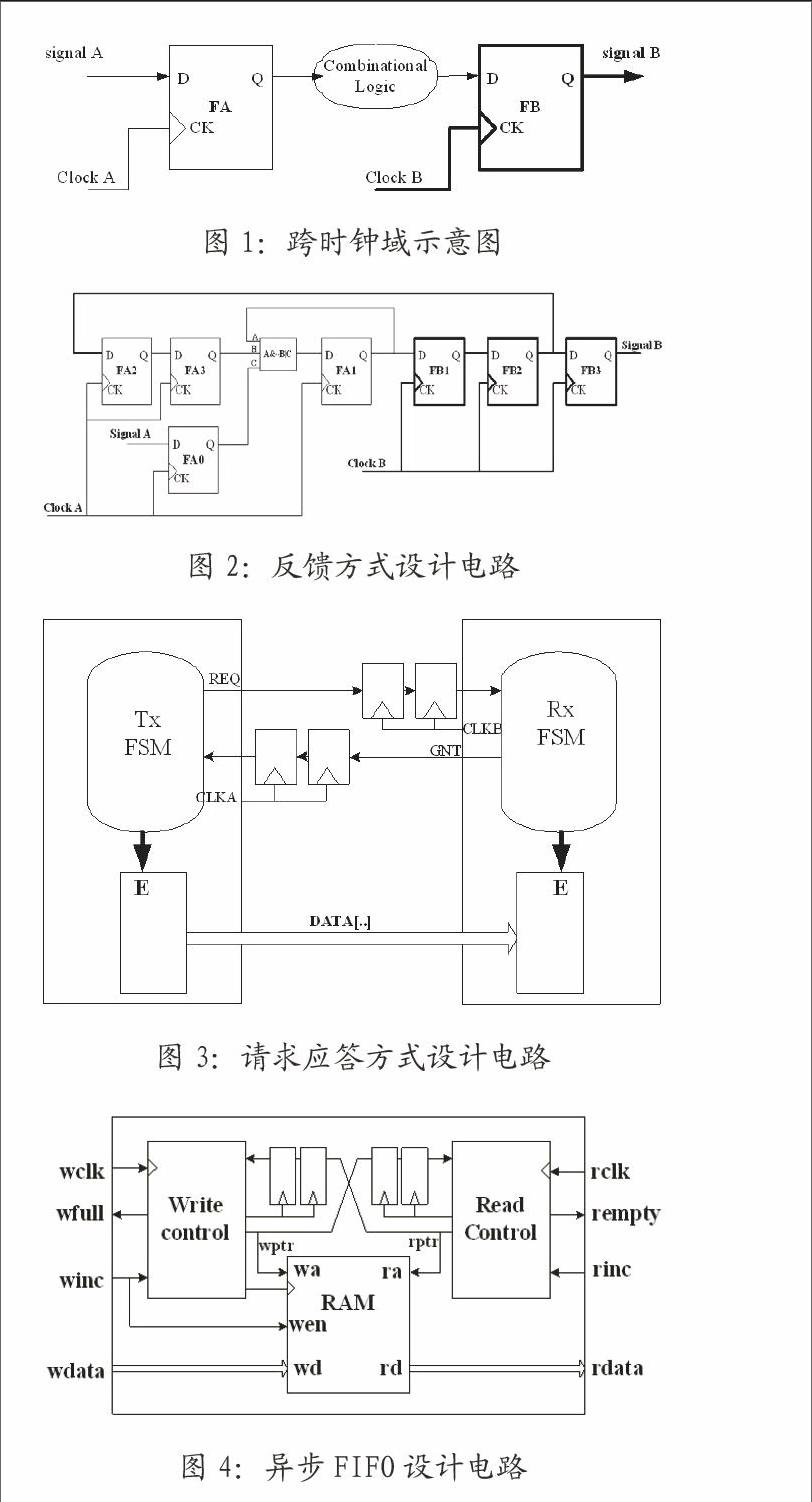

在多时钟设计中,跨时钟域问题总是当数据在时钟的驱动下由一个触发器传送到另一个触发器的时候产生,如图1所示。

2 问题的定义

亚稳态、毛刺、多扇出和重新收敛在异步设计中很有可能出现,他们有可能使整个设计进入不稳定状态,甚至最终会引起功能性错误。

亚稳态现象:数字信号通过异步时钟域时,如果时钟信号不能满足触发器的建立时间或保持时间,此时很可能产生亚稳态现象。

毛刺现象:同步逻辑电路中产生毛刺现象主要取决于数字信号传播时延,这些毛刺有可能会被成功锁存,也有可能导致错误脉冲在同步装置中输出。

多扇出现象:在同步逻辑电路中,由于不同的传播延时,会产生不同值得同步逻辑输出。

信号重汇聚:重汇聚信号当经过同步之后可能导致功能性错误。

3 解决方式

这部分主要介绍几种正确处理跨时钟域逻辑电路设计方式,这些设计方式可以保持数据在跨时钟域传输时的稳定性。

3.1 多同步设计

对于有1bit跨时钟域信号,通常的做法是使用两个触发器去然后再通往目的时钟域。但是其前提条件是信号从源时钟域通往目的时钟域时必须有足够的保持时间以供目的时钟域采样,即时钟A的频率应该低于时钟B的频率。

当我们使用两个触发器进行同步设计时设计者需要保证设计的CDC路径中没有组合逻辑,但是反相器和缓存器除外。否则毛刺现象和多扇出现象便会出现。

3.2 多结构同步设计

对于多位信号在不同的时钟域之间传输,多路复用设计可以保持跨时钟域传输时的正确性,如下图所示。多路复用设计可以适用于如下的设计中,一组数据需要从一个时钟域传输到另外一个时钟域;当断言时,有标记的表明数据信号稳定的一组信号。

3.3 握手设计

握手设计是基于以下协议进行设计的:源时钟域向目的时钟域发出请求,而且该请求信号一直保持着,直到源时钟域接受到目的时钟域的返回信号;目的时钟域接收到请求信号之后,连续不断地发送确认信号,直到其接收到源时钟域是重复断言的。握手机制可以设计为简单的反馈同步器,也可以设计为全握手机制或者半握手机制。

3.3.1 反馈同步设计

对于图2所示,使用的是反馈同步设计实现的逻辑电路。对于该电路来讲,时钟A和时钟B之间的频率差值是没有极限要求的,时钟A的频率可以比时钟B的频率低,也可以比时钟B的频率高。然而该电路使用的是信号A由一个时钟周期组成,而且从当前脉冲到下一个脉冲的时间间隔要大于两倍的时钟A和两倍的时钟B的时间之和。

3.3.2 请求-应答设计

请求和回答传输方式在发送信号Tx和接收信号Rx之间需要双重同步,而且数据的保持时间必须保持到发送信号Tx收到确认无效之后,如图3所示。

3.4 异步FIFO同步设计

当有突发量数据在两个时钟域之间传输时,FIFO同步器是最常用的一种解决方案。如下图,是使用FIFO实现的同步器示意图。它包含双端口RAM,读写控制模块以及两个同步触发器。在使用FIFO实现同步时最关键的问题在于FIFO状态信号的形成,包括满信号、半满信号、空信号以及半空信号。通常情况下,读写指针使用格雷编码,他们可以使用两个同步触发器来保证同步的正确性,如图4所示。

2n队列FIFO是异步FIFO典型例子,它的深度是2n,是一个比较小的FIFO,根据设计的需要,n可以赋予任何的正整数值。理论上来讲,2n队列FIFO可以稳定的传输信号,即使源时钟频率是目的时钟频率的n倍。

参考文献

[1]王利祥,肖铁军.边标志算法的改进与硬件实现[J].计算机工程与设计,2014(08):2817-2821.

[2]孙晓东.FPGA毛刺产生的原因及其抑制放法[J].电脑编程技巧与维护,2010(05).

作者单位

河南护理职业学院 河南省安阳市 455000endprint