一种基于OFDM的新型低功耗RF收发器设计*

2016-12-23帅立国

徐 进,帅立国

(1.苏州经贸职业技术学院SOC研发中心,江苏苏州215009;2.东南大学机械工程学院,南京210096)

一种基于OFDM的新型低功耗RF收发器设计*

徐 进1,2,帅立国2*

(1.苏州经贸职业技术学院SOC研发中心,江苏苏州215009;2.东南大学机械工程学院,南京210096)

为实现低功耗信号传输,提出一种基于正交频分复用(OFDM)的IEEE 802.15.4g低功耗无线电频率(RF)收发器。该新型RF收发器电路由发射机(Tx)基带模拟(BBA)、片上RF开关前端、接收机(Rx)BBA及锁相环(PLL)构成,采用0.18μm CMOS技术制作,满足了IEEE 802.15.4g OFDM系统低功耗信号传输的需要。实际测试结果显示,相比传统的RF收发器,在保持灵敏度和误包率均不降低的条件下,提出的RF收发器具有更低的功耗,当电源电压为1.8 V时,Tx模式下功耗为26.46 mW,Rx模式下功耗为28.26 mW。

IEEE 802.15.4g;RF收发器;OFDM;低功耗

目前,基于无线电频率(RF)的网络系统在计量系统领域拥有巨大的市场潜力[1-2],可以提高服务效率并降低成本。IEEE 802.15.4g网络是解决基于RF网状网络问题的办法之一,但其本身存在许多缺陷,包括通信范围有限、数据速率低、可靠性低及阴影区问题[3]。

为解决以上问题,庞娜[4]等人提出一种AODV混合Zigbee网络,通过在路由层进行设计来提高传输速率和较低功耗。文献[5]使用相位斜率码集合恢复信号,来实现IEEE 802.15.4g接收器,解调方法简单,能耗较低。但是以上研究均是从算法实现角度来解决能耗问题,很少涉及硬件方面。文献[6]提出了基于OFDM IEEE 802.15.4g系统,该系统能够在几百米的范围内,以800 kbit/s的数据速率进行通讯,并保证可靠性,十分适合应用于远程水电数据采集。该系统同样能够用于PC外围设备、个人医疗保健、万能遥控器及家居控制[7-8],具有较高的推广价值。

此类基于OFDM IEEE 802.15.4g的系统需要2种条件:采用移频键控(FSK)且带有极低DC电源的低数据速率和使用正交频分多址(OFDM)的高数据速率[9],即在满足高速数据传输的条件下,要求实现较低的传输能耗。为了降低数据传输功耗,提出了一种OFDM的IEEE 802.15.4g的低功耗RF收发器,可以应用于IEEE 802.15.4g OFDM系统,该收发器是使用0.18μm CMOS技术实现的。整体电路包括片上RF开关前端、Tx BBA(基带模拟)、Rx BBA及PLL。在保持灵敏度和误包率均不降低的条件下,提出的RF收发器具有更低的功耗。

1 提出的RF收发器设计原理

为了减少载波泄露,应采用低通滤波器(LPF)和可变增益放大器(VGA)等Tx基带电路。考虑到基于OFDM的发送器上的峰均功率比要求为10 dB,从1 dB输出压缩点开始,所有RF及模拟电路应在补偿为+10 dB的情况下运行。

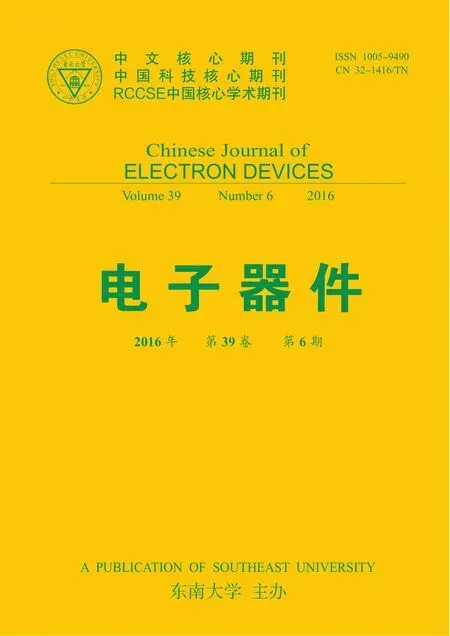

图1是本文提出的基于OFDM的低功耗RF收发器的电路原理图。当接收器最大能容纳-20 dBm的输入时,低噪声放大器(LNA)应首先在低增益模式下运行,以便使接收器输出处于不饱和状态。本文提出的RF收发器采用了零中频结构来实现高集成。该收发器包括带有片上T/Rx开关的RF前端、同相正交(IQ)变频混频器、Tx及Rx链的IQ基带模拟模块(VGA及LPF)以及PLL模块。考虑到表1和表2列举了目标设计规格,对收发器中的所有电路模块进行了设计。

图1 提出的CMOS RF收发器电路原理图

2 RF前端设计

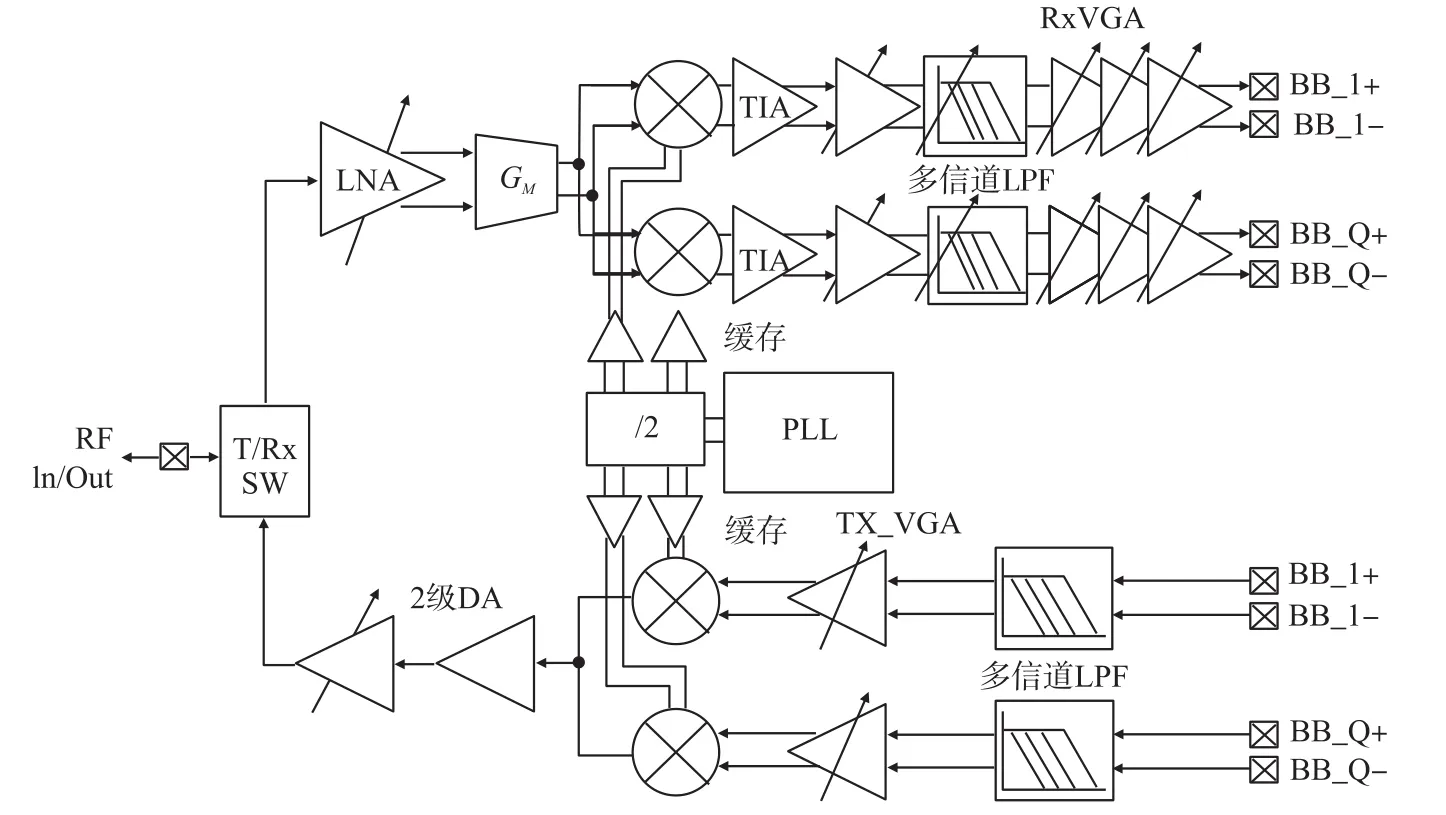

图2是本文提出的RF前端的设计电路图,包括数模(DA)及LNA,该设计允许DA及LNA在不会降低各自性能或可靠性的前提下共享通向天线及外部匹配网络(M/N)的共光路。

图2 提出的RF前端的电路图

图2中,由于T/Rx开关仅位于LNA的输入端,能够在没有损失的情况下将DA的输出功率传递到天线,并产生极少的DC功率损耗。在传输模式下,开关SW0关闭,开关SW1开启,尽管LNA无法工作,外部的M/N用于DA的输出功率匹配电路。在接收模式下,DA无法工作,开关SW0开启,开关SW1关闭。该模式下,直接将LNA的输入耦合到M/N,目前M/N用于LNA的输入匹配电路。在工作频率为920 MHz的情况下,由SW0造成的损失低于1.1 dB,并且不会严重影响接收器的灵敏度。尽管图2中的LNA存在单端输入以便与DA共享外部M/N,LNA能够提供微分输出以驱动下面的双平衡混频器。本文提出的LNA提供了30 dB的高压增益和10 dB的低压增益用以容纳-105 dBm~-20 dBm范围内的RF输入信号。

在接收器中,由于从5.208 kHz开始全是下变频基带信号,混频器对闪烁噪声的贡献十分关键。作为电流驱动的无源混频器,实现了图2的IQ下变频混频器,其中零中频接收器没有或只有少数闪烁噪声,相较于有源混频器,同样提供更高的线性度及更小的芯片面积。

3 LPF和PLL设计

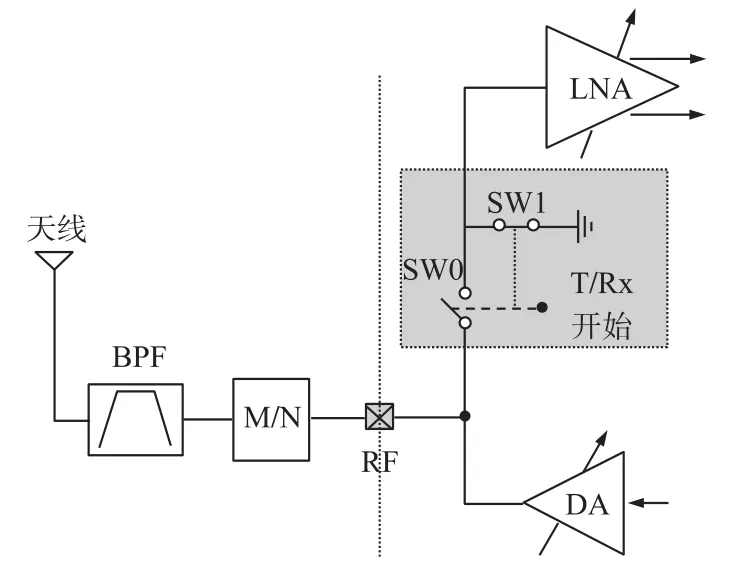

为了实现高线性度,本文提出的收发器中的低通滤波器(LPF)采用了有源RC拓扑,该拓扑比Gm-C LPF等其它LPF类型更平直。图3是本文提出发送器及接收器的有源RC 5级切比雪夫LPF的方框图,该LPF能够提供100 kHz/200 kHz/400 kHz/600 kHz的多信道带宽用以支持所有选项以及阻带中的高衰减量。在本文提出的LPF中,1/(Rs∙C1-5)产生了1-dB的截止带宽,并由抗PVT(过程、电压及温度)的干扰性能强的数控电容器C1-5进行控制。将LPF中采用的运算放大器设计成带有大输出装置用以抑制DC频率附近的闪烁噪声。

图3 本文提出的LPF的电路图

为了在图2中的接收器链实现100 dB的总电压增益,LNA的电压增益为30 dB,并且基带模拟模块(LPF及VGA)为1 dB的阶梯提供了70 dB的电压增益。由于DC偏移能够让整个基带电路处于饱和状态,为了缓解该问题,分别在I及Q基带电路中采用了DC偏移抵消环。模拟结果显示,由于输入DC偏移达400 mV,可以默许模拟基带输出。

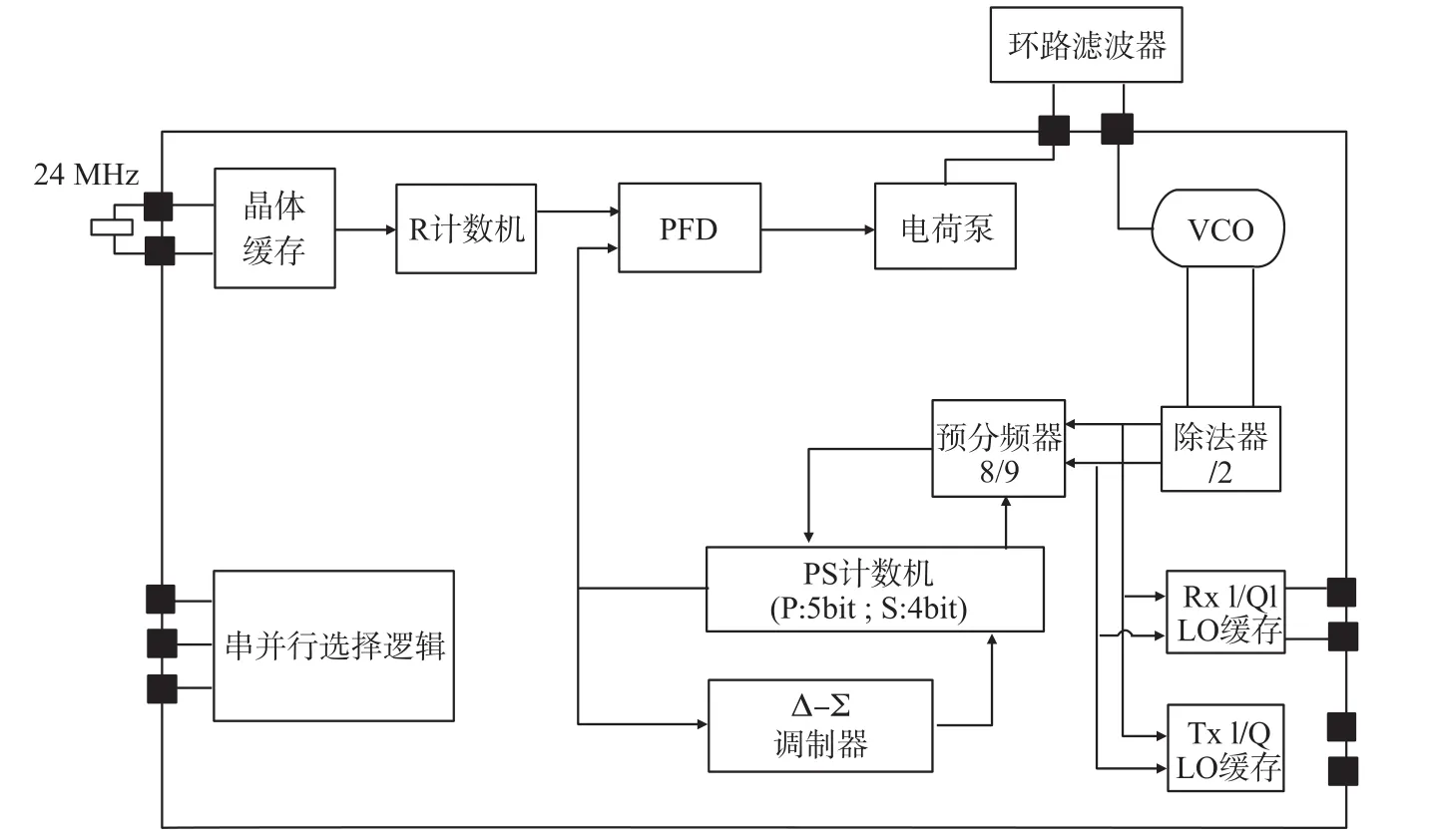

图4是Δ-Σ小数-N频率合成器的电路原理图。其使用了24 MHz的参考时钟,其中互补微分压控振荡器(VCO)两次运行1.4~2 GHz的LO频率。一比二分频电路将微分VCO输出信号转换成图2中上下变频混频器的IQ 920 MHz的LO信号。本文提出的PLL同样采用3级3比特的输出Σ-Δ调制器用以提高接近相位噪声并使分辨率达到91.55Hz。

图4 PLL的电路原理图

对于发送器中的IQ调制及频率上变频,使用了正交电压采样无源混频器,这样线性度高且发送器上不存在LO。

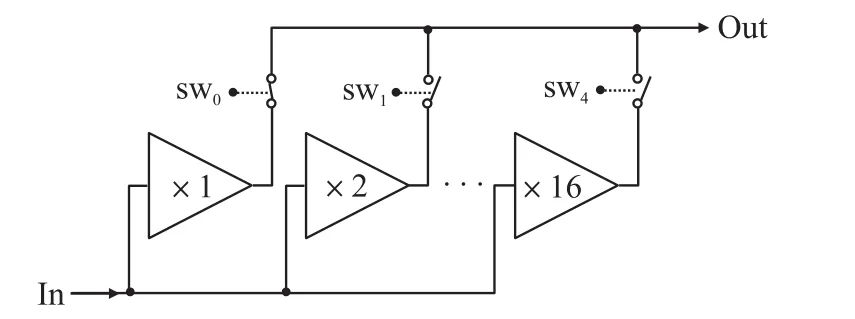

考虑到线性度及功率效率的因素,我们将2级DA设计带有单端拓扑,并包括A类及AB类放大器。A类放大器作为AB类放大器的高电压摆幅提供适度增益及高线性度。第2阶段的放大器是共源共栅的AB类放大器用以实现高效率及高线性度,如图5所示。在本文提出的AB类放大器中,放大晶体管分成二进法装置,通过b0~b4的厚氧化物共源共栅晶体管开关可以开启或关闭该装置。因此,整体DA的DC功率损耗与DA的输出功率水平呈正比。整体DA的可变输出功率的范围为-10 dBm~+10 dBm,并且,当电源电压为1.8 V时,相应的DC功率损耗的范围为8.1 mW~24.3 mW。

图5 可扩展AB类放大器的电路图

4 实验结果与分析

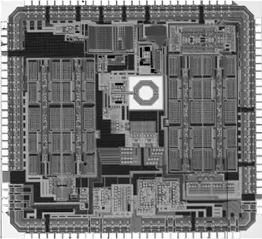

如图6所示,在0.18μm CMOS技术中组装了本文提出的RF收发器原型。图6中,芯片面积为2.8 mm× 3.0 mm。当电源电压为1.8 V时,Tx模式下,组装的RF收发器会消耗14.7 mA,Rx模式下会消耗15.7 mA。

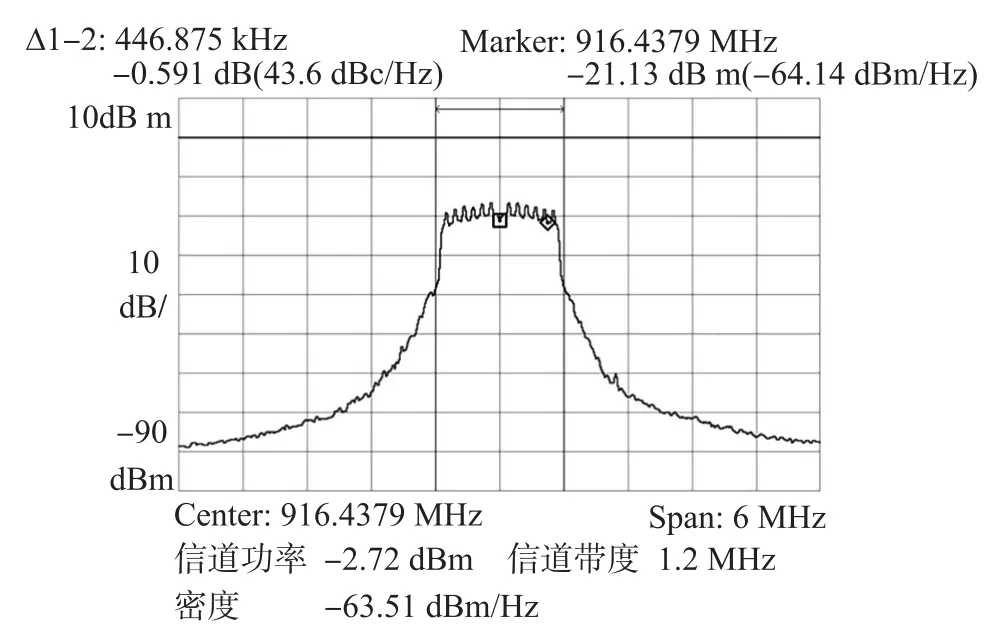

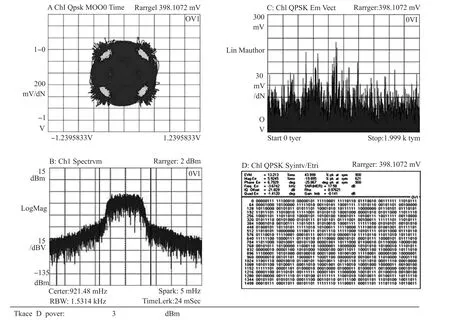

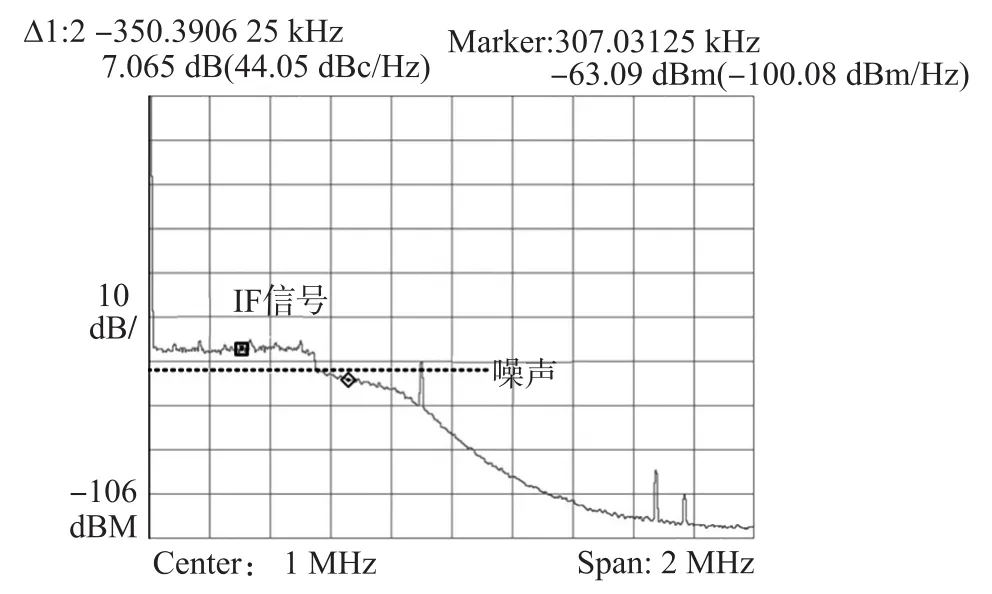

图7为发送输出频谱,其调制方式为QPSK,数据速率为800 kbit/s。考虑到发送器中的峰均功率比为+10 dB,测量的平均信道功率为-2.7 dBm(包括电缆损耗),在测试Tx误差向量幅度(EVM)中,由QPSK调制的正交基带信号用于发送器输出,该信号由向量信号发生器(VSG)发出。如图8所示,当信道功率为+3 dBm时,测量的Tx EVM大约为13%(-17.7 dB);信道功率为-2 dBm时,EVM为-20 dB。图9是接收器输出基带频谱图,其中带宽为600 kHz,可以看出阻带衰减率较好。

图6 组装的RF收发机的芯片图片

图7 发送的输出频谱

图8 信道功率为+3 dBm时的测量的Tx EVM;为了测试Tx EVM,由向量信号发生器(VSG)发出的QPSK调制的正交基带信号用于发送器的输出。

图9 基带输出频谱(信道BW=600 KHz)

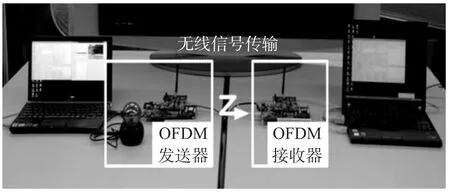

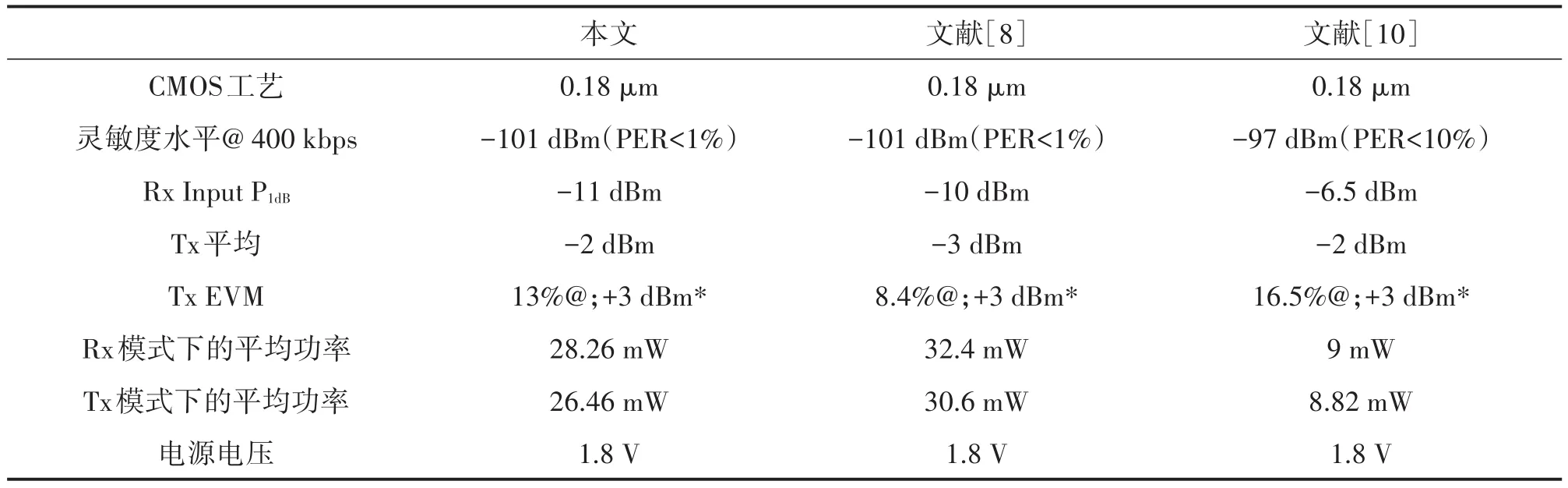

为了测量接收器的灵敏度,在SUN OFDM系统板上对提出的RF收发器进行了测试,如图10所示。包括3个不同的PCBs,上面的PCB用于RF芯片,中间的PCB用于模数转换器/数模转换,底层的PCB用于调制解调器及媒体访问控制(MAC)。模数转换器/数模转换是使用0.18-μm CMOS技术实现的,调制解调器及MAC均设计成带有FPGA。使用该系统板后,评估了组装的RF收发器的灵敏度水平。数据速率为100 kbit/s时,测量的最小灵敏度为-103 dBm且错包率(PER)为1%。该测量的灵敏度水平符合IEEE 802.15.4g OFDM标准,该标准的要求为:数据速率为100 kbit/s时,测量的最小灵敏度为-103 dBm且PER<10%。表1总结了测量的RF收发器的性能,并与其他文献进行了对比,可以看出相比类似收发器[8],提出收发器的灵敏度和误包率相同,但Rx模式和Tx模式工作功耗更低。虽然文献[10]的功耗更低,但是其信号质量指标EVM较差且误包率较大,较低了系统可靠性。

图10 包括RF、调制解调器的FPGA板

表1 收发器性能参数对比

5 结论

本文设计了一种基于OFDM的IEEE 802.15.4g新型低功耗RF收发器,该收发器是使用0.18-μm CMOS技术实现的。测量结果显示,组装的RF收发器芯片很好地满足IEEE 802.15.4g OFDM系统。由于实现的OFDM系统包括RF、调制解调器及MAC,实际测试结果显示,相比传统的RF收发器,在保持灵敏度和误包率均不降低的条件下,提出的RF收发器具有更低的功耗,虽然功耗没有大幅降低,但是系统可靠性没有降低。

[1]由磊,雷建军.认知无线视觉传感网络机会传输的分布式跨层优化[J].天津大学学报,2013(10):910-916.

[2]袁静,高永安.MIMO-OFDM系统中基于空频域导频的信道估计[J].电子器件,2010,33(5):595-598.

[3]殷严刚,王小华,何富运.基于FPGA技术实现的OFDM基带调制系统[J].电子器件,2014,37(1):89-91.

[4]Chin-Sean Sum,Harada H,Zhou Lan,et al.Smart Utility Net⁃works in TV White Space[J].IEEE Comm.Magn,2011,49(2):132-139.

[5]庞娜,程德福.基于ZigBee无线传感器网络的温室监测系统设计[J].吉林大学学报(信息科学版),2010,28(1):55-60.

[6]孟新,肖时茂,于云丰,等.一种用于低功耗低成本的IEEE802.15.4接收器的新颖解调算法[J].电子器件,2008,31(4):1256-1260.

[7]Pilsoon Choi.An Experimental Coin-Sized Radio for Extremely Low Power WPAN(IEEE802.15.4)Application at 2.4 GHz[J]. IEEE J of Solid-State Circuits,2003,12(38):2252-2268.

[8]Wolfram Kluge,Frank Poegel,Matthias Lange,et al.A Fully Inte⁃grated 2.4 GHz IEEE 802.15.4-Comliant Transceiver for ZigBee Application[J].IEEE J of Solid-State Circuits,2006,12(41):2767-2775.

[9]甘业兵,马成炎,袁国顺,等.低功耗Zigbee收发器镜像抑制滤波器设计[J].电子器件,2009,32(3):557-561.

[10]Kim Y J,Hwang I C,Baek D.A Switchless Zigbee Frontend Transceiver With Matching Component Sharing of LNA and PA[J].Microwave&Wireless Components Letters IEEE,2010,20(9):516-518.

[11]姚信威,王万良,吴腾超,等.不同调制机制下无线传感网收发器能耗优化模型[J].传感技术学报,2013,26(8):1140-1146.

徐 进(1972-),男,汉族,江苏泰州人,硕士,副教授,主要研究方向为电路与系统,无损检测;

帅立国(1968-),男,汉族,江苏高邮人,博士。教授、博导,主要研究方向为机器人、无损检测。

A Novel Low Power RF Transceiver Based on OFDM*

XU Jin1,2,SHUAI Liguo2*

(1.SOC R&D Center,Suzhou Institute of Trade&Commerce,Suzhou Jiangsu 215009,China;2.Department of Mechanical Engineering,Southeast University,Nanjing 210096,China)

In order to realize low power consumption,a low power IEEE 802.15.4g radio frequency(RF)transceiver based on OFDM is proposed.The radio frequency(RF)transceiver circuit is composed of the on-chip RF switch front-end,TX BBA(Analog Baseband),RX BBA and phase-locked loop(PLL),fabricated using 0.18μm CMOS technology.The actual test results show that the proposed RF transceiver has lower power consumption and good sensitivity compared with the traditional RF transceiver.When the power supply voltage is 1.8 V,the proposed RF transceiver will consume 14.7 mA in Tx mode,and 15.7 mA in Rx mode.

802.15.4g IEEE;RF transceiver;OFDM;low power consumption

TN802

A

1005-9490(2016)06-1391-06

6250

10.3969/j.issn.1005-9490.2016.06.022

项目来源:国家自然科学基金项目(61175069);江苏省高等职业院校国内高级访问学者计划项目(2014FX120);苏州市2016年度产业前瞻性应用研究(工业)指导性计究项目

2015-11-21 修改日期:2016-01-04