一种基于FPGA的地址学习功能的设计

2016-12-05王辉

王辉

(中国电子科技集团公司 第三十四研究所,广西 桂林541004)

一种基于FPGA的地址学习功能的设计

王辉

(中国电子科技集团公司 第三十四研究所,广西 桂林541004)

当前的综合传输设备中,大多都提供了高速的以太网业务接口,能够直接实现以太网业务的传输。但是,这些传输设备无法实现以太网数据包的地址学习功能,给传输设备和交换设备的组网带来了一定的影响。文章中提出了一种基于FPG A的地址学习功能的设计,以解决对数据包的源m ac地址进行学习和管理。给出了电路原理,详细介绍了硬件接口模块和地址学习模块中的各模块功能,并进行了应用验证。

FPG A;M A C地址;老化

0 引言

当前,传输设备的地址学习功能大多出现在交换设备上。交换设备能够自动学习到达设备端口的以太网数据包的源MAC地址,有利于对数据包的快速转发[1,2]。传输设备一般只提供物理接口,只对数据进行透明传输,不提供源MAC地址的学习功能。当传输设备和交换设备组网时,需要传输设备实时学习和记录接入到传输设备的终端设备(如PC)的MAC地址,并能够适时发送免费的ARP学习包,使得交换设备能够及时更新其与传输设备相连的端口上的MAC地址表。为了实现上述功能,本文在传统传输设备的基础上,采用FPGA[3]的方式,实现了传输设备对接入终端设备的源MAC地址的学习和管理功能[4]。

1 电路原理

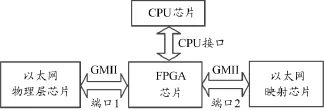

设计时,我们在传输设备以太网板的物理层芯片和映射芯片之间增加了一块FPGA芯片,用来处理收到的数据包,对数据包中的MAC地址进行学习和管理。电路原理如图1所示。FPGA芯片提供了1个CPU接口和2个GMII接口。CPU接口用于连接CPU芯片,2个GMII接口分别用于连接以太网物理层芯片和以太网映射芯片。

图1 电路原理示意图

一方面,FPGA截获从端口1收到的所有的数据包,并获取数据包的源MAC地址,建立端口1的MAC表项(包含MAC地址、IP地址);另一方面,FPGA还能够接收CPU的指令,适时的从端口2发出以端口1的MAC表项构成的免费的ARP包以利于其他设备快速更新其MAC表项。

2 硬件接口模块功能

2.1CPU接口模块

FPGA提供的CPU接口外部采用地址/数据并行总线接口形式,内部设置了一系列的寄存器。CPU芯片可以通过CPU接口对FPGA提供的内部寄存器进行读写,实现CPU对FPGA的功能模块的控制管理。CPU芯片对FPGA的主要控制功能有:MAC地址学习功能的开启和关闭;MAC地址老化时间的设置;MAC地址学习包代理转发功能(传输设备代替接入端口1的终端设备向端口2转发免费的ARP学习包)的开启和关闭;免费的ARP包的发包频率的设置。

2.2GMII接口功能

FPGA的端口1和端口2都是GMII接口,只支持1000Mb/s的速率。FPGA将端口1的GMII信号和端口2的GMII信号通过FIFO转换时钟域,实现物理层和以太网映射芯片之间业务的透传功能。

3 地址学习内部模块功能

3.1以太网数据包地址学习功能

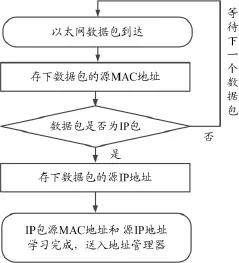

以太网数据包地址学习功能是指FPGA学习从端口1进来IPv4包(非WLAN)的源MAC地址和源IP地址,然后将MAC地址和IP地址送入以太网地址管理器进行比较和保存。

以太网数据包地址学习功能的FPGA逻辑流程图如图2所示。当端口有数据包到达时,FPGA对数据包的字节进行计数。首先,存下数据包的源MAC地址 (第15到第20字节)。然后,存下以太网包类型(第21和22字节)并判断是否为IP包。如果是IP包,则存下IP包的源IP地址(第35到第38字节);如果不是IP包,则结束本次存入过程,等待下一个数据包。最后把源MAC和IP地址送入地址管理器进行比较和保存。

图2 以太网数据包地址学习逻辑流程图

3.2以太网地址管理功能

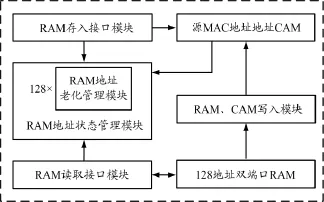

图3为地址管理器示意图。FPGA提供了以太网地址管理功能,包括一个128个地址的双端口RAM、一个内容地址查找表(Contend Address Memory,CAM)、一个RAM和CAM写入模块、一个RAM存入接口模块、一个RAM读取接口模块和一个RAM地址状态管理模块。

图3 地址管理器示意图

各个模块的功能如下:

⑴一个128个地址的双端口RAM。用来存储学习到的源MAC地址表项。

⑵一个CAM。用于比较以太网包的源地址表项是否已经存在于CAM内。

⑶RAM、CAM写入模块。用于将RAM存入接口保存的以太网地址写入RAM和CAM。

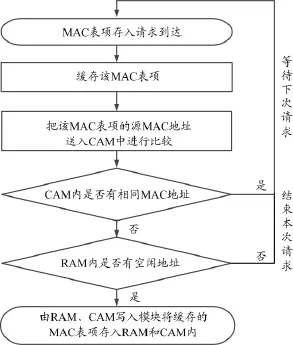

⑷RAM存入接口模块。逻辑流程图如图4所示。首先,地址学习模块获取数据包的源地址并将这些地址送入RAM存入接口模块;然后,RAM存入接口模块缓存这些以太网地址,同时将该地址送入CAM中;最后,CAM查找CAM内部是否有相同的MAC地址。如果CAM内部已经存在相同的MAC地址,则终止本次存入,并产生MAC地址更新信号通知RAM地址状态管理模块更新此MAC地址表项。如果CAM内没有此MAC地址,RAM存入接口模块查询RAM地址状态管理模块是否有未使用的RAM地址。如果没有空闲RAM地址,地址管理器将丢弃该以太网地址;如果有空闲RAM地址,则RAM、CAM写入模块将该MAC地址表项写入RAM内空闲地址中数值最小的地址内,并告诉RAM地址管理模块该RAM地址被使用,结束本次存入。

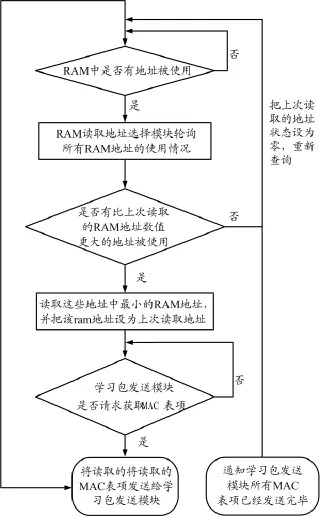

⑸RAM读取接口模块逻辑流程图如图5所示。RAM读取接口模块内部设计了一个状态机,可以将RAM中的存储的MAC表项按照RAM地址从小到大的顺序依次读取出来。状态机持续地检查RAM地址状态管理模块给出的RAM地址使用状态,从RAM中已经使用的地址中最小的地址开始预读取一个MAC表项。当代理转发模块请求MAC表项时,RAM读取接口模块直接将预读取的MAC表项发送给代理转发模块,接着马上去读取RAM中下一个的MAC地址表项,直至不再收到代理转发模块的请求。

图4 RAM存入接口模块逻辑流程图

⑹RAM地址状态管理模块,由128个RAM地址老化管理模块组成,用于管理128个RAM地址的使用及老化状态。逻辑流程图如图6所示。系统刚上电时RAM地址的使用状态默认设置为未使用 (数值为‘0’),老化计数器清零。当RAM的地址状态为“0”时,老化计数器为零且处于不计时状态;当RAM的地址状态为“1”时,老化计数器处于计时状态(时间递增)。有2种情况会使对应的RAM地址的老化计数器清零,并开始计时。第一种情况,有新的MAC表项被写入到RAM中;第二种情况,RAM中原本存在的MAC表项进行了更新。当老化计数器递增到设定的值(默老化时间300s)时,地址保护模块会从源端口发出一个以该MAC表项为目的地址的ARP请求包,询问该MAC地址所在的主机是否存在。如果不存在,则通知RAM地址状态管理器将该RAM地址设置为未使用(即,清除此MAC表项),并清零老化计数器;如果存在,则将该地址老化计数器重新开始计时。

图5 RAM读取接口模块逻辑流程图

图6 RAM地址使用及老化状态管理模块逻辑流程图

3.3MAC地址学习包代理转发功能说明

MAC地址学习包代理转发功能开启后,SDH设备主动模拟接入SDH设备的主机发送免费的arp包,从而更新后端网络设备的MAC表项。此功能使得传输设备与其它设备MAC表项的更新状态保持一致,提高了整个网络的稳定性。

4 应用验证

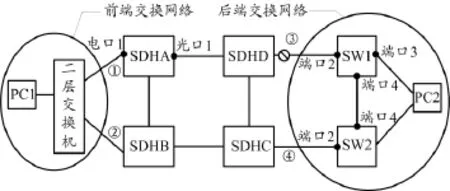

实际应用中网络如图7所示,网络由前端交换网络、后端交换网络和SDH传输网络组成。前后端的交换网络通过SDH传输网络实现前后端的数据交换。SDH网络可以根据与交换网络的链路情况选择一条传输路径连接交换网络。传输网络中SDHA-SDHD为SDH传输设备,后端交换网络SW1和SW2为三层交换机。正常情况下前后端交换网络通过路径①③进行数据交换。当链路③故障时,传输路径自动切换为①④。后端网络SW1和SW2互为主备热备方式。PC2为双网卡终端,能够实现主备网卡的切换。此网络拓扑设计为能够实现网络故障的快速保护。

图7 实际应用网络图

正常通信时,PC1能够收到PC2的单向数据包(此时PC1无任何数据包发出)。但是当链路③故障时,PC1长达几分钟的时间收不到PC2发送的数据包。此情况不符合此冗余网络能够快速保护业务的初衷。排查原因发现:链路③故障时,SW2没有及时更新PC1的MAC地址导致了此情况的发生。正常通信时(路径①③),PC1发送ARP学习包,则SW2的端口4学习到了PC1的MAC地址。当链路③故障时,SDH网络切换到路径①④。由于没有从PC1到PC2的包,因此SW2的端口2上没有PC1的MAC地址。当PC2到PC1的单向包被发送到SW2时,SW2发现PC1和PC2的MAC地址都在端口4上,因此,数据不可能从端口2转发出去,PC1无法收到PC2的数据,直到SW2的端口2上学习到PC1的MAC地址,通信才能恢复。主要取决于端口2上学习到PC1的MAC地址。

如果SDH网络具有地址学习功能,则当SDH网络由路径①③切换到路径①④时,SDH设备同时开启了MAC保护功能,代替PC1向后端网络发送学习包,此时SW2能够通过路径①④迅速学习到PC1的MAC地址,实现交换通道的快速建立,从而实现整个网络的快速切换。因此,增加了地址学习功能的SDH设备能够很好地和交换网络互联,实现网络的快速切换。

5 结束语

以上,我们采用FPGA的方式,实现了传输设备对接入终端设备的源MAC地址的学习和管理功能。通过实际的网络验证可知,增加了地址学习功能的SDH传输网络能够很好地与交换网络互相配合,共同实现整个网络的功能。因此,此功能行之有效,能够很好地解决SDH网络和交换网络互联时引入的地址学习的问题。

[1]程明坤,赵翠华,江云霞.浅释交换机的MAC地址学习的过程及应用[J].数字技术与应用,2012(7):218-218

[2]蒋友,罗惠琼.二层交换机中MAC地址的学习、查找和老化方法[J].软件导刊,2005(20):40-42.

[3]云创工作室.Verilog HDL程序设计与实践[M].北京:人民邮电出版社,2005.

[4]于翔,郑力明,黄红斌.基于FPGA的MAC层地址表设计与仿真[J].计算机工程与设计,2013(1):121-125.

Address learning function design based on FPGA

WANG Hui

(The 34th Research Institute of CETC,Guilin Guangxi 541004,China)

Current integrated transmission equipments mostly provide high-speed Ethernet interface and realize Ethernet business transmission directly.These transmission equipments,however,could not realize the function of address learning for Ethernet packets,which brings a certain influence to the group network of transmission equipment and switching equipment.In the paper,a design of address learning function based on FPGA is proposed to solve the problem of learning and managing the source MAC address of the data packets. The principle of the circuit is given,the function of each module in the hardware interface module and the address learning module is introduced in detail,and the application verification is carried out.

FPGA,MAC address,aging

TN914.332

A

1002-5561(2016)05-0032-04

10.13921/j.cnki.issn1002-5561.2016.05.010

2016-01-11。

王辉(1981-),男,硕士,工程师,主要从事光通信和网络交换方面的工作。