基于MicroBlaze的可靠网络接口设计

2016-11-21侯鸿杰王竹刚

侯鸿杰,王竹刚

(1.中国科学院 国家空间科学中心,北京 100190;2.中国科学院大学 北京100190)

基于MicroBlaze的可靠网络接口设计

侯鸿杰1,2,王竹刚1

(1.中国科学院 国家空间科学中心,北京 100190;2.中国科学院大学 北京100190)

Microblaze是Xilinx公司设计一种软核SOPC,它是FPGA芯片内部逻辑组成的一种32位软核嵌入式处理器。为了实现数据从FPGA到计算机的高速传递,本文介绍了一种基于uIP及LwIP的网络协议栈,提出了一种可靠UDP(reliable UDP,RLUDP)协议,并完成了嵌入式TCP/IP协议栈设计与实现,实现了PC与MicroBlaze的高速数据传输,并对其性能进行了简单的测试,最终达到了设计要求。

MicroBlaze;SOPC;可靠UDP;嵌入式TCP/IP

现场可编程门阵列(FPGA)广泛应用于数传,遥测,调制解调等领域。随着我国测控通信技术的极速发展,对通信基带数据发射和接收的速度及实时性要求日渐提高。针对FPGA与计算机等信源信宿的高速数传需求,需要有一种基于现有通信协议的解决方案。网络方式可以满足长距离(100 m及以上级别)的高速数传需求。近年来SOPC技术得到了迅速的发展,基于FPGA的SOPC系统结合FPGA及微处理器的优点在点对点数传方面的得到了广泛应用。文献[1]描述了一种基于MicroBlaze的嵌入式协议栈移植,并搭建了简单LED外设进行验证。文献[2]提出了基于FPGA的Micro Blaze+DM9000网卡以太网接口方案,并实现了TCP,UDP通信。基于以上需求及成功的应用案例本文采用了Xilinx的FPGA,并使用其嵌入式软核处理器MicroBlaze,采用嵌入式TCP/IP协议栈的方法实现了高速数传。

1 系统总体设计

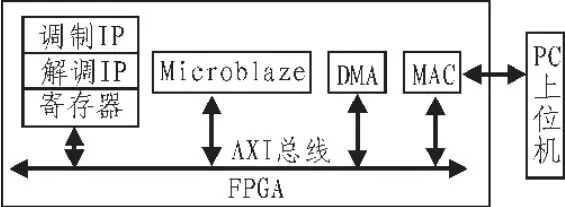

系统总体硬件框图如图1所示,系统分为两部分,分别PC上位机和FPGA,FPGA端包括MicroBlaze处理器系统[3-5],调制解调软核,PC端主要为上位机。数据调制解调模块主要完成通信物理层相关的数字信号处理工作,MicroBlaze是本系统的核心,在其上运行嵌入式TCP/IP协议栈,其他模块包括基于DMA[6]的千兆网卡MAC IP核[7],LED外设[8]等。PC上位机是协议栈的客户端点,完成数据收发请求,寄存器配置,连接建立保持等功能。FPGA采用了Xilinx的7系列芯片,由于调制解调数据有高速传输需求,因此采用的是千兆网卡的MAC IP核。

图1 系统总体结构图

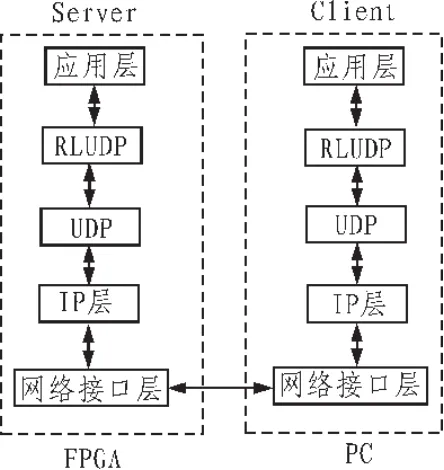

本系统的数传端点分别为FPGA和PC,对于FPGA协议栈选择了在MicroBlaze中实现,总体的协议栈参考模型如图2所示,FPGA网络接口层使用的是Xilinx的千兆以太网IP核,其余各层则在MicroBlaze中实现。PC端采用Windows操作系统,使用MFC界面[9],用户代码主要完成传输层以上的处理。

图2 系统协议栈模型

2 可靠UDP协议设计

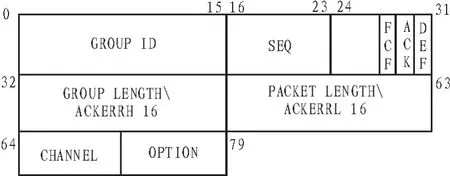

UDP协议是一种面向无连接的协议[10],它不提供可靠性,如果数据包发生丢失UDP也不提供丢失信息。然而由于没有确认信息,差错信息的额外开销,UDP相比于TCP具有了高速的特点。由于点对点的近距离网络通信环境误码率较低,并且由于网卡内部缓冲区有限,可能存在丢包的现象,因此设计一种通过重传来保证可靠性的UDP成为了最佳选择。SOPC作为嵌入式系统内存资源有限,在高速通信时可能存在缓存区溢出的情况,因此需要对UDP数据包的发送速率进行控制,本文设计的可靠UDP协议主要包括了两部分:超时重传,流量控制。在标准的TCP/IP的协议栈基础上加入超时重传,流量控制功能,RLUDP的首部设计如图3所示。

图3 可靠UDP首部

其各字段为:

GROUP ID(组标示号):一次传输单元(组)的唯一标示,即同一组的数据包GROUP ID字段相同,GROUP ID的长度为16位。

SEQ(包序列号):一个传输组中的单个数据包的序列号,长度为8位,功能为标示其在一个数据组的前后顺序,一组中第一个数据包的SEQ为0。

FLAG(标志):8位,各个位有不同的功能,DEF位表示一个组的最后一个包,ACK位代表确认包,FCF位代表流量控制标志,其余5位保留。

GROUP LENGTH/ACKERR H16:GROUP LENGTH表示一个组携带的数据总长度(不包括首部),以字节为单位,该字段长度为16位。ACKERR H16表示该字段对应位置在数据确认包首部中表示数据丢失掩码的高16位。

PACKET LENGTH/ACKERR L16:PACKET LENGTH表示本数据包所携带的数据长度,以字节为单位,长度为16位,该字段大小不超过网络的MTU与协议首部的长度差。ACKERR L16表示该字段对应位置在数据确认包中标示数据丢失掩码的低16位。

CHANNEL(通道号):RLUDP通道号,长度为8位,通道号与应用层传输需求对应。

OPTION(选项):8位,保留。

ACKERR中各个二进制位对应一组中数据包的SEQ序列号,序列号为n的数据包对应ACKERR的第n位二进制位。本协议一组最大包个数为32个。

RLUDP使用通道(channel)的方式来满足应用层的不同传输要求,即调制数据的发送功能占用一个通道,调制数据的接收功能占用一个通道,寄存器读写占用一个通道,通过该方式可实现RLUDP层的复用,各通道之间相互独立,其功能与传输层的端口功能类似,在所有的通道中0号通道为特殊通道,用于维护PC与FPGA端的连接信息。针对点对点简单通信环境,RLUDP并未使用类似于TCP的3次握手过程。当PC端启动时,PC向FPGA发送连接询问包,其首部中SEQ字段为0xFF,CHANNEL字段为0,其余字段也均为0。该通道用于探测FPGA端的协议栈是否处于活动状态,连接询问包始终由PC发送,在空闲时段,每隔一定时间就发送该询问包,FPGA返回的响应包仅仅将对应询问包中的ACK置位。若PC收到响应包,则表示连接存在,若约定时间内未收到响应包,则表示FPGA端未处于活动状态,PC端上位机释放所有通道的缓存数据,禁止所有数据的传输功能。此时,由用户决定是否重连FPGA。

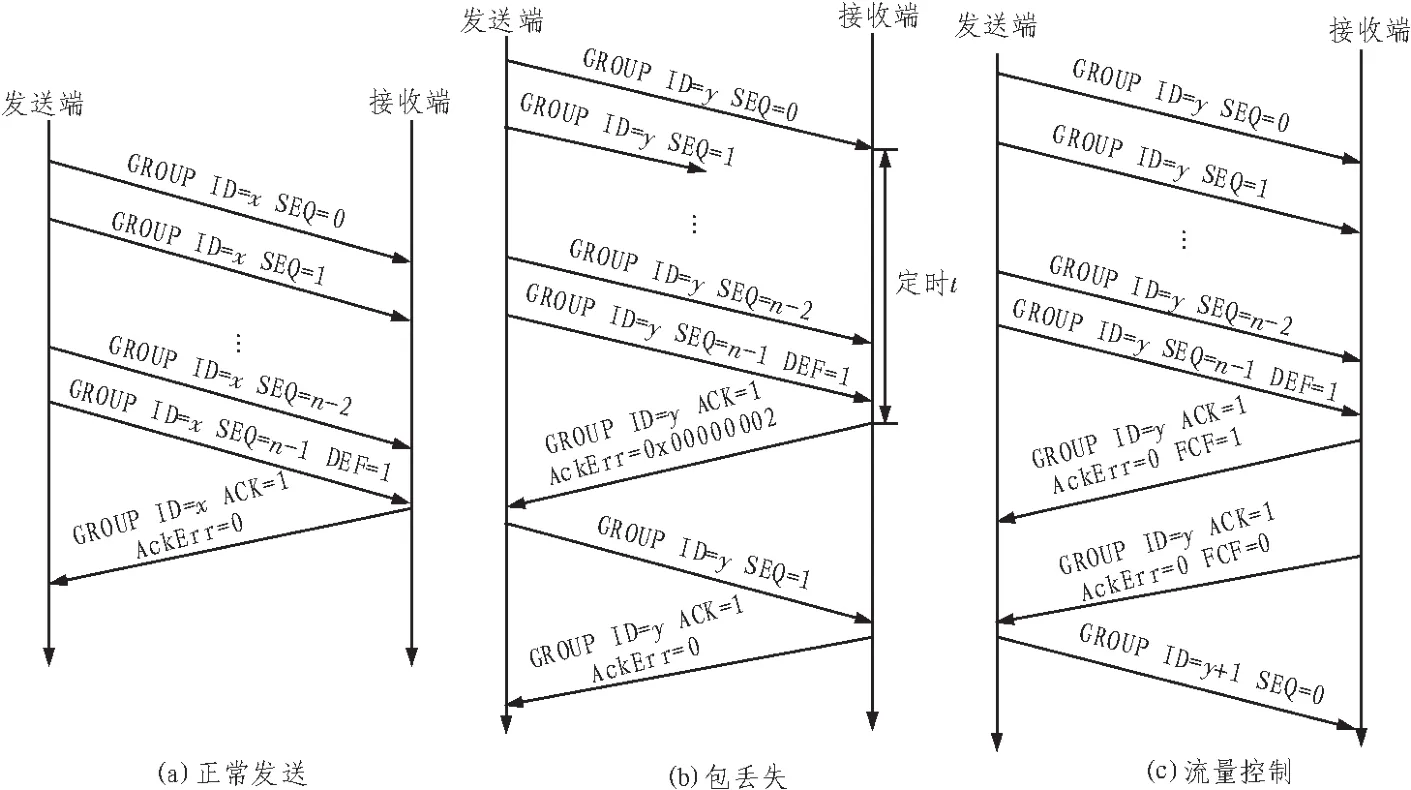

数据收发过程:发送端一次发送一组数据包 (n个包,ACK为0),等待ACK包(flag字段中ACK置1的包)。接收端在接收到一个包后检查GROUP ID是否和之前的相同,若相同丢弃该包,若不相同则启动定时器,如图4(a)所示,若在规定时间段内收到完整一组包,则向发送端发送ACK包,ACK ERR字段为全零,图 4(b)中规定时间内未收到完整一组包返回ACK包并在ACKERR中指明丢失包的序号。由于SEQ指明了数据包在一组的序号,所以即使发生乱序也能将顺序纠正,n值的选取直接影响了发送的速率,n值越大,应答的效率越高,等价传输的速率就越快,然而对于FPGA而言却需要更大的缓冲区。

如图 4(c)所示,若在接收完一组包后缓冲区大小小于设定值,则将返回的ACK包flag标志中FCF置位,PC端对应通道停止发送数据包,处于等待状态。直到FPGA缓冲区大小大于设定值后发送该组ACK包,FCF复位。

3 上位机程序设计

在PC端,通道号与应用层数据传输功能进行了绑定,每个数据传输功能均由一个线程来完成。应用层数据传输需求包括3个线程,数据下行线程,数据上行线程,寄存器配置线程。RLUDP协议实现包括两个线程:RS(Receive and Store)线程,RLU(Reliable UDP)线程。RS线程位于RLUDP的最底层,该线程主要负责数据包的接收工作,区分ACK包 (Flag中ACK置位)和DATA包(Flag中ACK复位)以及连接响应包(CHANNEL为0),ACK包和DATA包存放于相应的包队列中,同时向RLU线程发送数据包到来的消息。RLU线程是RLUDP的核心线程,该线程工作于消息驱动模式,功能包括RLUDP协议主要部分:通道复用,通道分用,流量控制,数据发送,数据接收。

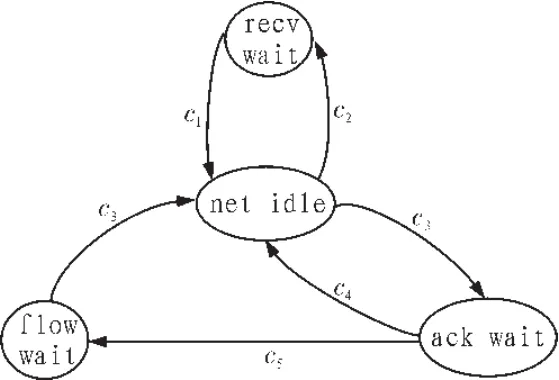

单个通道通过状态机的模式来严格控制数据传输,其状态机如图5所示。其中有 4个状态 net idle,recv wait,ack wait,flow wait。

图4 可靠UDP发送过程

图5 可靠UDP程序状态机

其中各个转换条件为:c1表示一组中所有包接收完毕,c2表示收到一组中一个包,c3表示包发送完毕,c4表示接收到ACK包(FCF=0),c5表示接收到ACK包(FCF=1)。每个通道(0号除外)的初始状态为net idle,当应用层的某个线程要发送一组数据时,就将数据存入该线程对应通道的RLUDP类对象的数据缓冲区中,并通知RLU线程,发送该组数据。此时若该通道的RLU状态为net idle那么就将该组数据的各个数据包加上RLU的协议首部,发送一组数据,接着就将RLU状态置为ack wait状态,等待ACK包的到来。若收到了ACK包,就检查是否无数据包丢失,若无丢失就向应用层相应的线程发送消息,通知应用层该组数据已经发送成功,同时将RLU状态置为net idle状态。若有数据包丢失就发送丢失的数据包,直到收到ACK包指示无数据丢失为止,应用层要接收数据时,向FPGA应用层发送通知包,该通道处于net idle状态,接收到数据包后转换为recv wait状态接收完一组包后就转换为net idle状态。

当FPGA内存剩余空间大小小于指定阈值时,将RLUDP的ACK确认包首部的FCF字段置一,PC端接收到该ACK包就将相应的通道RLU状态置为flow wait状态,此时应用层线程阻塞在消息等待处,就不会继续发送下一组数据。当FPGA的内存空间大于阈值时就再次发送ACK数据包并清除相应的FCF标志,此时PC收到该ACK包后就将向应用层线程发送该组数据发送完成的消息,应用层可继续发送下一组数据,同时RLU状态置为net idle。

4 MicroBlaze嵌入式TCP/IP协议栈程序设计

本协议栈的传输层及以下各协议根据uIP和LwIP协议改写。uIP和LwIP是瑞典计算机科学院的AdamDunkels等开发嵌入式TCP/IP协议栈,uIP协议栈针对嵌入式系统资源有限的特点保留了网络通讯必须的协议[11]。LwIP的主要目的是在保持 TCP/IP协议主要功能的情况下减少对 RAM的使用[12-13]。在MicroBlaze处理器的主频限制下,LwIP其他功能会占用大量的时间,从而导致数传的时间片有限,无法保证较高的传输速率。

针对高速数传需求,本协议在uIP的基础上,保留了ARP,IP,ICMP,UDP,在UDP之上架设一层可靠UDP协议。采用LwIP的协议栈内存管理模型,在内存中申请一片缓冲池,使用队列方式来对内存进行管理,提供内存的申请释放API。MicroBlzae系统采用Xilinx XPS环境开发[14],软件开发环境为EDK[15],协议栈各层的设计如下:

1)网络接口层:使用了FPGA的DMA模式下MAC IP核,在协议栈初始化阶段将自定义的内存区指针交给DMA,在MAC IP核中由DMA对该内存区进行操作,数据发送操作也是向DMA传递指针。2)ARP协议:接收操作对底层接收的数据包进行解析,只对广播包机地址为本机的包进行处理,发送操作在初始化阶段发送ARP请求,并执行退避算法,在已存在目标IP映射的情况下,填充MAC地址,以太网协议类型字段0x8000。3)IP协议:接收操作对底层接收的数据包长度,校验和,及协议等字段进行解析,只处理合法的UDP和ICMP包;发送操作完成IP首部各字段填充。4)ICMP协议:对收到的ECHO请求包进行应答。5)UDP协议:接收操作对端口号进行解析,处理端口匹配的数据包,发送操作对UDP首部进行填充。

5 系统性能测试

系统性能测试主要为数据速率的测试,运行MicroBlaze,主频配置为最大值100 MHz。性能测试分为两个方向:PC到FPGA,发送116 MB的文件,FPGA只进行接收操作,测试不同的n值(一组包中包的个数)对速率的影响,以及其他一些简单的功能测试。进行测试时,首先在PC端进行ping的测试如图6所示,PC端可成功ping通FPGA,用WireShark抓包软件可看到ping相关的ARP包,ICMP包,接着进行功能复用测试,在发送调制数据的同时对寄存器进行读写操作,可成功配置寄存器,观察LED可看到配置的寄存器值。

图6 WireShark抓取的ICMP包

速率测试,改变n值测试文件传输时间,得出传输速率,n值对应速率测试结果如表1所示。从表中可以看出n值越大速率越高。

表1 速率测试结果

6 结 论

经过改写后的TCP/IP协议栈加上RLUDP协议可完成丢包环境下的数据传输,该通信处理器应用于SOPC环境下的测控通信数据传输,通过接收确认方式完成了高速通信数据的传输功能。上位机采用多线程方式,通过多通道的方法完成了FPGA[16-17]下位机多功能复用。文中的流量控制方法很好的解决了CPU在内存资源有限的条件下,对数据传输速率的动态控制问题,目前该接口已应用于相关的测控通信系统,运行状态稳定可靠,速率高,达到了系统设计需求。

[1]高一沅,黄春晖.基于MicroBlaze的以太网通信系统平台设计的研究[J].现代电子技术,2007(17):29-31.

[2]薛昊,佘勇,姚振东,等.基于MicroBlaze和DM9000A的以太网接口设计[J].通信技术,2013(2):32-34.

[3]何宾.基于AXI4的可编程SOC系统设计[M].北京:清华大学出版社,2011.

[4]Xilinx Inc.MicroBlaze Processor Reference Guide[EB/OL].http: //www.xilinx.com/support/documentation/sw_manuals/xilinx14_ 3/mb_ref_guide.pdf

[5]Xilinx Inc.LogiCORE IP AXI Timer v1.03a[EB/OL](2012). http://www.xilinx.com.

[6]Xilinx Inc.LogiCORE IP AXI Ethernet v3.01a[EB/OL](2012).http://www.xilinx.com/support/documentation/ip_documentation/axi_ethernet/v3_01_a/ds759_axi_ethernet.pdf.

[7]Xilinx Inc.LogiCORE IP AXI DMA v6.02a[EB/OL](2012). http://www.xilinx.com.

[8]Xilinx Inc.LogiCORE IP AXI GPIO v1.01.b[EB/OL](2012). http://www.xilinx.com.

[9]孙鑫.VC++深入详解[M].北京:电子工业出版社,2013.

[10]W.Richard Stevens TCP/IP详解卷1:协议[M].范建华,胥光辉,等译.北京:机械工业出版社,2014.

[11]Dunkels A.uIP-A Free Small TCP/IP Stack[EB/OL].(2002-01-15).http://www.sics.se/adam/uip.

[12]Dunkels A.Design an implementation of the LwIP TCP/IP Stack[EB/OL].http://www.sics.se/adam/lwip.

[13]张燕芳,沈丽.基于Xilinx Spartan-3E和LwIP协议的以太网通讯[J].核电子学与探测技术,2013(5):540-543.

[14]Xilinx Inc.EDK Profiling User Guide[EB/OL](2012).http:// www.xilinx.com.

[15]Xilinx Inc.OS and Libraries Document Collection[EB/OL](2013).http://www.xilinx.com.

[16]李威,翟社平.模拟路标识别及其FPGA实现[J].电子科技,2016(2):45-47.

[17]党俊博,李哲,李雅俊.基于FPGA的串口通信电路设计与实现[J].电子科技,2016(7):106-109.

Design of reliable network interface based on MicroBlaze

HOU Hong-jie1,2,WANG Zhu-gang1

(1.National Space Science Center,Chinese Academy of Sciences,Beijing 100190,China;2.University of Chinese Academy of Sciences,Beijing 100190,China)

Microblaze is a kind of soft-core SOPC designed by Xilinx.It is a 32-bit soft-core embedded processor that consist of FPGA logic units.In order to achieve high-rate data transmission from FPGA to computer,a reliable UDP(RLUDP)protocol is proposed in this paper based on uIP and LwIP network protocol stacks.This paper introduces the design and implement of embedded TCP/IP protocol stacks,and illustrates the high-rate data transmission between PC and MicroBlaze according to the proposed protocol.Simple test on system performance is described,which shows that the designed system meets the design requirement.

MicroBlaze;SOPC;reliable UDP;Embeded TCP/IP

TN925

A

1674-6236(2016)21-0105-04

2015-11-12稿件编号:201511117

侯鸿杰(1991—),男,四川宜宾人,硕士研究生。研究方向:时间驯服与时间同步,嵌入式技术。