基于SOPC和FPGA的智能机器人无线通讯系统设计

2016-11-16周瑞钊王和明

周瑞钊,王和明

(空军工程大学防空反导学院,西安710051)

基于SOPC和FPGA的智能机器人无线通讯系统设计

周瑞钊,王和明

(空军工程大学防空反导学院,西安710051)

针对单处理器系统控制的机器人,其无线通信系统存在丢包现象和实时性差等弊端,设计了一种以FPGA作为机器人的主控制器,以PT2262/2272为通信芯片的无线通讯系统。该设计包括无线发射模块、接收模块、SOPC建立及软件实现。研究结果表明,该方案实现灵活,具有体积小、稳定性高、实时性好等优点,不仅解决了丢包的问题,而且具有一定的可扩展性。

FPGA,机器人,无线通讯,PT2262/2272,SOPC

0 引言

小型智能机器人融合机械设计、自动控制、无线通信、图像识别等多项技术,其中,无线通信系统是衔接主机和场地机器人不可缺少的一环。

目前国内多数的智能机器人都是基于传统的SOC系统,主控制器采用DSP,其运算速度快、成本低。但是这些基于SOC(SystemOn Chip)的设计方案在整个电路的复杂度和设计等方面存在很多的缺点,例如需要增加很多的芯片和分立元件,不仅增大体积,功耗较大,而且不利于系统的硬件升级[1]。通信时,利用定时器或者查询的方式实现无线数据的收发,这种方案既难以保证数据传输的高速和稳定,而且还会出现丢包现象,导致机器人失控。

本设计采用FPGA作为主控制器,以SOPC(SystemOnProgrammableChip)的设计方法进行设计,嵌入NIOSⅡ处理器。SOPC是用可编程逻辑技术把整个系统放到一片硅片上的一种特殊嵌入式系统。一方面,它片上系统(SOC)完成整个系统的逻辑功能;另一方面,它是可编程系统,具有灵活的设计方式,可裁剪、扩充、升级,并具备软硬件在系统可编程功能[2]。本设计通信芯片采用PT2262/2272,利用FPGA硬件可编程的特点,将通信芯片在FPGA内部与智能机器人的NIOSⅡ控制器进行连接,从而简化系统的设计,减小系统的体积,也便于对硬件进行修改、仿真以及系统的升级。

1 整体设计

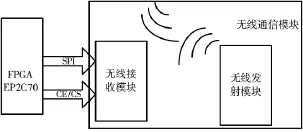

如图1所示,本系统主要由三大模块组成:FP GA、无线发射模块和无线接收模块。无线发射模块主要由PT2262组成,发射无线信号,由PT2272组成的无线接收模块只接收与本机设定相同的地址码。PT2272接收完数据,输出高电平,FPGA进行读取数据。

图1 系统组成框图

2 硬件设计

2.1发射模块电路设计

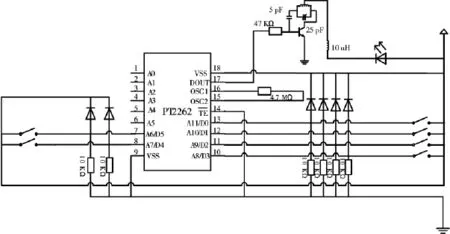

PT2262/2272湾普城公司生产的一种CMOS工艺制造的低功耗低价位通用编解码电路,其最多可有12位(A0~A11)三态地址端管脚(悬空、接高电平、接低电平),任意组合可提供531441址码[3],PT2262最多可有6位(D0~D5)数据端管脚,设定的地址码和数据码从17脚串行输出,可用于无线遥控发射电路。

以PT2262构成的发射电路如图2所示,为方便考虑,本设计主要控制机器人的前进、后退、抬头、低头、蹲下、起立,因此选择六位地址编码。故将A0~A5六位地址悬空,实际应用中智能机器人接收的指令较多,A0~A5能够提供36个地址,可以通过增加单片机用I/O线对地址进行设定。

图2 无线发射电路图

2.2接收模块电路设计

接收模块以安装在机器人身上的芯片PT2272为主,电路如下页图3所示:为了同发射电路地址保持一致,PT2272的A0~A5地址悬空,D0~D5有数据时输出5 V左右的高电平(FPGA端口电压为3.3 V,故需要稳压芯片,选择AMS1117进行分压),驱动电流约2 mA,与发射器上的6个按键一一对应;此接收电路为超再生接收模式,包含选频网络、放大、整形等电路;天线输入端有选频电路,而不依赖1/4波长天线的选频作用,控制距离较近时可以剪短甚至去掉外接天线;接收电路自身辐射极小,加上电路模块背面网状接地铜箔的屏蔽作用,可以减少自身振荡的泄漏和外界干扰信号的侵入[4]。

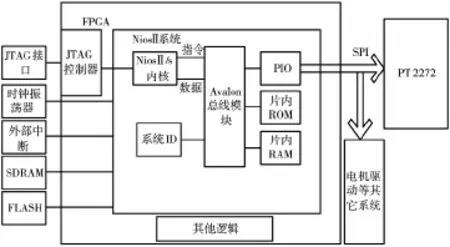

2.3SOPC设计

本设计采用FPGA器件EP2C35F672C6ES作为主控器,它是Altera公司生产CycloneⅡ系列芯片。其硬件资源包含有33 216个逻辑单元LE,105个M4K RAM块,483 840个RAM位,35个嵌入式18×18乘法器,4个锁相环,最大可用I/O管脚475个,205个差分通道[5]。

利用QuartusⅡ构建基于FPGA的SOPC系统如图4所示。NiosⅡ系统包含NiosⅡ/s处理器、Avalon总线、片内ROM、片内RAM以及PIO线;NiosⅡ外围设备包括JTAG控制器、外部时钟、外部中断。本设计配置了8MB的SDRAMIS42S16400B,4MB的FLASH S29AL032D70TF104,当片内RAM不够存储时,可以将程序储存在SDRAM或FLASH,非常方便后续升级对系统容量的需求。

图3 无线接收电路图

图4 SOPC系统框图

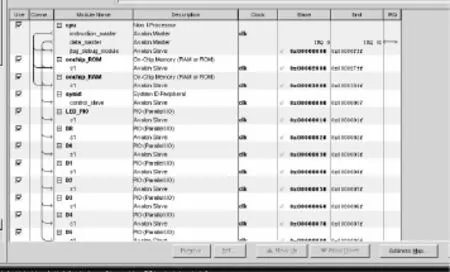

打开QuartusⅡ的SOPC Builder,如图5所示,依次添加CPU、RAM、ROM、PIO等,给处理器分配复位向量地址和异常向量地址,然后外设一个中断优先级,配置成功提示:Systemgeneration was successful。

图5 添加元件窗口图

图6 系统硬件电路图

智能机器人包含通讯系统、电机驱动系统等,可以通过SPI等与FPGA进行连接,本文只研究通讯系统。FPGA与PT2272的连接如图6所示,clk是NiosⅡ/s处理器的时钟引脚,reset_n是复位引脚,DR是外部输入中断;D0~D5作为FPGA与PT2272的SPI接口;为调试系统是否正常运行,增加LED_PIO输出来控制LED灯。

3 系统软件设计

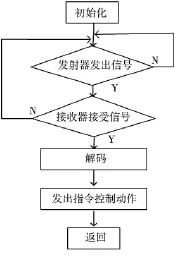

软件程序设计的主要部分是PT2272与FPGA的数据传送,设计的主要思路是:PT2262发出信号,PT2272判断是否接收到信号,若收到信号由FPGA解码,解码后再发出指令控制机器人相应的动作。程序框图如图7所示。

图7 系统软件流程图

4 测试过程

为验证该系统的可行性,用AlteraDE2开发板进行测试。DE2开发板有18个拨动开关4个按钮开关,8个贴片发光二极管,8个7段数码管,其外围电子原件和板上的核心FPGA芯片CycloneⅡEP2C35F672C6连接,可完成基于FPGA/CPLD芯片的电路设计。本测试过程用LEDG0亮灭检验系统是否可行,LEDGO与FPGA的PIN_AE22连接。

测试原理是:用NIOSⅡ控制DE2开发板上的LEDG0亮灭,SYS_CLK、SYS_nRST分别配置FPGA的PIN_N25、PIN_N26管脚,LED_TEST配置PIN_AE22管脚。当主机发送数据01或10时,LEDG0闪亮;当发送11时,LEDGO熄灭。

具体过程为:将已经构建好的SOPC添加到工程中,经编译、配置后用下载线USB-Blaster下载至FPGA,下载模式为JTAG,下载成功提示:Programmeroperationwassuccessful。如图8所示。实验结果验证了该系统的可行性,说明该无线通讯系统满足通讯要求。

图8 程序编译及下载

5 结论

本研究主要介绍了基于FPGA为主控器的机器人无线通信硬件和软件设计,并对SOPC的设计进行介绍,且实验结果验证了设计的可行性,保证数据传输的高速和稳定,有效解决了丢包现象,具有体积小、稳定性高、实时性好等优点。在SOPC系统中,软硬件都可以编程,从而为硬件系统的灵活配置和软件系统的灵活设计提供了方便,也有利于系统的优化和升级。尤其这种量体裁衣的硬件配置方式,可以最大限度地提高系统的性价比,同时也可以利用HardCopy技术,将成功实现于FPGA器件上的SOPC系统通过特定的技术直接向ASIC转化[5]。但实际中智能机器人得到的指令远比本设计复杂,因此,在信号发射模块还需要再作进一步的研究和改进。

[1]汪明,赵晓,李晓明.基于FPGA的小型足球机器人无线通信子系统的设计[J].机电工程,2011,11(28):1386-1390.

[2]任爱锋,初秀琴,常存,等.基于FPGA的嵌入式系统设计[M].西安:西安电子科技大学出版社,2004.

[3]普诚科技.PT2262数据手册[EB/OL].[2011-01-01].http://www.princeton.com.tw/downloadpro-cess/downloadfile.asp? Mydownload=PT2262_4.PDF.

[4]新世纪电子研究所.超外差无线接收模块J05U技术规格书[R].安阳:安阳市新世纪电子研究所,2011.

[5]周立功.SOPC嵌入式系统基础教程[M].北京:北京航空航天大学出版社,2006.

Wireless Communication System Design of Intelligent Robot Based on FPGA

ZHOU Rui-zhao,WANG He-ming

(School of Air and Missile Defense,Air Force Engineering University,Xi’an 710051,China)

In view of the single processor system to control the robot,the wireless communication system existing packet loss,poor real-time.The paper designs a wireless communication system of robot,which uses FPGA as the core controller and PT2262/2272 as the communication chip.The design includes wireless emission module,receiver module,SOPC building and software.Results show that this scheme has high stability and flexibility,it has many advantages of small size,more realtime.The scheme not only solves the problem of packet loss but also has a certain degree of scalability.

FPGA,robot,wirelesscommunication,PT2262/2272,SOPC

TP242.6

A

1002-0640(2016)10-0188-04

2015-08-11

2015-09-25

周瑞钊(1991-),男,陕西宝鸡人,硕士研究生。研究方向:微电子技术应用。