DSP平台下ARINC429总线的驱动设计

2016-11-09周加谊徐碧辉中国兵器工业第五八研究所四川绵阳621000

周加谊,官 琴,徐碧辉(中国兵器工业第五八研究所 四川 绵阳621000)

DSP平台下ARINC429总线的驱动设计

周加谊,官 琴,徐碧辉

(中国兵器工业第五八研究所 四川 绵阳621000)

针对某航空弹载设备在DSP平台下与其他ARINC429设备之间数据通信这一关键问题,通过分析ARINC429总线协议芯片HI3584的具体功能,利用软件工程化方法,设计出通用性良好的ARINC429总线驱动程序,并给出了驱动程序的实现过程。测试结果证明,该驱动程序满足了设计的需求,具有稳定性好、可靠性高、通用性强等特点,在以后的类似项目中仅做少许修改便能直接应用。

ARINC429总线;数字信号处理;驱动设计;HI3584

在现代飞机上,大量信息在系统与系统、系统与部件之间高速传递。目前,相当数量的军用机、民用机及运输机的数据通信都采用机载数据总线ARINC429[1]。ARINC429总线结构简单、性能稳定,抗干扰性强。最大的优势在于可靠性高,这是由于其非集中控制、传输可靠、错误隔离性好。在x86、PowerPC、ARM等处理器下,通常选用功能齐全且通用性较好的操作系统,例如Windows系列、VxWorks、Linux等,软件工程师将设计好的驱动程序直接递交给这类操作系统,并不直接和用户的应用程序交互[2-4]。而在DSP平台下,通常采用简易实时嵌入式操作系统DSP/BIOS,由应用程序直接调用驱动程序,因此驱动程序的设计更为复杂,需充分考虑应用层的需求和程序的健壮性,这样才能保证程序稳定可靠。

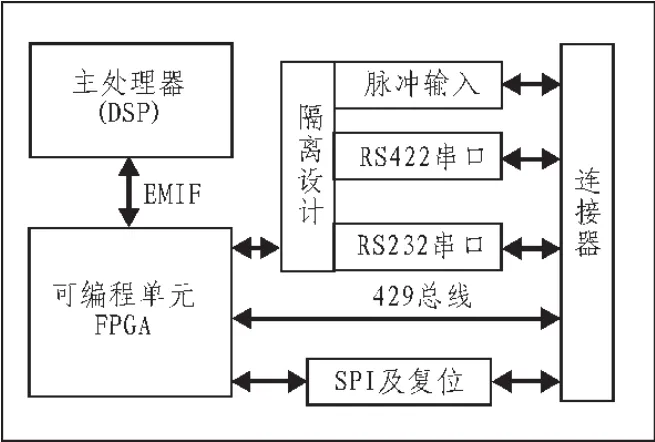

1 系统方案

图1系统组成示意图,为某弹载计算机运算控制模块,其主要包括主处理器(DSP)、可编程单元(FPGA)、存储器和外围接口组件。计算机运算控制模块负责对采集的信号进行解算处理,根据处理结果对外部设备进行实时控制。其接口功能包括ARINC429、RS232、RS422、脉冲输入、SPI接口、复位信号输入等。

主处理器采用TI公司型号为SM32C6713BGDPA20EP的DSP。该芯片具有200 M速率和1 200 M FLOPS运算能力,内部两级缓存架构,拥有一级4 kB程序缓存和4 kB数据缓存及256 kB二级缓存等特性。计算机运算控制模块的信息处理和数据运算由DSP完成,并处理部分中断事件和板间通信。

可编程单元采用XILINX公司型号为XC3S400-4FTG256I的FPGA,通过EMIF总线与DSP相连,协助DSP完成接口功能控制。该芯片拥有400 k系统门数,896个可配置逻辑模块(CLB),56 k分布式RAM,288 k嵌入式BRAM,173个用户I/O。该处理器容量和资源能满足本设计需求。

ARINC429总线控制器采用HOLT型号为HI3584的协议芯片。由于DSP的引脚有限,主处理器需借用FPGA扩展引脚,如图1所示。总线协议芯片HI3584通过并行数据线与可编程单元FPGA互联,接收控制指令,以此实现单体与机载控制终端的ARINC429协议数据交互。

图1 系统组成示意图

2 HI3584芯片分析

HI3584芯片具有一个发送器和两个接收器 (以下简称R1和R2),发送器和两个接收器都具有独立的32×32 FIFO。该芯片能高效可靠实现16位并行数据与ARINC429串行数据的转换功能[1]。

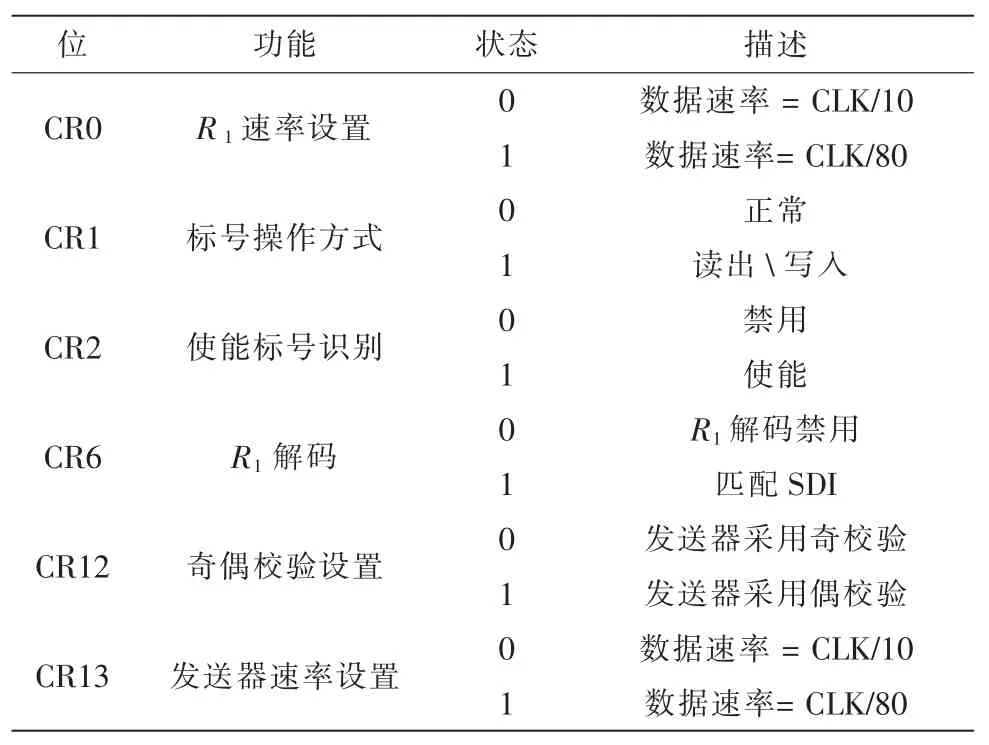

HI3584芯片拥有一个16位控制寄存器和一个9位状态寄存器。表1为该芯片控制寄存器的位、功能、状态和描述,这里只列出了寄存器的部分信息。控制寄存器的功能主要是对芯片的发送器和接收器进行设置,例如发送和接收的速率,奇偶校验位的设置和标号(Label)的操作方式。

表1 HI3584控制寄存器

状态寄存器主要描述HI3584芯片中发送器和接收器的FIFO状态,共9位,分别对应SR0-SR8。其中SR0为表示R1的FIFO状态是否为空,SR1表示R1的FIFO状态是否半满,SR2表示R1的FIFO状态是否全满。SR3表示R2的FIFO状态是否为空,SR4表示R2的FIFO状态是否为半满,SR5表示R2的FIFO状态是否全满。SR6表示发送器的FIFO状态是否为空,SR7表示发送器的FIFO状态是否为半满,SR8表示发送器的FIFO状态是否全满。FIFO状态为驱动程何时发数何时收数提供了依据,发送器的FIFO状态为全满时,驱动程序的发送函数则需要等待,直到发送器状态不为全满,否则发送将会丢数。数据接收可采用轮询和中断两种方式,例如采用轮询方式,驱动程序的接收函数必须不停的读取接收器的FIFO状态,FIFO状态不为空取出FIFO中的数据。

3 软件设计

3.1接口设计

一款优秀的软件具备通用性好,调用简单,易于理解,可重用性高等特点,因此在进行驱动设计的时候需充分分析上层应用程序的需求,并深入理解芯片自身特点和协议的标准。

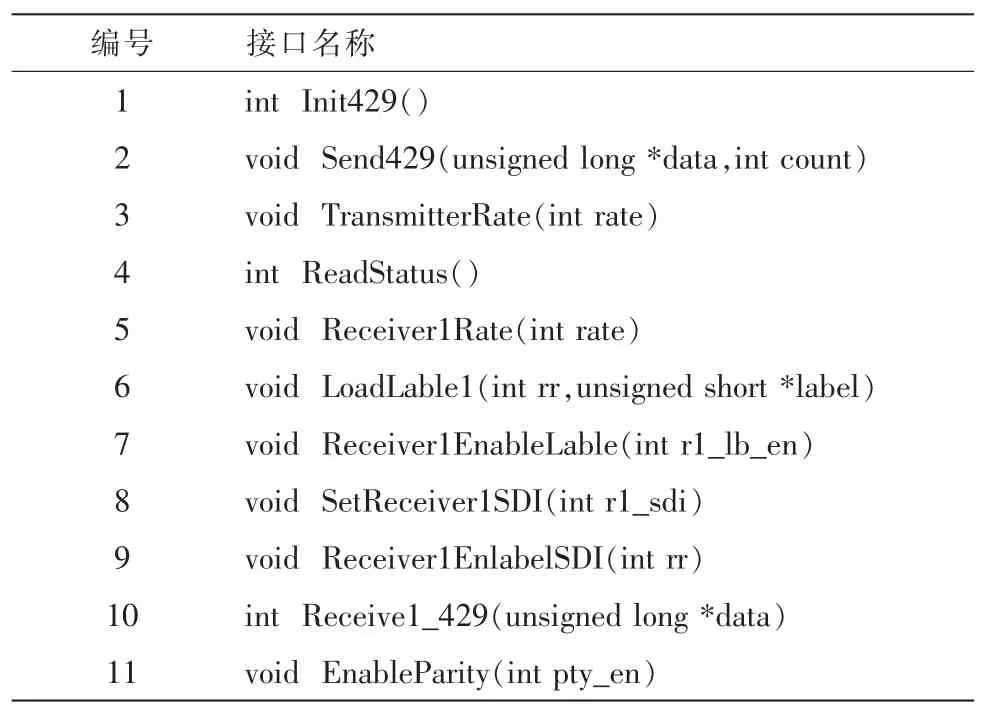

表2是根据429总线协议和芯片功能设计出的驱动接口。下面将描述接口的功能和使用。1号接口用于初始化总线芯片。2号接口用于数据发送,参数data为发送数据的值,参数count发送数据的个数。3号接口用于发送器速率设置,参数rate为1代表高速,0代表低速。4号接口用于读取状态寄存器,判断FIFO中是否有数据。5号功能用于接收器1速率设置,参数rate为1代表高速,0代表低速。6号功能为设置标号(Label),第一个参数 rr取值 0、1、2,分别代表“正常操作”、“读标号”、“写标号”,第二个参数为标号的值。7号接口用于设置接收器1标号匹配使能。8号接口用于设置CR7和CR8。9号接口用于设置CR7,CR8使能。10号接口用于接收器1接收数据。11号接口用于设置奇偶校验使能。

表2未列出接收器2驱动接口,接收器2的接口设计可参考接收器1的接口设计,具体参照5~10号接口。

表2 429总线驱动通用接口

3.2初始化

芯片初始化需实现Init429接口,至少需要完成以下几项设置:1)接收器速率设置;2)接收器SDI值设置;3)使能检验位;4)接收器滤波设置;5)接收器标号设置;6)发送器速率设置;7)设置数据发送顺序。

在实现Init429接口的时候,根据实际需求调用5-11号接口完成相关设置,5-11号接口提供了芯片的各项设置,参照表1中HI3584控制寄存器,向对应的CR位中写入需要的值便可实现5-11号接口。例如实现5号接口Receiver1Rate,由表1可知,R1速率设置位为CR0,因此在实现Receiver1-Rate接口是只需根据参数rate传进来的值改变控制寄存器的CR0位,控制寄存器其余位值不变。

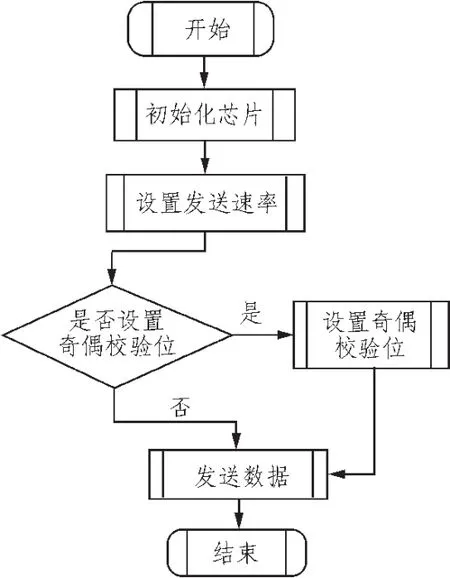

3.3数据发送

数据发送需实现2号接口Send429。实现时,向FPGA为总线芯片分配的发送寄存器中写入需发送的数据,若有多条数据需要发送,则多次循环写入。图2为系统429数据发送流程。

3.4数据接收

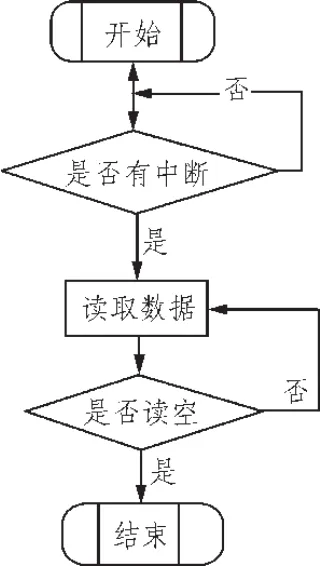

数据接收通常可采用中断方式和轮询方式。轮询方式不需要硬件支持,代码易读性高,便于追踪调试,但会增加系统负荷,严重降低系统性能[5-6]。中断方式需硬件支持,能大大提高处理器的利用率。本驱动中采用中断方式,中断由FPGA给DSP触发,触发条件为接收FIFO状态为半满。数据接收需实现接口Receive1_429。实现时,将FPGA为总线芯片分配的数据接收寄存器中的值读取出来,存放于用户指定的缓存区。在此过程中调用ReadStatus接口,反复读取状态寄存器,判断接收FIFO的数据是否读空。接收数据流程如图3所示。

图2 数据发送流程

图3 中断接收流程

3.5驱动测试

ARINC429总线驱动程序的测试方法为自发自收。HI3584芯片具有一个发送器和两个接收器(A和B),在测试时将发送器和接收器之一相连接,本测试采用接收器A。上位主机开发环境采用TI公司CCS5.0,集成编码和在线调试功能。调试时上位主机和DSP通过JTAG仿真器连接,本测试仿真器型号为SEED-XDS560v2。

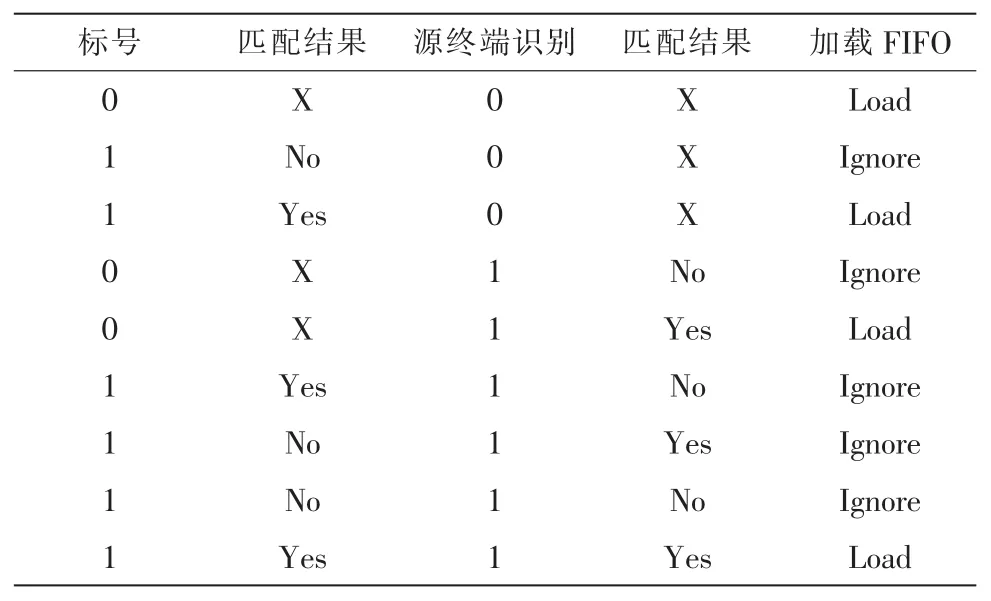

ARINC429总线协议芯片HI3584的接收器会根据控制寄存器的设置对收到的数据进行过滤。若接收的数据与设置的不相符,接收器则会丢掉;若满足要求,则将数据加载到接收器的FIFO当中。表3为FIFO加载判定,共9种组合。第一列表示是否使能标号匹配,0表示不使能,1表示使能;第二列表示标号匹配结果,X表示任意结果,No表示不匹配,Yes表示匹配;第三列表示是否使能源终端识别(SDI)匹配,0表示不使能,1表示使能;第四列表示源终端识别匹配结果;第五列表示接收的数据是否加载进入FIFO,Load表示加载数据到FIFO,Ignore表示忽略数据。第5列判断依据来自于第二列和第四列的结果,其规则为逻辑与,其中X可看作Yes。

使用 LoadLable1函数设置是否加载标号, 使用SetReceiver1SDI设置SDI值,并使用Receiver1EnlabelSDI函数设置SDI使能,通过Send429函数发送表3中9种组合数据,使用ReadStatus函数判断接收状态,并结合表3对比,判断程序是否正确。笔者将发送数据预设为表3的9种组合,经测试,完全符合表3的预期结果。

表3 FIFO加载判定

除测试表3中的组合项,还需使用TransmitterRate和Receiver1Rate函数测试发送速率和接收速率,以及使用EnableParity函数测试奇偶校验位,笔者都进行了长时间的测试,完全符合预期结果。

4 结 论

文中设计出的ARINC429总线驱动程序解决了计算机控制模块与其他ARINC429设备之间数据通信问题,并且具有良好的可移植性。经大量实验证明,驱动程序稳定可靠,能够满足上层应用程序的普遍需求。

[1]李榕,刘卫国,刘晓剑.航空用ARINC429总线收发系统设计与实现[J].计算机测量与控制,2005,13(9):970-972.

[2]Gujarati A,Cerqueira F,Brandenburg B B.Multiprocessor real-time scheduling with arbitrary processor affinities:from practice to theory[J].Real-Time Systems,2015(51):440-483.

[3]张杨.VxWorks内核、设备驱动与BSP开发详解[M].北京:人民邮电出版社,2011.

[4]于海彬,王斌,陈兴林,等.基于Linux的SC16IS752的串口驱动程序设计[J].自动化与仪表,2013(28):36-41.

[5]周爱武.计算机操作系统教程[M].北京:清华大学出版社,2006.

[6]任哲.嵌入式实时操作系统μC/OS-Ⅱ原理及应用 [M].北京:北京航空航天大学出版社,2014.

Design of the ARINC429 bus driver based on DSP p latform

ZHOU Jia-yi,GUAN Qin,XU Bi-hui

(No.58 Research Institute of China Ordnance Industries,Mianyang 621000,China)

Aiming at the critical problem of data communication between DSP and other ARINC429 devices,we designed a setof ARINIC 429 bus driver.Analyzed the chip HI3584 which implements the protocol of ARINIC 429 bus,we designed a universal driver interface combining with this scheme,and gives realization of program.The result shows that the driver is stable and reliable.In the later project,the driver can be used directlywith littlemodification.

ARINC429 bus;DSP;driver design;HI3584

TN914

A

1674-6236(2016)19-0171-03

2015-09-30稿件编号:201509193

周加谊(1990—),男,重庆人,助理工程师。研究方向:嵌入式软件。