0.18 μm完全隔离型低导通态电阻(Low Ron)NLDMOS研究

2016-09-13冯喆韻马千成中芯国际集成电路制造有限公司上海201203

冯喆韻,马千成,汪 铭(中芯国际集成电路制造有限公司,上海 201203)

0.18 μm完全隔离型低导通态电阻(Low Ron)NLDMOS研究

冯喆韻,马千成,汪铭

(中芯国际集成电路制造有限公司,上海 201203)

介绍一组基于0.18 μm逻辑平台构建的低导通态电阻(Low Ron)NLDMOS。该组LDMOS涵盖10~30 V应用电压。该NLDMOS为完全隔离型,因而其源端和漏端均可以独立于衬底加偏压。针对Drift区域和Body区域分别进行结构优化,最终得到性能良好的低导通态电阻(Low Ron)NLDMOS。其导通态电阻(Ron)为4.4 mΩ·mm-2对应击穿电压(BV)~20 V,21 mΩ·mm-2对应击穿电压(BV)~41 V。

LDMOS;低导通态电阻;完全隔离型

1 引言

功率集成电路(Power IC)是指将功率器件、控制电路、信号处理和通信接口电路等集成在同一芯片中的特殊集成电路。随着技术的不断发展,功率集成电路处理电流能力越来越强,系统集成度也越来越高,目前已被广泛应用于通信与网络、计算机与消费电子、工业与汽车电子等诸多领域。

近年来,功率集成电路应用对于降低成本、缩小面积和提高集成度方面的需求越来越高[1,2]。因而不断降低LDMOS的导通态电阻(Ron)是我们努力的一个主要方向。我们都知道LDMOS的击穿电压(BV)和导通态电阻(Ron)之间有着很强的制约关系,单纯地通过物理尺寸的变化得到低导通态电阻(Ron)的同时击穿电压(BV)也会随之减小。同理,提高击穿电压(BV)的同时导通态电阻(Ron)也会随之增大[3,4]。所以很多人都致力于用各种方法来突破击穿电压(BV)和导通态电阻(Ron)的极限关系[5]。

本文所述0.18 μm BCD平台与0.18 μm逻辑平台兼容,可同时提供应用电压为10~30 V的高压器件,平台中的NLDMOS为完全隔离(fully isolated)型。该平台针对LDMOS进行优化,在同等击穿电压(BV)下得到更低的导通态电阻(Ron)。

2 平台简述及器件结构

本文介绍的0.18 μm BCD平台是基于0.18 μm逻辑标准工艺搭建的,其低压部分与0.18 μm CMOS平台相兼容,高压部分提供10~30 V完全隔离型低导通态电阻(Low Ron)NLDMOS。完全隔离型NLDMOS 的Drain端和N-epi之间是隔离的,Drain端相对于N-epi可独立加压,其相对于衬底甚至可为负偏压。这种结构对于来自Drain端的瞬间电流可以很好地隔绝,也能很好地隔绝来自衬底的噪音,因而更适用于大电流及高频开关的器件应用,如移动电源控制。其基本结构如图1所示,器件的Drain端和N-epi之间有Deep P-Well作隔离。低导通态电阻(Low Ron)NLDMOS(图1(b))相比于普通NLDMOS(图1(a))在Drift区和Body区都有所不同。

图1 完全隔离型NLDMOS结构图

本平台中采用的N-epi深度为7 μm,针对高压部分比逻辑标准工艺增加P-Body、N-Drift、Deep P-Well制程。P-Body层是用来调整低导通态电阻(Low Ron)NLDMOS的阈值电压(Vt)的,为了实现较低的导通态电阻(Low Ron)该层深度较浅,所以需要P-Well作引出。在低导通态电阻(Low Ron)NLDMOS的Drift区中,不仅有N-Drift还有N-Well。N-Well与N-Drift在横向与纵向上都形成较好的N型梯度,有利于降低导通态电阻(Ron)。本平台在高性能的同时也兼顾低成本。这里的N-Well是原本逻辑制程里的N-Well,因而不需要额外增加光罩或制程。

3 数据和分析

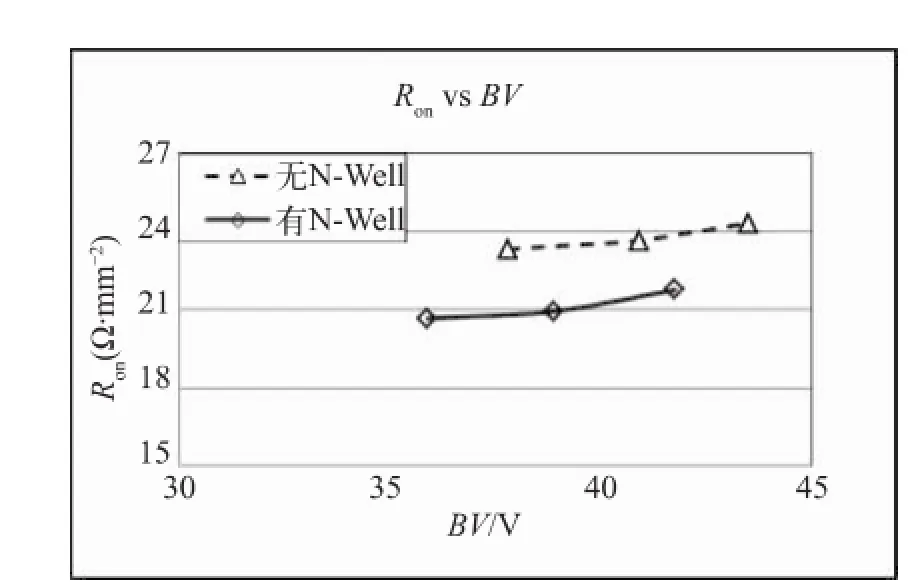

在低导通态电阻NLDMOS的Drift区域,我们采用层进的结构。在N-Drift里增加了一个浓度和深度介于N-Drift和Drain端N+之间的N型的层,N-Well。这里的N-Well是原本逻辑制程里的N-Well,因而不需要额外增加光罩或制程。这样Drift区在横向与纵向都能形成较好的N型梯度。图2为无N-Well结构(图2(a))和有N-Well结构(图2(b))的浓度分布图,可以看到有N-Well的结构浓度分布更均匀。图3、图4为当LDMOS处于BV发生点时无N-Well结构和有N-Well结构的电势分布图和碰撞离化图。可见,有N-Well结构虽然在Drift底部出现一个新的碰撞离化点,但是原先在STI角落处的碰撞离化点得到优化。同时,由于Drift区的整体浓度有所提高,使导通态电阻(Ron)降低。图5为有/无N-Well结构的导通态电阻(Ron)对应击穿电压(BV)图,图中不同的点代表不同的N-Drift尺寸。可以看到,在击穿电压(BV)相同的情况下,有N-Well结构导通态电阻(Ron)要小10%以上。当然,N-Well的尺寸也是需要优化的。N-Well的尺寸增加固然对降低导通态电阻(Ron)有利,但是过大的N-Well也会使击穿电压(BV)急剧下降。图6为不同N-Well尺寸下导通态电阻(Ron)对应击穿电压(BV)图,其中DF2为N-Well与STI交叠部分尺寸。

在低导通态电阻NLDMOS的Body区域,我们设计的P-Body浓度较高,这样可以形成一个很短的沟道且不易发生短沟道效应。优化后器件的线性区电流(Idlin)有所提升,即意味着导通态电阻(Ron)降低。同时由于尺寸的减小,导通态电阻(Ron)将进一步降低。图7为有/无P-Body的导通态电阻(Ron)对应击穿电压(BV)图,图中不同的点代表的是不同操作电压的器件,有/ 无P-Body这两组器件的尺寸和制程条件都各自进行了优化。当然,P-Body的引入使得器件的阈值电压(Vt)也比较高,这组器件相比无P-Body器件的阈值电压(Vt)要高约0.5 V。

图2 Drift区域有/无N-Well结构NLDMOS浓度分布图

图3 Drift区域有/无N-Well结构NLDMOS电势分布图

图4 Drift区域有/无N-Well结构NLDMOS碰撞离化图

图5 有/无N-Well结构的导通态电阻(Ron)对应击穿电压(BV)图

图6 不同N-Well尺寸下导通态电阻(Ron)对应击穿电压(BV)图(DF2为N-Well与STI交叠部分尺寸)

图7 有/无P-Body的导通态电阻(Ron)对应击穿电压(BV)图

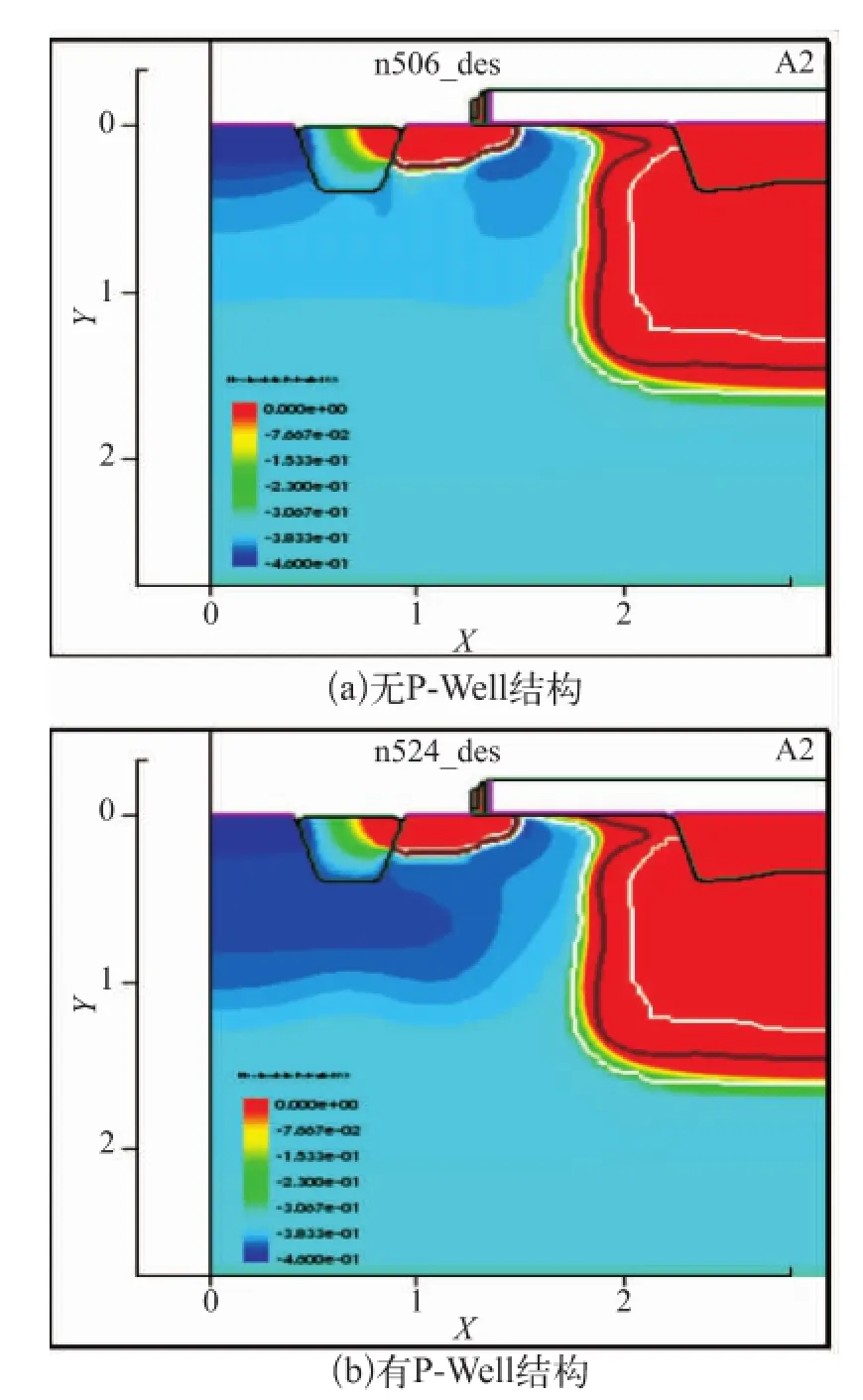

在Body区域有一个P-Well,其与P-Body部分重叠。这里的P-Well也是原本逻辑制程里用到的,因而不需要额外增加光罩或制程。为了使器件的阈值电压(Vt)仅受P-Body的控制,P-Well和栅极(Gate)并没有交叠。这个P-Well除了对P-Body做电性连接外,它还优化了电场分布。图8为有/无P-Well结构NLDMOS电势分布图。我们可以看到有P-Well结构的分布更均匀,这样有利于击穿电压(BV)的提高。此外,这个P-Well的增加局部提高了Deep P-Well的浓度,也有利于防止寄生NPN的开启。

图8 有/无P-Well结构NLDMOS电势分布图

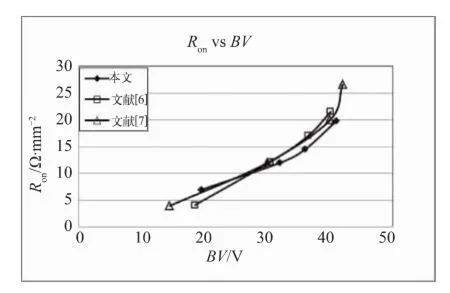

经过前文所述针对Drift和Body区域的分别优化,最终得到了一组特性良好的NLDMOS。图9描绘了本文所述低导通态电阻NLDMOS的击穿电压(BV)对应导通态电阻(Ron)的特性,并将其与其他BCD平台的击穿电压(BV)对应导通态电阻(Ron)特性相比较。如图可见,本组NLDMOS中器件的击穿电压(BV)为20 V时对应导通态电阻(Ron)低至4.4 mΩ·mm-2,器件的击穿电压(BV)为41 V时对应导通态电阻(Ron)低至21mΩ·mm-2,该特性与业界先进水平[6,7]可比。

4 结论

本文所介绍的0.18 μm BCD平台是基于0.18 μm逻辑制程而构建的,与0.18 μm逻辑平台兼容。同时提供应用电压范围为10~30 V的高压器件支持,其中NLDMOS为完全隔离(fully isolated)型。通过对LDMOS的优化,本平台的NLDMOS在同等击穿电压(BV)下可得到更低的导通态电阻(Ron)。其低导通态电阻NLDMOS的Ron可达4.4 mΩ·mm-2,对应击穿电压(BV)~20 V,21 mΩ·mm-2对应击穿电压(BV)~41 V,与业界先进水平可比。

图9 器件击穿电压(BV)及导通态电阻(Ron)特性对比其他平台

[1]R A Bianchi,F Monsieur,F Blanchet,C Raynaud,O Noblanc.High Voltage Devices Integration into Advanced CMOS Technologies[C].IEDM,2008:137-140.

[2]P L Hower.Current Status and Future Trends in Silicon Power Devices[C].IEDM,2006:89-92.

[3]B Jayant Baliga.Fundamentals of Power Semiconductor[M].北京:科学技术出版社,2008:16-21.

[4]Nakagawa A.Intelligent Power IC Technology-High voltage SOI power ICs[P].Toshiba Advanced SemiconductorDevices Research Lab,2003.

[5]Choul-Joo Ko,Sang-Yong Lee,II-Yong Park,Cho-Eung Park,Bon-Keun Jun,Yong-Jun Lee,Chan-Hee Kang,Jae-O Lee,Nam-Joo Kim,Kwang-Dong Yoo.Implementation of 85 V High Side LDMOS with n-layer in a 0.35 BCD Process [C].ISPSD,2008:103-106.

[6]Kwang-YoungKo,Il-YongPark,Yong-KeonChoi,Chul-JinYoon,Ju-HyoungMoon,Kyung-MinPark,Hyon-CholLim,Soon-YeolPark, Nam-JppKim,Kwang-Dong Yoo,Lou N Hutter.BD180LV-0.18 μm BCD Technology with Best-in-Class LDMOS from 7 V to 30 V [C].ISPSD,2010:71-74.

[7]Sameer Pendharkar,Robert Pan,Takehito Tamura,Bob Todd,Taylor Efland.7 to 30 V state-of art power device implantation in 0.25 μm LBC7 BiCMOS-DMOS process technology[C].ISPSD,2004:419-422.作者简介:

冯喆韻(1980—),女,祖籍广东,硕士研究生就读于上海大学物理系,现任职于中芯国际研发部,主要从事Power器件及制程的研发工作,拥有多年BCD研发经验。

Studies of 0.18 μm Fully Isolated Low RonNLDMOS

FENG Zheyun,MA Qiancheng,WANG Ming

(Semiconductor Manufacturing International Corporation,Shanghai 201203,China)

The paper presents a group of LowRonNLDMOS based on 0.18 μmlogic platformthat covers applied voltage ranging from10~30V. The fully isolated nature biases the source/drain electrodes with different voltages fromthe substrate potential. Structures of Drift side and Body side have been optimized to obtain well-performedLowRonNLDMOS of which Ronreaches 4.4mΩ·mm-2at 20V(BV)and 21mΩ·mm-2at41V(BV).

LDMOS;low Ron;fully isolated

TN432

A

1681-1070(2016)07-0039-05

2016-3-4