NAND Flash浮栅干法蚀刻工艺优化解决数据写入失效

2016-09-13周朝锋李晓波上海交通大学上海0040中芯国际上海集成电路股份有限公司上海01507

陈 亮,周朝锋,李晓波(1.上海交通大学,上海0040;.中芯国际(上海)集成电路股份有限公司,上海01507)

NAND Flash浮栅干法蚀刻工艺优化解决数据写入失效

陈亮1,2,周朝锋2,李晓波2

(1.上海交通大学,上海200240;2.中芯国际(上海)集成电路股份有限公司,上海201507)

随着移动终端的大量普及,存储器市场需求得到大幅度提升。NAND Flash以其大容量和体积小的优点,在目前的存储器市场占据着越来越重要的地位。产品良率是影响NAND Flash发展的一个重要因素。其中NAND Flash读写操作中的写入失效是良率损失最主要的原因。经分析,整合工艺的复杂性以及蚀刻制程工艺的局限性,浮栅和控制栅物理结构不完善会产生数据写入失效。着眼于对浮栅的干法蚀刻工艺进行改进,改善浮栅和控制栅物理结构,防止写入失效,从而得到最佳的良率。

NAND;Flash工艺制程;浮栅;控制栅;干法蚀刻;良率

1 引言

随着苹果的智能手机(iPhone)及智能移动终端(iPad)的成功,以及安卓(Android)的流行,智能移动终端迅速普及。它已经取代PC成为IT领域发展最快并且最大的市场。与CPU、显示器一起,存储器已成为智能终端的3个核心器件之一,占据着重要的战略地位。与此同时,IT市场一个重要趋势是固态硬盘(SSD)取代传统硬盘(HDD)。因此核心闪存存储(Flash Memory)技术是现在所有存储器中发展最快的核心技术。世界第一大存储器厂商韩国三星斥巨资300亿美元在西安建立最新一代NANDFlash生产线,生产64Gb及以上的高容量产品,即为抢占高容量SSD市场。

许多大厂如东芝、美光、海力士等,纷纷涉足NAND Flash晶圆制造领域,从512 Mb和1 Gb容量切入,锁定机顶盒、智能电视、用户端设备(CPE)、高阶网络设备、工业电脑(IPC)、工业设备系统、汽车应用等需要高容量NOR Flash芯片的领域,所以改善NAND Flash制造工艺制程的成熟度和提升产品的良率对国内存储行业的发展尤为重要。

NAND Flash的主要良率损失来自数据写入慢。经过前期数据分析,数据写入慢可能是由于字线(Word Line,WL)之间的短路或者位线(Bit Line,BL)有源区损伤等原因而造成。由于38 nm NAND Flash的线宽间距太小,而且浮栅和控制栅图形蚀刻结构非常复杂,蚀刻工艺一点点的不完善可能导致字线之间的短路。

本文基于38 nm NAND Flash工艺制程,通过优化浮栅和控制栅极的干法蚀刻制造工艺,解决由于数据写入慢造成的失效问题,提升产品良率。

2 实验对象和条件

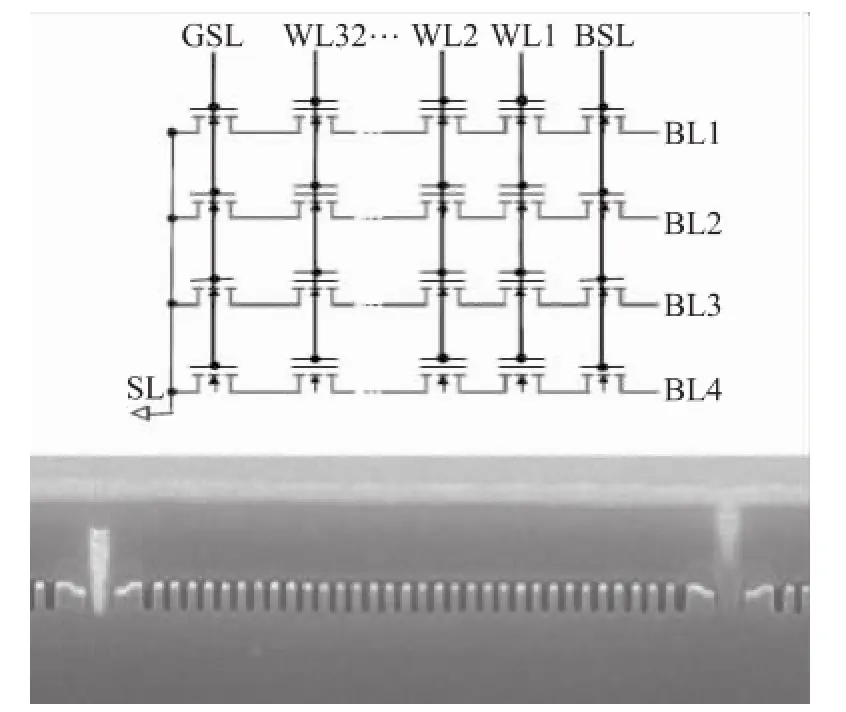

2.1NAND Flash结构以及测试顺序

NAND Flash的结构如图1所示,为竖向结构,图中所示 32位 NAND Flash由 32根 WL及两根Contact组成。由于contact没有直接连在存储单元格,其随机存储性能不是很快,但是其有效存储单元格的面积可以很小,从而使NAND Flash的Chip尺寸可以相对小一点,而且每个单元格的成本可以大大降低。

每个单元格是NAND Flash最基本的存储单元,其基于浮栅层技术,切面结构如图2所示。MOS管是由两个重合的栅极形成,底部栅极由氧化物包围而被隔离,上层栅极则由Contact连到外围电路。底部栅极由于是完全被隔离而被称为浮栅(Floating Gate,FG),非常适合电子存储而不丢失,这种状态可以保持很多年不会变化。上层栅极由于可以通过contact控制,而被称为控制栅(Control Gate,CG)。

图1 NAND Flash结构(Source:Forward Insights)

图2 FG记忆存储单元

NAND flash“写入”操作以WL为基本单位,每次一条WL加上写入电压(Vpgm),如图3所示。目标单元格的BL上接地,WL上的CG和BL之间会产生一个电场,电子通过栅极氧化层进入到FG当中,从而完成写入的过程[1]。

与目标单元格同一条BL上其他的单元格会加上一个通过电压(Vpass),从而使BL导通,但是Vpass还不至于使电场足够大而使电子吸入;同时,同一条WL相邻的单元格不希望被写入,BL因此会接VDD,这样电压差不够产生足够的电场而吸入电子,防止其被写入。

良率测试最典型的方法是将不同测试的图形对单元格矩阵进行写入,再通过读取判定写入是否成功。如果某一单元格写入不成功,认定这个单元格失效,当某一个Die失效单元格总数超过容许的数字(冗余使用数量)时,此Die认定为功能失效,从而会导致良率缺失。

2.2测试对象和条件

本实验所选用的对象是38 nm NAND Flash,测试以数据写入为研究重点,具体条件是一种称为Checkerboard的方法(第一行数据101010……,第二行数据01010101……),如图4所示。在Checkerboard的测试阵列测试后,芯片中间会有数据写入失效。

根据不同的蚀刻工艺条件,再通过测试各个条件下数据写入失效的比率,对结果进行分析。

图3 NAND Flash写入操作

图4 Checkerboard良率测试方法

2.3蚀刻工艺

NAND Flash浮栅和控制栅图形蚀刻的结构以及工艺流程如图5所示。蚀刻的结构是浮栅层由氧化硅/氮化硅/氧化硅三明治结构的介电层覆盖,再由控制栅所覆盖。蚀刻的最终要求是将子线的图形定义出来,子线间隔之间在有源区上无多晶硅的残留,以防止两条子线间的短路。

浮栅和控制栅图形蚀刻工艺流程主要分为三步:

(1)控制栅极和外围电路栅极图形的定义(如图5 (a)所示);

(2)控制栅极和外围电路栅极干法蚀刻(如图5 (b)所示),蚀刻停在浮栅上的介电层(氧化硅/氮化硅/氧化硅)上;

(3)浮栅干法蚀刻(如图5(c)所示),要求浮栅底部之间即字线之间不能有浮栅材质残余,字线有源区表面不能被损伤。

图5 蚀刻工艺流程

3 主要实验设计、结果和讨论

3.1NAND Flash控制栅极和浮栅的干法蚀刻工艺制程优化设计

根据干法蚀刻工艺的特点,在NAND Flash控制栅极和浮栅的干法蚀刻工艺制程优化实验设计中:

(1)把控制栅极和外围电路栅极干法蚀刻的蚀刻量减少,尽量不要损伤到介电层(氧化硅/氮化硅/氧化硅)。通过浮栅与浮栅之间控制栅极的蚀刻量来表征,如图6所示。减少的蚀刻量分成4组:A0(标准条件)、A1(减少一档)、A2(减少二档)、A3(减少三档)。

图6 控制栅极蚀刻量A

(2)由于在控制栅极的干法蚀刻中把蚀刻量减少,为预防蚀刻中浮栅材质的残留,要增加浮栅蚀刻的量,同时又要考虑到不能过蚀刻的情况,损伤到字线有源区表面。根据蚀刻量分成4组:B0(标准条件)、B1(减少一档)、B2(增加一档)、B3(增加二档)。

结合步骤(1)和(2),以A2和B2为中心,总共设计6组实验,分别为A0B0(校准组)、A1B2、A2B3、A2B2、A2B1、A3B2。

3.2实验结果

实验第一步中控制栅极的4个条件,通过物理分析,浮栅极和浮栅极之间控制栅极蚀刻量的数据如图7所示,A3<A2<A1<A0。其中A0为标准条件,图中H指浮栅极高度。

图7 不同条件控制栅极蚀刻量

对各个条件进行良率测试,根据测试数据分析的结果如图8所示,标准组的A0B0条件,芯片中间还是有数据写入失效问题,其他5组条件A1B2、A2B3、A2B2、A2B1和A3B2芯片中间都没有出现写入失效的问题,良率都很高,各个条件之间没有明显差异。由于良率没有区别,需要进一步分析平均冗余使用数量。

如前所示,各个die失效单元会有冗余替代,只要不超过上限此die还是有效的,可以计入良率好的die。所以有功能的die平均冗余使用数量越小,说明此芯片的质量越高。6个条件中,A2B2的冗余使用数量最小,而标准组条件A0B0则是最大的,如图8所示,相同的B2条件下,A1B2和A3B2的冗余使用量都比A2B2要高。图中所有条件良率都在1.5Y之上,平均冗余使用量大多在2X以下。

图8 良率和冗余使用数量结果

3.3结果讨论

3.3.1写入失效分析

A0B0有很严重的写入失效,造成良率缺失。通过对A0B0条件下芯片失效地址数据的电性分析,主要失效现象表现在:(1)在同一条位线上有连续几个存储单元数据写入失效;(2)远离栅极接触孔的存储单元越容易数据写入失效,反之越容易成功;(3)通过多次数据写入应力测试,连续几个存储单元数据写入失效会变成“十”字形的跨越式失效;(4)在控制栅极接触孔加1 V电压,芯片的底层接0 V,在失效存储单元位线上控制栅极接触孔电流强度为1.7 nA,而正常的存储单元位线上的电流强度小于pA级别。

由于控制栅极到底层有漏电流出现,通过物理失效分析数据写入失效单元,发现此单元下面的浮栅氧化层有击穿的现象。由于A1、A2、A3所有芯片都没有写入失效的问题,从图7已经知道,浮栅和浮栅之间的控制栅极蚀刻量A3<A2<A1<A0,间接反映了A0条件下控制栅极到浮栅之间的介电层(氧化硅/氮化硅/氧化硅三明治结构)在蚀刻的工艺制程中被损伤,介电层的耐压就会降低。在写入数据时,由于在控制栅极上会加入一个高电压(一般大于16 V),这会让控制栅极和浮栅短路,高电压直接加在浮栅上,把浮栅氧化层击穿,造成控制栅极和底层之间的漏电或者短路。这样这个存储单元数据写入就会失效。

3.3.2冗余使用数量分析

如上所述,标准组A0冗余用量最高,是由于控制栅极蚀刻量过多导致控制栅极和浮栅之间的介电层的损伤。此时将控制栅极蚀刻量减小到A1、A2以及A3,冗余量就有明显的改善。

通过对A1B2、A2B2和A3B2三组数据进行分析,A2条件的冗余量最少,A1的冗余量比A2高,可能是因为A1条件下,介电层还是有一点点损伤,而A3比A2也高,从物理结构上分析,可能是控制栅极蚀刻量过少,同样的浮栅蚀刻情况下,浮栅材质就可能会有残留,导致浮栅与浮栅之间的短路,从而使冗余使用量增加。

进一步分析A2B2、A2B1和A2B3三组条件的结果,其中浮栅蚀刻量是B1<B2<B3。由于B1条件下浮栅蚀刻量的减少,与控制栅极蚀刻量减少类似,浮栅与浮栅之间可能产生短路,所以B1的冗余量比B2高;此外,如果过多增加浮栅蚀刻量到B3,虽然浮栅与浮栅之间的短路可以完全解决,但是过多的蚀刻会使浮栅下面的有源区以及浮栅氧化层损伤,这样在数据写入时,高电压加在浮栅后会将浮栅氧化层击穿,造成写入失效。

结合以上的分析,为了获得最佳的芯片质量,控制栅极的蚀刻量和浮栅蚀刻量都应该精准地控制,最佳的蚀刻条件应该选择在A2B2。

4 结论

通过控制栅极和浮栅的干法蚀刻工艺制程的优化,减少控制栅极的蚀刻量,降低控制栅极与浮栅之间介电层的损伤,可以解决芯片中间NAND Flash的数据写入失效问题,从而提高产品良率。

[1]Rino Micheloni,Luca Crippa,Alessia Marelli.Inside NAND Flash[M].Springer Dordrecht Heidelberg London New York:4-25.

NAND Flash Floating Gate Dry Etch Technology Optimization to Tackle Program Failure

CHEN Liang1,2,ZHOU Chaofeng2,LI Xiaobo2(1.Shanghai Jiaotong University,Shanghai 200240,China;2.SMIC,Shanghai 201507,China)

The memory demands have sharply increased due to the rapid development of smart devices. NAND Flash featuring large storage capacity and small volume has been playing an increasingly important role in memory market.However,yield is a key factor affecting NAND Flash development.During NAND flash operation,"Program"is the major reason causing yield loss.Analysis shows that imperfect Floating and Control Gate structure may lead to Program fail as a result of the limitation of Dry ETCH technology.The paper proposes an optimization method of Floating Gate Dry Etch technology to obtain better yield.

NAND;Flash technology;floating gate;control gate;dry ET;yield

TN405.98

A

1681-1070(2016)07-0044-04

2016-3-16

陈亮(1984—),男,安徽人,学士,研发工程师,毕业于同济大学,现就职于中芯国际集成电路制造有限公司,主要从事NAND Flash整合工艺开发。