一种高速LVDS接收电路的设计

2016-09-13胡庆成贺凌炜周晓彬中国电子科技集团公司第58研究所江苏无锡214035

胡庆成,贺凌炜,周晓彬(中国电子科技集团公司第58研究所,江苏无锡214035)

一种高速LVDS接收电路的设计

胡庆成,贺凌炜,周晓彬

(中国电子科技集团公司第58研究所,江苏无锡214035)

提出了一种内置失效保护功能的高速低压差分信号(Low Voltage Differential Signaling,LVDS)接收电路。该电路不仅解决了传统电路结构在电源电压3 V或更低时不能满足LVDS标准规定的输入共模电压范围内(0.05~2.35 V)稳定工作的问题,而且还可以直接作为LVDS接口电路的输入级使用,节省了外接保护电路。基于SMIC 0.18 μm CMOS工艺模型库,用spectre进行仿真,在输入共模电压范围内工作稳定,传输速率达到1 Gbps。

LVDS;接收电路;失效保护;共模电压

1 引言

LVDS是一种低摆幅的差分信号,具有传输速度快、低功耗以及低噪声等优点,是一种通用的接口标准。它广泛应用于体积小、功耗低的便携式设备和高速通讯设备中[1]。图1是典型的点到点LVDS系统。

它由驱动电路(driver)、连接线(interconnect)、接收电路(receiver)和端接阻抗(100 Ω)组成。data信号通过驱动电路生成LVDS差分信号VO+和VO-,然后经过连接线传输,最后在端接阻抗两端形成接收电路的输入信号VI+和VI-。接收电路会根据VI+和VI-的大小判别出所传输数据是“0”还是“1”,并将其转换成相应的内部逻辑电平。

由于驱动电路和接收电路的参考地存在电势差,为了保证信号传输的可靠性,LVDS标准[2]规定,接收电路必须在0.05~2.35 V的输入共模电压范围内稳定工作。但是,当电源电压降低至3 V或更低时,传统的LVDS接收电路结构就很难满足这个指标。而且,LVDS接口电路是可以并联使用的,既可以同时工作,也可以部分工作。当部分工作时,未使用的接收电路就没有输入信号。为了避免非正常工作,就需要用到失效保护电路。通常都是采用外接的方法来实现,不仅增加了外围电路的复杂性和成本,还会对正常工作时的输入信号产生影响。本文设计了一种互补并行结构的高速LVDS接收电路,且内置了失效保护功能,可以保证在标准规定的输入共模电压范围内正常工作,还可以节省外部元器件,降低成本,提高电路可靠性。

图1 典型的点到点LVDS系统

2 接收电路设计

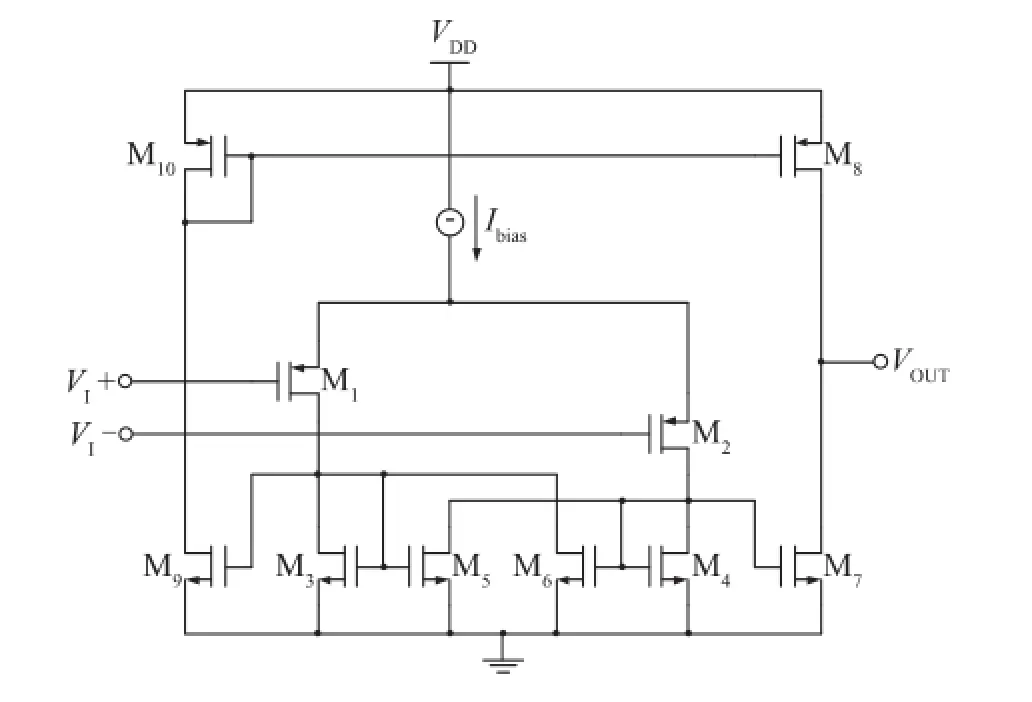

图2 典型的LVDS接收电路

图2是典型的LVDS接收电路结构[3]。M1~M6组成施密特型差分放大器,检测到差分输入信号VI+和VI-后,经二级放大,由M7~M8构成的反相器输出CMOS电平。当差分信号的输入共模电压保持在一个合适的范围内,接收电路就可以稳定地输出结果。但是,要达到LVDS标准要求的0.05~2.35 V输入共模电压范围,就存在一些问题。

电源电压降低到3 V或更低时,如果没有采用低阈值的器件,在输入共模电压低于0.1 V时,M1和M2就会进入线性区工作,导致放大器的增益下降,那么第一级放大器的输出就没有足够的能力来驱动第二级反相器,VOUT输出幅度就会降低甚至出错。另外,增益的下降还会加大放大器的传输延迟,降低传输速率。

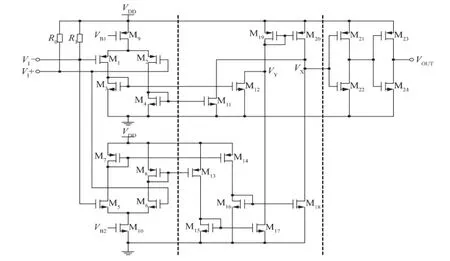

图3是本文设计的接收电路结构,可以在不用低阈值器件的基础上仍然满足LVDS标准规定的输入共模电压范围。

接收电路的第一级由两个互补并行的CMOS差分放大器构成。M1~M4组成PMOS差分对,M5~M8组成NMOS差分对,M9和M10分别为差分放大器提供直流工作点。无论哪个差分对由于输入共模电压的变化而偏离正常的工作区域,其互补的差分对仍然可以稳定工作,因此电路就可以拓宽输入共模电压的范围。在PMOS差分对中,PMOS管M1和M2组成差分输入管,NMOS管M3和M4以二极管连接的方式作为负载。在直流工作点不变的情况下,放大器的增益和带宽只与输入管及负载管的宽长比有关[4]。同理NMOS差分对的增益和带宽也只与M5~M8的宽长比有关。

接收电路的第二级采用镜像电流源结构,由M11~M20组成。M13~M16实现PMOS电流源向NMOS电流源的转换。M11、M12、M17和M18分别镜像M4、M3、M8和M7的电流,并选取合适的增益进行电流放大。M19和M20组成镜像电流源负载,并实现双端变单端的输出转换。M21~M24为两个反相器,构成缓冲级,输出CMOS电平。

图3 本文设计的LVDS接收电路结构

3 内置失效保护功能

如图2所示的接收电路,当差分输入没有信号的情况下,整个电路的工作就很不稳定。如果要作为LVDS接口电路的输入级使用,就必须外接保护电路。而在本设计中,如图3所示,采用增加上拉电阻R0和R1以及增大M20宽长比的简单方法,就可以使VOUT在无信号输入的情况下输出恒定的高电平,实现保护功能。下面简要说明一下工作原理。

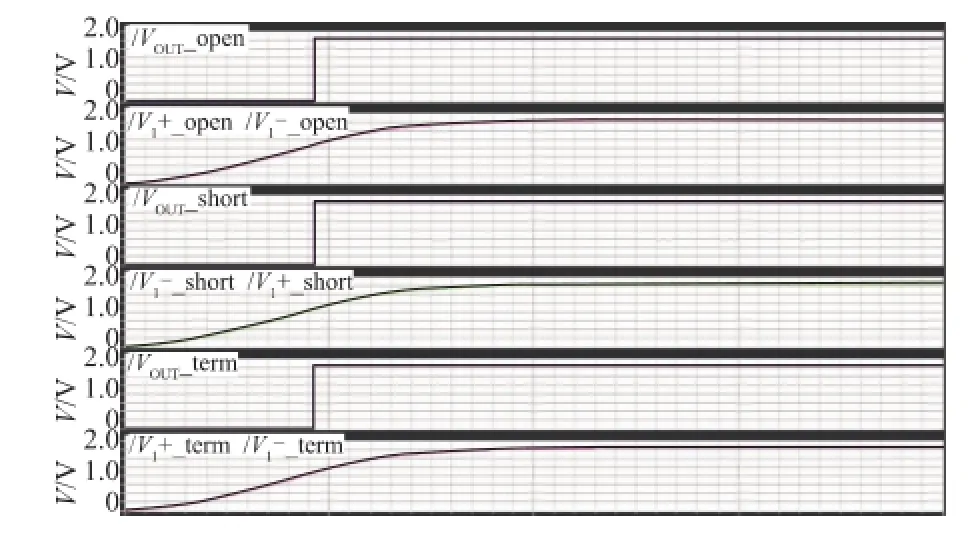

当接收电路输入端口VI+和VI-处于开路、短路或端接阻抗(100 Ω)三种故障状态时,由于上拉电阻的作用,两端口的电压值都等同于VDD,即差分放大器的输入共模电压为VDD,此时流过M19和M20的电流是一样的。但是,由于增大了M20的宽长比,增强了导通能力,其相应的VDS电压降减小,抬升了节点VX的电压值,就可以使输出VOUT保持高电平。图4是输入端口在开路、短路和端接阻抗三种情况下的仿真波形。

图4 三种故障模式下的失效保护功能仿真波形

4 仿真结果与分析

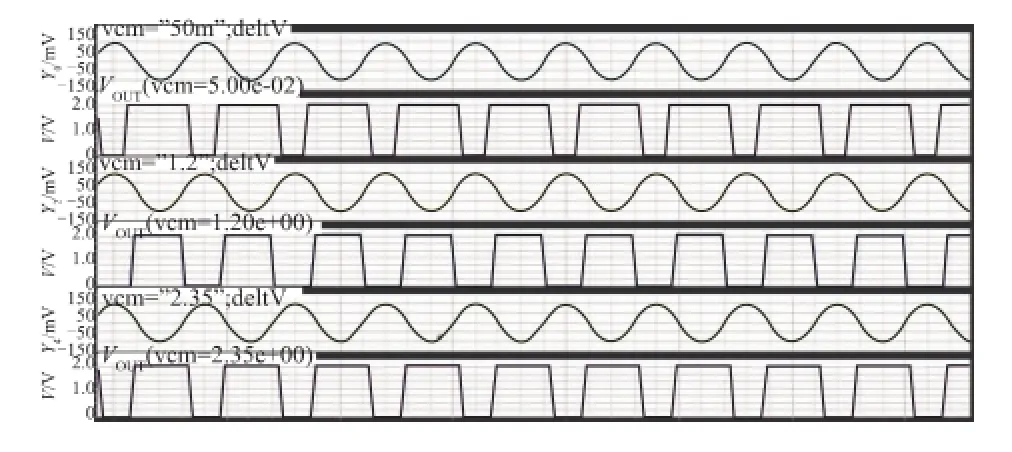

采用SMIC 0.18 μm CMOS工艺模型库进行spectre仿真。考虑到ESD保护结构以及封装对电路的影响,在仿真中加入了寄生参数。图5为电路仿真模型图,ESD寄生电容选为2 pF,封装的寄生参数选为2 nH和5 pF[5]。

图5 电路仿真模型图

图6为电路仿真波形。差分信号的输入频率为500 MHz,差模电压为±100 mV;输入共模电压选取了三个典型值,分别为0.05 V、1.20 V和2.35 V。结果显示,电路可以稳定工作在1 Gbps的传输速率下。

图6 电路仿真波形图

5 结束语

本文设计了一种内置失效保护功能的高速LVDS接收电路,其中互补并行的差分输入结构展宽了共模电压输入范围,达到LVDS标准规定的要求;而且还可以节省外接的保护电路,降低成本、提高可靠性。在SMIC 0.18 μm CMOS工艺模型上,电路传输速率可达1 Gbps,可直接应用于高速传输的接收电路中。

[1]蔡敏,王谧.LVDS接收器的失效保护电路设计[J].半导体技术,2005,30(4):61-64.

[2]TIA/EIA-644-A.Electrical Characteristics of Low Voltage Differential Signaling(LVDS)Interface Circuits[S].2001.

[3]Andrea Boni.LVDS I/O interface for Gb/s-per-pin operation in 0.35 μm CMOS[J].IEEE Journal of Solid-State Circuits,2001,36(4).

[4][美]毕查德·拉扎维.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2003.

[5]丁艳玲.一款低功耗的高速CMOS LVDS信号接收器[J].电子技术应用,2015,41(3):55-57.

Design of a High-Speed LVDS Receiver

HU Qingcheng,HE Lingwei,ZHOU Xiaobin

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214035,China)

The paper proposes a high-speed LVDS receiverembedded with failure-safe function,which ensures stable operation at 3 V or lower power supply when input common-mode voltage requirement(0.05 V to 2.35 V)may not be met and eliminates the protective circuit.During the Spectre simulation based on the model library of SMIC 0.18 μm CMOS technology,the circuit works stably in input common-mode voltage range and achieves a transmission rate up to 1 Gbps.

LVDS;receiver;fail-safe;common mode voltage

TN402

A

1681-1070(2016)07-0026-03

2016-3-25

胡庆成(1976—),男,江苏无锡人,本科,工程师,主要从事集成电路设计工作;

贺凌炜(1991—),男,江苏无锡人,本科,助理工程师,主要从事模拟集成电路设计工作。