一种嵌入式NOR Flash控制器IP的设计

2016-09-13解同同李天阳江南大学物联网工程学院江苏无锡4中国电子科技集团公司第58研究所江苏无锡4035

解同同,李天阳(.江南大学物联网工程学院,江苏无锡4;.中国电子科技集团公司第58研究所,江苏无锡4035)

一种嵌入式NOR Flash控制器IP的设计

解同同1,李天阳2

(1.江南大学物联网工程学院,江苏无锡214122;2.中国电子科技集团公司第58研究所,江苏无锡214035)

当前,嵌入式Flash广泛应用于嵌入式系统领域,便于系统进行软件在线更新和系统维护。嵌入式NOR Flash可以"嵌入"在芯片中作为高速缓存,对于提升芯片整体性能作用明显。传统的嵌入式NOR Flash不具备测试接口,在芯片出现工作异常时不便于对整个芯片进行故障诊断。设计并实现了一种具有片上可测试功能的嵌入式NOR Flash控制器IP。控制器主要分为控制模块与测试模块两个部分,分别对两个模块进行分析设计。经过仿真验证,控制器可以实现对NOR Flash的正常操作与片外测试功能,达到了设计目标。

NOR Flash;IP核;存储器控制器;可测试性

1 引言

在嵌入式系统中,NOR Flash通常用于存放直接执行的代码。NOR Flash具有高可靠性、随机读取速度快和片内执行等优势,因而在嵌入式系统中得到广泛应用[1]。高性能嵌入式芯片中的寄存器、一级高速缓存和二级高速缓存使用的都是嵌入式存储器[2],嵌入式存储器的优劣对嵌入式系统的影响越来越大,因此设计一款专用的NORFlash存储器控制器具有重要意义。

许多NOR Flash在设计完成后,无法从片外对其进行测试,一旦嵌入式芯片出现工作异常的情况,很难对NOR Flash进行失效分析[3]。本文设计的NOR Flash控制器,除了具有保证存储器与内核正常连接的控制功能外,还具有测试接口,可以从片外对存储器进行测试,增强了NOR Flash的可测试性。

2 NOR Flash基本操作

本文的 NOR Flash IP选用 SFD16KX64M16 P8I20A,这是一款采用TSMC的0.18 μm工艺技术制造的CMOS页擦除双字可编程嵌入式存储器。其接口信号如表1所示。IFREN为高电平时选择信息块,低电平时选择存储块。SE置为高电平时可进行读操作。NVSTR置为高电平时可进行擦写操作。TMR、TM、VPP用于对Flash的测试。

表1 Flash IP接口信号

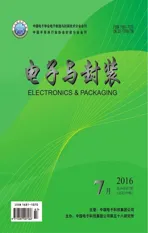

NOR Flash的读、写和擦除操作需要满足一定的时序要求。写操作时序如图1所示。首先将PROG置为1,满足NVSTR的建立时间后将NVSTR置为1,经过编程建立时间,信号稳定后进行写操作。写操作时,XE、YE置为1。写操作结束时,信号PROG在编程保持时间后置为0,在满足NVSTR的保持时间后将NVSTR置0。

读操作时序如图2所示。读取数据时需将XE、YE、SE置1,等待行地址获取时间Txa和列地址获取时间Tya后读取数据。

擦除操作时序如图3所示。先将XE、ERASE置为1,满足NVSTR的建立时间后将NVSTR置为1。擦除结束时,将ERASE置为0,满足NVSTR的保持时间后将NVSTR置为0。

3 设计方案

3.1总体设计

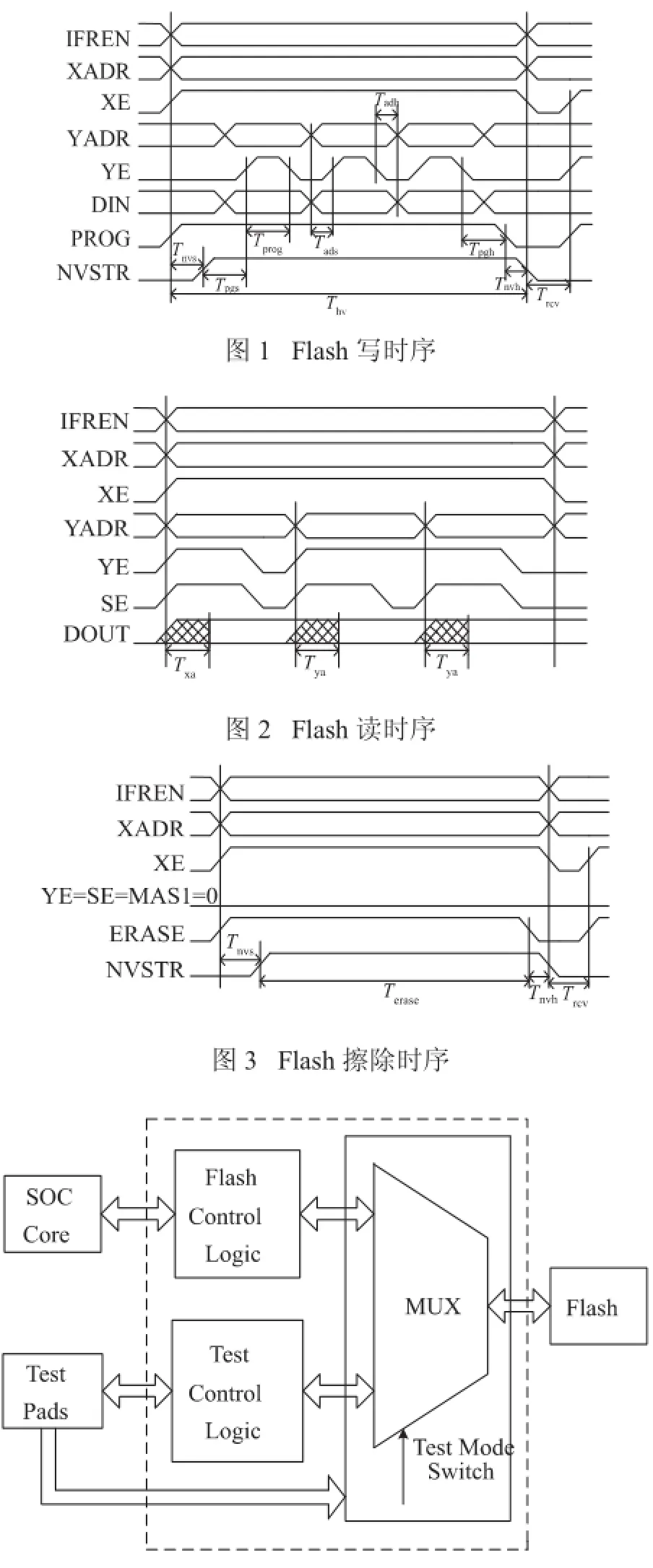

如图4所示,NOR Flash控制器主要包括控制模块和测试模块两部分,分别对应正常模式和测试模式两种工作模式。它们通过选通模块与NOR Flash相连接,正常模式下,内核通过控制模块实现对NOR Flash的操作。需要片外对NOR Flash进行访问时,通过Test Mode Switch切换到测试模式,能够通过Test Pads完成对NOR Flash的操作。在测试模式结束后,切换回正常模式,使NOR Flash回归正常工作。

图4 NOR Flash控制器结构框图

3.2控制电路设计

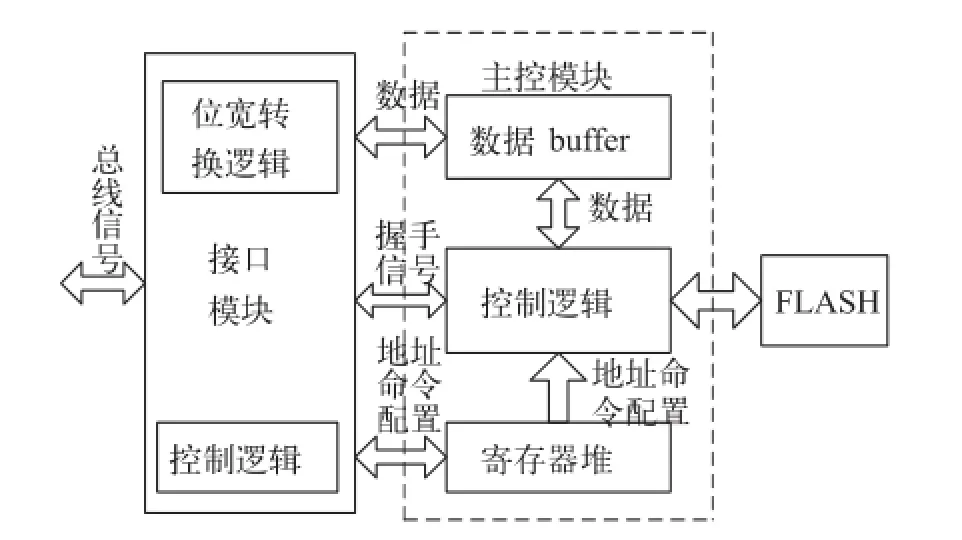

控制模块被设计成基于EBI(外部总线接口)的从设备模块,控制电路作为一个符合系统总线标准的从设备模块挂在系统总线上以供其他主设备访问[4]。其结构如图5所示,整个控制电路主要分为接口模块和主控模块两大部分。总线信号包括时钟、复位、读写控制、写数据总线、读数据总线、地址总线。其中数据总线的位宽为16位,地址总线的位宽为15位。

图5 控制电路的结构框图

接口模块负责将EBI总线上其他主设备发出的数据和控制信号进行处理,将其转换成主控模块可以识别的格式并发送给主控模块,同时对主控模块传达的数据信号进行处理,将其转换成与总线标准相符合的形式后发送给系统中的主设备。接口模块方便了总线上的其他主设备对NOR Flash控制电路进行访问。

主控模块是整个NOR Flash控制电路的核心部分,控制电路对NOR Flash的各种操作都是通过主控逻辑部分来实现的[5]。主控模块包括数据buffer、寄存器堆和控制逻辑三个部分,其中数据buffer用来缓存控制逻辑和位宽转换逻辑产生的数据,寄存器堆用于接口模块与主控模块之间地址命令配置信号的过渡,寄存地址、命令以及配置等信号。控制逻辑对各个寄存器中的数据进行读取处理,以产生输出到NOR Flash的控制信号。主控模块实现了总线上其他主设备对NOR Flash进行访问操作。

如表2所示,控制电路中状态/控制寄存器主要包括FLASH_CONFIG寄存器、ERASE_STARTUP寄存器、ERASE寄存器和FLASH_STATUS寄存器。FLASH_CONFIG寄存器用于配置FLASH的基本操作,包含写模块控制、时钟频率选择与读写保护;ERASE_STARTUP寄存器用于控制擦除操作的启动,FLASH在该寄存器被写入特定的数据后启动擦除操作,然后再根据ERASE寄存器中的内容来执行具体的擦除操作;ERASE寄存器用于选择擦除的模式和区域;FLASH_STATUS寄存器用来对FLASH的读取、编程、擦除和待机四种状态进行标志,单个操作完成后要等待FLASH处于待机状态后才能继续进行下一个操作。

表2 FLASH控制电路内部寄存器描述

3.3测试电路设计

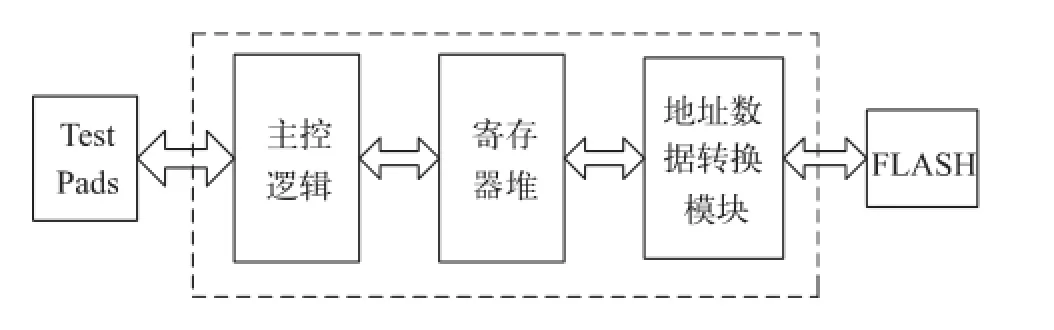

图6 测试电路结构框图

测试控制的具体结构如图6所示,测试电路由主控逻辑、寄存器堆和地址数据转换模块组成。主控逻辑作为整个测试电路的主控部分,主要功能是产生各种控制、地址与数据信号,实现测试端口对NOR Flash的控制,并将NOR Flash输出的数据通过测试Pads正确读取出来。3位SEL信号就是通过主控逻辑来对8位的地址/数据/控制复用总线进行控制。

寄存器堆的主要功能是对控制逻辑以及NOR Flash的数据、地址和控制信号进行缓存。设置Data-in Register、Address Register、Control Signal Register和Extra Test Register四个8位寄存器来缓存数据。

地址数据转换模块的主要功能是实现地址与数据线的位宽转换。测试端地址/数据/控制复用总线的位宽为8位。本设计采用的NORFlashIP的地址线为14位(行地址线10位、列地址线4位),数据线为64位[6]。NOR Flash进行片外操作所需信号由测试端的8位复用总线提供。所以该模块的作用就是将8位复用总线的地址和数据信号转换成与NOR Flash相匹配的位宽。

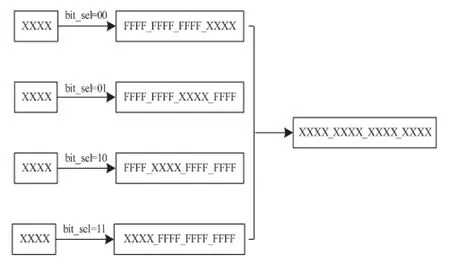

地址数据转换的原理是:8位复用总线进行两次地址输入组成一个16位地址信号(对应FLASH的10位行地址、4位列地址、2位数据选择信号)。由于Flash IP每次只允许对64位数据中的16位进行读写,所以一次完整的读写操作要对NOR Flash中的某一地址进行4次操作。数据转换设计实现如图7所示,当SEL[2:0]信号选择010和011时,8位复用总线分别输入Din[15:8]和Din[7:0],将两次8位输入数据组合成16位数据XXXX。写操作时,通过bit_sel[1:0]选择64位数据中的16位,其余48位置1得到64位数据写入,进行4次这样的操作以实现一次完整的写入。同样,读操作时也要进行4次操作,通过bit_sel[1:0]选择要读取的16位,最后分成两次通过8位复用总线读出。

图7 数据转换实现示意图

4 功能验证与时序仿真

本设计采用Verilog HDL实现,用Candence公司的NCsim进行仿真。

4.1内核对FLASH操作的仿真验证

Flash的写入操作是将存储单元相应位上的数据由“1”写为“0”,擦除操作是将“0”写为1。如图8所示,先通过寄存器配置,对NOR Flash进行擦除,擦除后读取00AA地址的数据,结果为FFFFFFFF,表示擦除操作实现。

图8 内核对Flash的擦除与读操作

系统数据总线位宽为32位,而NOR Flash存储器的位宽为64位,对NOR Flash中某一地址要进行写操作时,先写低32位,再写高32位。如图9所示,写操作时,将写模式设置为按字写入模式,向地址00AA依次写入FFFF1234与1234FFFF两个32位数据,输入给NOR Flash的DIN端口。读操作时,按字读出00AA地址对应的数据,依次读出的低32位和高32位分别为FFFF1234与1234FFFF,与写入数据相符,表示读写操作实现。

4.2FLASH测试电路仿真验证

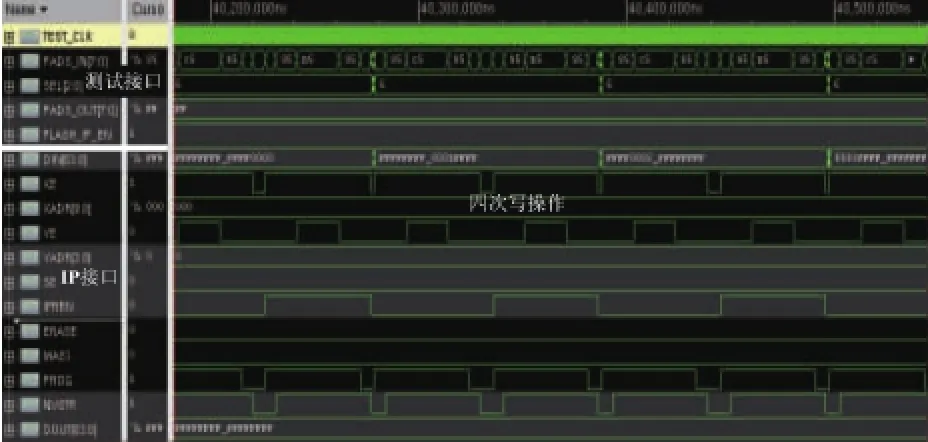

图 10为测试 Pads对 Flash的写操作,控制PADS_IN总线输入位选择信号,将4个16位数据(0000、0001、0002、0003)组成一个 64位数据写入NOR Flash的0000地址中。

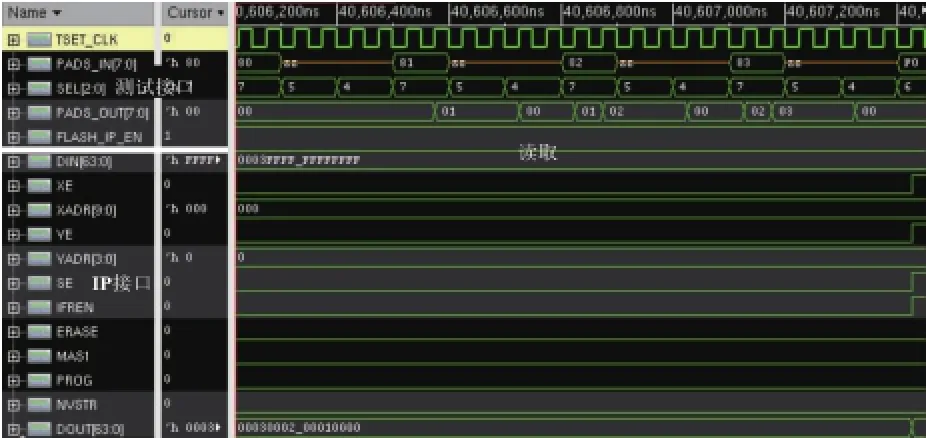

图11为测试Pads对Flash的读操作,先后对0000地址进行4次读操作,读出的64位数据为0003_0002_0001_0000,与写入的数据相符,表示测试电路的读写操作实现。

图9 内核对Flash的读写操作

图10 测试Pads对Flash的写操作

图11 测试Pads对Flash的读操作

5 结论

本文设计了一款基于嵌入式系统的NOR Flash存储器控制器IP,在常规嵌入式NOR Flash控制器设计的基础上增加了NOR Flash测试电路的设计,实现了对NOR Flash存储器的读写控制和片外可测试功能。通过仿真验证,控制逻辑实现了对NOR Flash的读写和擦除操作,满足时序要求。测试接口实现了片外对NOR Flash的直接存储操作,可用来进行独立的NOR Flash测试。

[1]Ashok K Sharma.先进半导体存储器——结构、设计与应用[M].曾莹,等译.北京:电子工业出版社,2005.1.

[2]潘立阳,朱钧.Flash存储器技术与发展[J].微电子学,2002,32(1):1-6.

[3]张钥,万培元,林平分.集成电路可测性设计IO复用方法[J].半导体技术,2011,36(9):705-709.

[4]王力纬.多端口存储器控制器IP核的设计与实现[J].武汉大学学报:理学版,2007(5):617-621.

[5]鲍胜荣,吴旭凡,钟锐.一款嵌入式芯片总线仲裁器的设计和评估[J].电子工程师,2005,31(1):19-22.

[6]高参,张永学.多模卫星导航芯片的可测性设计[J].微电子学,2012,42(6):778-781.

Design of an Embedded NOR Flash Controller IP

XIE Tongtong1,LI Tianyang2

(1.College of Internet of Thing,Jiangnan University,Wuxi 214122,China;2.China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214035,China)

At present,embedded Flash is widely used in embedded systems to facilitate system maintenance and online update.NOR Flash embedded in chips serves as a cache to enhance the overall performance of the chips.Lack of test interface in traditional embedded NOR Flashes may cause inconvenience in diagnosis upon failure.The paper designs and develops an on-chip testable embedded NOR Flash IP.The controller consists of two parts:control module and test module.The two modules are independently analyzed and designed.The simulation results show that the controller achieves normal operation and on-chip testable.

NOR Flash;IP core;memory controller;testability

TN402

A

1681-1070(2016)07-0018-04

2016-3-15

解同同(1988—),男,江苏徐州人,硕士研究生,研究方向为集成电路设计。