基于FPGA 的PCM解调器设计

2016-08-31李盘文蒋宏娜

李盘文 王 亮 蒋宏娜

基于FPGA 的PCM解调器设计

李盘文 王 亮 蒋宏娜

针对航空测试中常用的PCM数据流,提出一种双通道PCM解调器设计。系统以FPGA为控制器,实现两路PCM数据流的实时解析。PCM解码过程中进行,帧同步和位同步的检测,帧和位都同步则此帧数据有效。解析出一帧完整数据后通过USB发送给终端。

在航空测试领域,PCM作为数据传输和遥测的数据格式被广泛使用。信息接收端需要解调器,对PCM进行解调,以便进行数据处理和数据记录。FPGA具有结构灵活,设计周期短,可扩展性强,接口丰富等优点,在高速信号实时处理领域越来越重要。本文提出使用FPGA同时对两路输入的PCM 数据流进行解析,解析出一帧完整数据后放入FPGA内部RAM缓存,通过USB接口发送给外部设备。

硬件电路设计

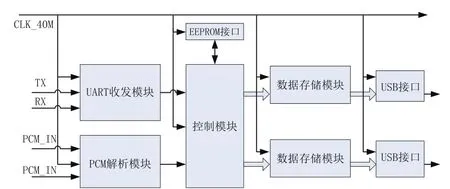

系统硬件由RS232电平转换芯片,RS422电平转换芯片,EEPROM芯片,USB驱动芯片和FPGA组成。上位机通过串口对系统进行配置,PCM数据流经过RS422电平转换芯片转换为TTL电平,FPGA将解析出的PCM数据通过USB芯片发送出去。

控制器FPGA

FPGA选用altera公司的 EP3C80F484I7,此FPGA自带多种接口的IP核,内部有2810880位的存储空间可以使用,可用IO 296个。此款芯片资源满足系统需求。

电平转换模块

上位机通过串口对系统进行配置,使用MAX232将电平转换为TTL电平供FPGA使用。PCM数据流为422电平,使用MAX3490将电平转换为TTL电平供FPGA使用。

存储器控制模块

存储器使用二线制I2C串行EEPROM AT24C02,此芯片有两种写入方式,一种是字节写,一种是页写,允许一个周期内同时对一个字节到一页的若干字节进行编程写入。

USB驱动模块

此模块使用FTDI公司的USB接口芯片FT245BM,此芯片支持USB协议与并行I/O协议之间的转换。使用时无需考虑固件设计以及驱动程序的编写,从而能大大缩短产品的开发周期。FT245BM支持USB2.0规范,数据传输速度可达12M bps。

软件设计

软件按模块进行设计。系统的运行由FPGA控制完成,软件由以下模块:UART收发模块,PCM解析模块,控制模块,数据缓存模块,接口模块。各功能模块在控制模块的控制下工作,来完成对PCM数据的采集和处理工作。组合模块如图2所示。

UART收发模块

系统选用9600bit/s的波特率传输数据,上位机按照表1所示的格式将配置信息下发给FPGA,经过奇校验数据无误,将数据通过I2C总线写入EEPROM。

表1 配置信息格式

在接收串口数据时,如图3所示,在每个数据中间进行采样,此时数据最为稳定,第0位数据时起始位忽略,接下来是8位数据位和一位奇偶校验位都被采集,最后一位是停止位忽略。在每个码元的每个采样点处间隔两个时钟连续采样三次,然后将这三次的采样值两两按位与,再将相与的结果相或便得到该采样点处的真实值,有效地防止了干扰造成的信号误判。取到数据后将每一位按位取异或后与接受到的奇偶校验位对比,一致则数据正确有效,否则数据错误,给上位机回发aaaa。

PCM解析模块

图1 系统硬件结构图

图2 组合模块结构图

图3 串口接受数据时序

PCM帧结构如图4所示,一个主帧有多个子帧组成,每个子帧由同步头,帧计数器,数据字构成。字长度为4~16,同步头长度为4~32位,且同步头长度是字长度的倍数。

图4 PCM帧格式

图5 状态转移图

图6 数据接收流程

图7 数据缓存

图8 PCM解析功能仿真

PCM解析流程

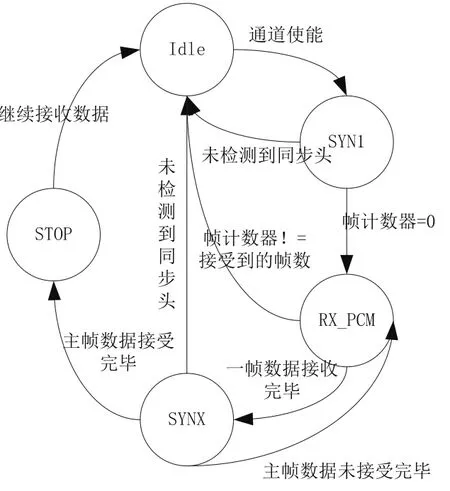

PCM解析模块负责完成位同步,子帧同步,串并转换功能。PCM解析如图5按如下步骤进行:

(1)Idle状态初始化计数器

(2)进入SYN1状态检测同步头

(3)当检测到同步头时,进入RX_PCM 状态检测是否为第一帧

(4)当一帧数据接收完毕,进入SYNX状态检测后面跟着的是否是同步头

(5)当检测到同步头时,判断主帧数据是否接收完毕

(6)一主帧数据接受完毕,进入下一次数据接收

帧同步头检测

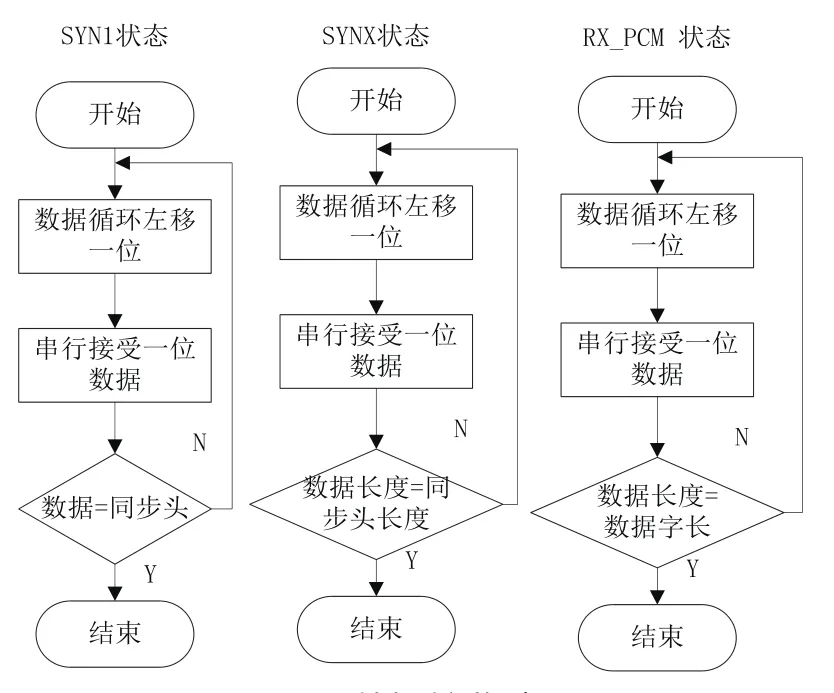

同步头检测分为两种,一种主帧开始的同步头检测即SYN1状态,如图6左图所示。一种是子帧数据接收完成后同步头检测即SYNX状态,如图6中图所示。

PCM数据接收

PCM有多种编码模式,系统设计有NRZL和BiΦL两种码型,以NRZL为例。数据在时钟上升沿发生变化,在时钟的下降沿处于稳定状态,所以当检测到时钟下降沿时进行采样,每个采样点处间隔两个时钟连续采样三次,然后将这三次的采样值两两按位与,再将相与的结果相或便得到该采样点处的真实值。

如图6右图所示,接收PCM数据,一子帧数据接收完毕后需检测后面的数据是否为同步头,如果不是则将此帧数据丢弃并重新检测主帧同步头。

数据缓存模块

数据在被处理的同时被写入双口RAM,当一主帧数据处理完毕,产生一个完成标志,同时将高位地a16 取反。系统检测到完成标志就将数据从RAM通过USB接口发出去,同时继续接收下一帧PCM数据。

系统调试

通过modesim进行功能仿真。,对系统配置,同步头FE6B2840,字长16,一帧有4个字,一主帧有三个子帧。如图8所示,系统在处理数据时将有效的数据写入RAM。

结语

通过对PCM格式进行研究,设计了基于FPGA的两路PCM解调器,解调器可以在接受PCM数据的同时,进行位同步和帧同步的检测并将数据写入RAM。处理后的数据通过USB发给外部设备。经过调试系统工作正常,可以实现PCM解调功能,满足设计要求。

DOI:10.3969/j.issn.1001-8972.2016.06.024