基于FPGA的AES解密算法研究

2016-06-27朱松柏肖顺文

朱松柏,肖顺文,江 敏

(西华师范大学 电子信息工程学院,四川 南充 637009)

基于FPGA的AES解密算法研究

朱松柏*,肖顺文,江敏

(西华师范大学电子信息工程学院,四川南充637009)

摘要:针对网络信息在安全性上的需求,并结合AES加密算法运行速度快、安全性高、硬件配置要求低等特点,对AES加密算法在FPGA上的实现进行了研究。通过对AES加/解密算法的分析,给出基于FPGA的AES解密系统的总体架构,系统包括密钥扩展、控制与存储、轮变换等功能模块,用VHDL语言对各功能模块进行系统设计。实验证明:该系统实现了AES解密功能。

关键词:现场可编程门阵列;高级加密标准;解密算法

随着互联网的快速发展和广泛应用,网络信息在人们日常生活和工作中发挥着日益重要的作用。为保护信息不被盗取,最常用的方式是对信息进行加密处理。高级加密标准AES(Advanced Encryption Standard)[1]采用Rijndael算法[2],使用的是代换-置换网络,而非数据加密标准DES(Data Encryption Standard)的Feistel架构[3],其加密功能更强,且易于实际运作。AES加密算法在实现上分为软件和硬件2种方式,软件实现是通过加密软件在主机上工作实现的,该方式通用、灵活,但占用主机资源、运行速度慢、安全性较低[4];而硬件加密具有实时性、高速性和安全性等优点,能够满足加密技术在各个领域的需要。近年来,AES算法的硬件实现在国内外已逐渐成为热门的研究方向。FPGA(Field-Programmable Gate Array,现场可编程门阵列)既具有硬件的安全性和高速性,又有软件的灵活性和易维护性。AES加/解密系统在FPGA上进行设计,可达到18 Gb/s的吞吐量,不仅能够满足高效性的需求,而且可以方便、快速地修正。

本文用VHDL(Very-High-Speed Integrated Circuit Hardware Description Language)实现了AES-128[5]解密系统,对AES-128解密系统以及系统中各功能模块的设计做了详细描述,并使用Quartus II软件进行系统仿真测试。

1解密系统总体结构

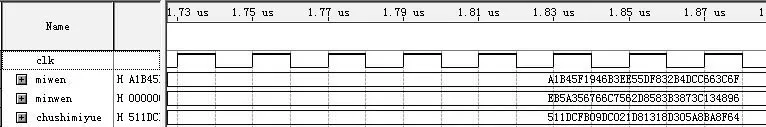

在AES解密流程中,轮密钥加是反向使用密钥扩展模块产生的密钥,即从密钥扩展模块产生的最后1组密钥开始使用,因此在密钥扩展的同时是无法进行解密的,需将扩展的密钥存储起来,待密钥扩展完后再进行解密工作。解密系统主要由密钥扩展模块、控制与存储模块以及轮变换模块3部分组成。密钥扩展模块负责将128位的初始密钥扩展为11组128位密钥,第1组为初始密钥本身,其余10组为扩展的子密钥;控制与存储模块对解密流程进行控制并存储扩展密钥;轮变换[6]模块由逆向字节替换模块、逆向行移位模块、轮密钥加模块、逆向列混淆模块4个子模块组成,是AES解密的核心部分,主要负责完成Rijndael算法,达到解密的目的。AES解密系统结构如图1所示。

图1 AES解密系统结构

2功能模块的实现

2.1密钥扩展模块

如图2所示,data[127..0]引脚为初始密钥输入,swgeneratorkey每生成4个32位字节即128位密钥,ENout引脚就被置高,128位密钥便可通过dout[127..0]端口输出,进入存储模块中。初始密钥在进入密钥扩展模块后,直接被复制为扩展密钥的前4个32位字节。密钥扩展模块产生的44个32位字节组成的数组里k[i][7],对于下标不为4的倍数的元素:

k[i]=k[i-1]⊕k[i-4]

(1)

下标为4 的倍数的元素:

k[i]=Subword(Rotword(k[i-1]))⊕

R[i/4]⊕k[i-4]

(2)其中:Subword为正向字节替换;Rotword为循环左移1个字节;R[i/4]为轮常量;R[1]=1;R[j]=2·R[j-1]。轮常量的变换可以通过循环移位和异或操作完成,用rc表示轮常量,其VHDL实现代码如下:begin

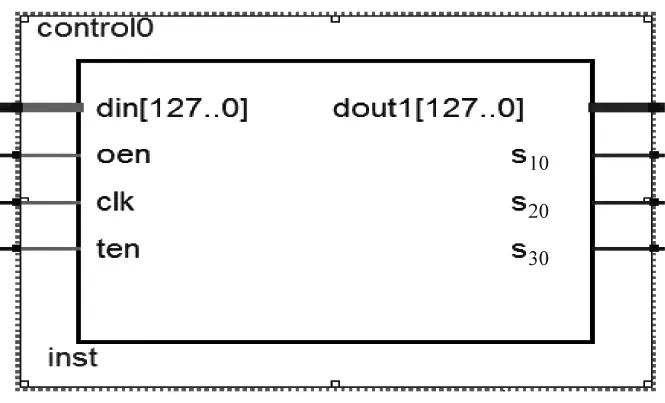

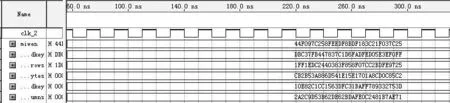

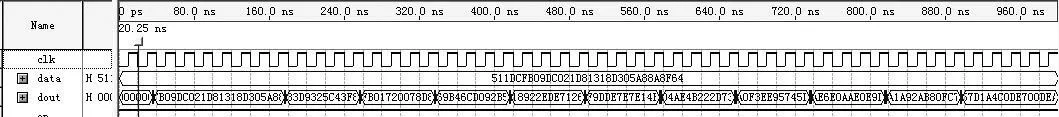

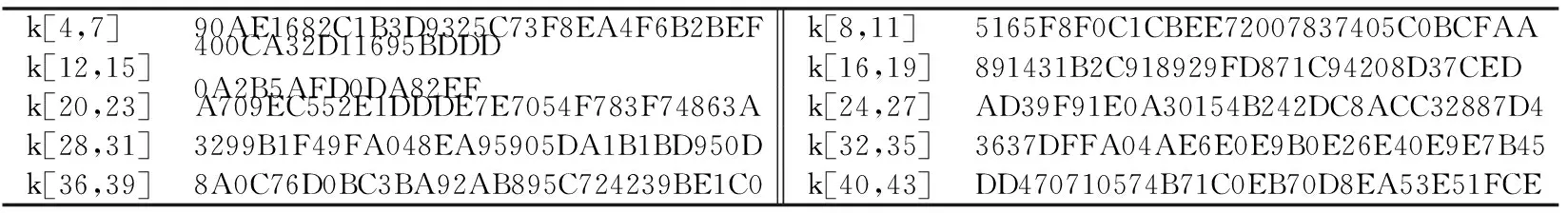

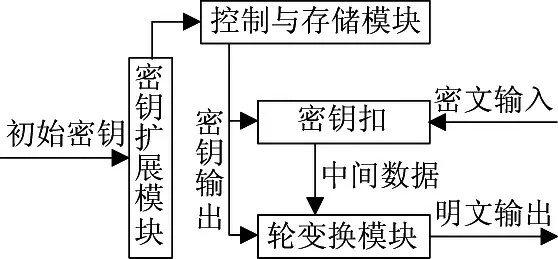

ifrc(31 downto 0) rc(31 downto 1):=rc(30 downto 0); Elsem(7 downto 0):=rc(31 downto 24); m(7 downto 1):=m(6 downto 0); rc(31 downto 24):=m(7 downto 0); rc:=rc xor x"1b000000"; end if; Return rc; End; 图2 密钥扩展模块 2.2控制与存储模块 控制与存储模块如图3所示,该模块主要负责各子模块的启动与关闭和运行的顺序、轮变换中轮数的控制以及存储密钥扩展模块产生的密钥。s10、s20、s30是3个1位的控制信号引脚,s10控制轮变换外独立的密钥加模块的开启与关闭,s20是轮变换的轮数控制信号,轮变换模块的时钟信号使能端与s30引脚相连。存储的密钥通过dout1[127..0]端口按序送到相应的模块中。 图3 控制与存储模块 2.3轮变换模块 轮变换模块如图4所示,该模块由逆向行移位、逆向字节替换、轮密钥加和逆向列混淆4个子模块顺序组成。经过1次密钥加处理的密文被送来时,控制模块将轮变换模块时钟信号的使能端口使能,轮变换模块在clk_2时钟信号上升沿时由miwen[127..0]端口接收密文,依次经过逆向行移位、逆向字节替换处理,并在同一时钟周期的下降沿时与roundkey[127..0]输入的密钥进行密钥加,最后是列混淆变换;当进行至第10轮变换时,控制模块将密钥加处理后的数据即明文直接送到dout2[127..0]端口输出。轮变换模块结构如图5所示。 图4 轮变换模块 图5 轮变换模块结构 逆向行移位、逆向字节替换和轮密钥加操作简单,在FPGA上实现较容易;逆向列混淆中使用的乘法和加法是定义在有限域GF(28)上的。其加法就是异或操作,乘法可以用中间结果相加的方法实现,以D乘7C为例: D·7C=(1 101)×(7C)=[(1000)⊕(0100)⊕(0001)×7C]= x3×(7C)⊕x2×(7C)⊕(7C) (3) 式(3)中某值乘上x(即{02}),其结果是将该值向左移1位,如果该值的最左边的位为1,那么在移位后还要与(00011011)异或。 x×(7C)=(00000010)×(11011100)= (10111000)⊕(00011011) (4) 7C最左边的位为1,所以不仅要向左移一位,还要在移位后异或(00011011)。 3模块仿真及结果分析 3.1轮变换模块仿真及结果分析 此次仿真输入为32位十六进制数即128位的二进制数据,依次通过轮变换中逆向行移位、逆向字节替换、轮密钥加和逆向列混淆4个子模块,即轮变换中前一个子模块的输出即为后一个子模块的输入。仿真结果如图6所示。 图6 轮变换模块仿真结果 图6中上面3个端口分别为时钟信号、输入密文和输入密钥,下面依次为逆向行移位、逆向字节替换、轮密钥加和逆向列混淆4个子模块的输出。 逆向行移位可提高AES算法的扩散性,将图6中逆向行移位的输入输出转换成4×4的a、b矩阵,可以看出a、b矩阵第1行是一样的,b矩阵第2行相对于a矩阵第2行循环右移一个字节,b矩阵第3行相对于a矩阵第3行循环右移2个字节,b矩阵第4行相对于a矩阵第4行循环右移1个字节,与期望结果一样;对输入逆字节替换模块的数据进行逆S盒查表,其结果与逆字节替换模块输出一致;轮密钥加模块输入与输入密钥的异或结果正是轮密钥加模块的输出;逆向列混淆的输出与理论计算结果一致,逆向列混淆计算较复杂,通过此模块可以快速地得出逆向列混淆计算结果。轮变换模块中4个子模块均能达到预期效果,即达到设计要求。 3.2密钥扩展模块仿真及结果分析 密钥扩展模块仿真结果如图7所示。 图7 密钥扩展模块仿真结果 由图7可知,该模块共产生11组128位密钥,由初始密钥511DCFB09DC021D81318D305A8BA8F64 产生的10轮子密钥如表1所示。 表1 扩展密钥列表 4解密系统仿真结果及数据测试 在解密流程中,初始密钥直接输入密钥扩展模块进行扩展,并送至控制与存储模块存储。待密钥产生完成之后,控制模块开启密钥加模块,并将密文(A1B45F1946B3EE55DF832B4DCC663C6F)和相应的第11组密钥(DD470710574B71C0EB70D8EA53E51FCE)送至该模块中进行密钥加操作。经过一次密钥加的密文再被送至轮变换模块中,轮变换模块处理后的输出即为明文。图8为解密系统仿真结果。 图8 解密系统仿真结果 图8中的miwen是由miwen和chushimiyue经AES解密系统解密所得到的。解密系统中轮变换模块的轮密钥和每轮输出如表2所示。 5结语 AES已成为对称密钥加密中最流行的算法之一,广泛应用于无线通信、数字存储等众多领域[8]。本文采用VHDL硬件描述语言完成了对AES-128解密系统中密钥扩展、控制与存储、轮变换等功能模的设计,通过综合和仿真,各模块均达到设计要求;并在此基础之上,对AES-128解密系统进行了数据测试,给出了测试的密文输入、初始密钥输入以及每轮变换的输出,将解密出的明文与理论计算值相对比,结果表明本文在FPGA上实现的AES-128解密系统完全可行。 参考文献: [1] 何建华.FPGA上SHA算法和AES算法的优化实现技术研究 [D].广州:华南理工大学,2011. [2] 钱晓捷, 师攀攀, 王建辉.基于多核的Rijndael算法的并行优化与实现[J]. 计算机工程与设计, 2012, 33(6):2197-2202. [3] 刘建立.AES加密机制在IPSec协议中的应用研究及其硬件实现[D].南京:南京理工大学,2007. [4] 王亮.针对AES加密算法的研究及其FPGA实现[D].上海:上海师范大学,2010. [5] 韩少男,李晓江.可兼容AES-128、AES-192、AES-256串行AES加密解密电路设计[J].微电子学与计算机,2010,27(11):40-41. [6] 鹿钦鹤,任涛.AES算法的研究[J].长春理工大学学报(自然科学版),2007, 30(1):83-85. [7] 斯托林斯.密码编码学与网络安全:原理与实践[M].4版.北京:电子工业出版社, 2008:118-119. [8] 赵雪梅.AES加密算法的实现及应用[J].常熟理工学院学报,2010, 24(2):105-110. Research on AES Decryption Algorithm Based on FPGA ZHUSongbai*,XIAOShunwen,JIANGMin (College of Electronical and Information Engineering, China West Normal University, Nanchong 637009, China ) Abstract:In view of the network information security need, and combined with the AES encryption algorithm running fast, high security, low hardware configuration requirements, the implementation of AES encryption algorithm on the FPGA is studied. Based on the analysis of the algorithm of AES encryption-decryption, the article presents the general structure of AES decryption system based on FPGA. The system includes function modules, such as the secret key extension module, the control and storage,the transformation module and so on, and the function modules are designed by using VHDL language. After the verification of the system, it realizes the AES decryption function. Key words:FPGA; AES; decryption algorithm DOI:10.13542/j.cnki.51-1747/tn.2016.02.008 收稿日期:2015-11-30 基金项目:四川省教育厅基金项目“软件无线电中的加密模块研究”(15ZA0145) 作者简介:朱松柏(1991— ),男(汉族),四川阆中人,在读硕士研究生,研究方向:软件无线电、AES加密技术及SOPC技术研究,通信作者邮箱:1130479837@qq.com。 中图分类号:TP309.7 文献标志码:A 文章编号:2095-5383(2016)02-0027-04 肖顺文(1970— ),男(汉族),四川金堂人,教授,研究方向:软件无线电及EDA技术研究。