LDPC/Turbo双模译码器技术发展与前景综述

2016-06-17王秀敏洪芳菲曹维林

王秀敏,洪芳菲,单 良,王 怡,曹维林

(中国计量学院 信息工程学院,浙江 杭州 310018)

LDPC/Turbo双模译码器技术发展与前景综述

王秀敏,洪芳菲,单良,王怡,曹维林

(中国计量学院 信息工程学院,浙江 杭州 310018)

【摘要】Turbo码和LDPC码的性能接近Shannon理论极限,有着很强的抗衰落和抗干扰的能力,因此特别适合在卫星通信、深空通信、移动通信、无线接入等无线通信系统中运用.目前LDPC/Turbo双模译码器技术还没有形成相对成熟、完整的理论体系,对相关研究的系统性总结工作仍然相对缺乏. 我们首先回顾了LDPC/Turbo双模译码器的发展现状,其次详细总结了译码器结构以及SISO的实现方法,并对其进展情况和特点分别进行总结分析. 最后,就双模译码器研究中现存的问题加以分析,并探讨了其发展趋势.

【关键词】双模译码器;系统结构;软输入软输出

先进的信道编译码技术可以降低信息在传输过程中由于噪声和各种干扰而造成的误差,提高整个系统可靠性. 因而高效的信道编译码技术渐渐地成为4G/5G[1]移动通信系统中亟待解决的关键技术之一. 在未来的移动通信标准中,信道编译码方案已不仅仅是纠错码[2]、交织算法[3]和编译码算法[4]的选择问题,它还涉及各种纠错码优化问题. 其中Turbo码[5]和LDPC码[6]与它们所采用的迭代译码技术开始在通信学界独领风骚,逐步取代现已成熟的线性分组码和卷积码技术,而且还会进一步与其他先进技术相结合,广泛地用于各种数字通信和信息处理之中.

目前,国际上对LDPC码和Turbo的理论研究已取得重要进展,而且工程应用在现场可编程门阵列(field programmable gate array, FPGA)[7]和超大规模集成电路(very large scale integration,VLSI)[8]实现方面的研究也在全方位开展当中. 在文献[9]中,双模译码器的设计思想已见雏形,文献提出了一种统一的可编程架构的译码器结构,它可应用于多种通信标准(3GPPLTE, IEEE802.11n, IEEE802.16(e) and DVB-S2/T2).此外,文献[10]设计了一个以ASIP(application specific instruction set processor,专用指令集处理器)为基础的多码型前向纠错(FEC)的体系结构框架, 适用于实现三种码(卷积码、Turbo码和LDPC码)的专用译码器.该双模译码器适用于各种码字的无冲突内存映射方法,此外文献中还计算了各种并行度的多项式时间,与现有的最佳方法相比,计算时间有了很大的提高.

尽管许多学者已经进行了大量相关的研究工作,目前基于LDPC/Turbo双模甚至多模译码器仍然面临许多挑战,还没有形成相对成熟、完整的系统理论体系,对相关研究的总结工作仍然相对缺乏. 为此本文的目的在于从多个方面,对国内外有关LDPC/Turbo双模译码器研究现状和成果进行梳理和综述,为后继开展更为深入的理论和应用研究提供借鉴与参考.

本文首先简述了双模译码器系统的主要结构组成. 在双模结构的基础上,特别讨论了SISO[11](soft input soft output)关键实现技术,并对一些具体的实现方案给予分析与评价. 最后展望了LDPC/Turbo双模译码器的研究发展方向.

1双模译码器结构实现进展

1.1双模结构简介

Turbo码和LDPC码具有优异的渐进性能,因此这两种码的编译码的联合技术与信道编译码方案得到了较多的关注和研究,目前LDPC/Turbo双模译码器[12]的研究主要分为理论研究、性能分析以及应用研究三个方面.

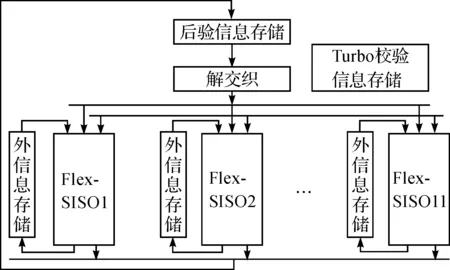

在文献[13]中,Sun Yang等人根据相似的译码推导过程[14],在VLSI的平台上实现了并行度为P的双模译码器. 该双模译码器是基于资源共享思想设计的.资源共享主要包括双模译码器的计算单元共享和存储单元共享两个方面.对于高吞吐量的应用程序,它使用多个SISO译码器并行工作来实现计算单元共享并提高译码速度. 对于Turbo码来说将码字划分为几个子块来实现P个SISO平行处理[15],而对于LDPC码来说,译码器通过多个校验节点来实现译码器的平行处理过程[16]. 文献[13]中提到的多并行度的SISO双模译码器如图1.

图1 双模译码器结构实现Figure 1 Structure of dual-mode decoder

在这种结构体系中,存储器划分为三类:外信息存储器,初始信息/后验信息存储器,Turbo码校验信息存储器. 其中外信息存储器存储的是每一个SISO产生的外信息值,初始信息存储器存放初始信息值以及更新后的LLR值(log likelihood ratio),而校验信息存储器只是针对于Turbo码设定的,存储Turbo码的校验信息位. 在图中交织器和解交织器执行LLR值的来回切换的过程.

文献[13]中实现了以下三种情况的高性能LDPC/Turbo双模译码器:1)802.16e(WAMAX)标准下的LDPC码;2)802.11 n(WLAN)标准下的LDPC码;3)3GPP-LTE标准下的Turbo码. 该译码器的最大时钟频率是500 MHz. 合成的核心面积为3.2 mm2,其中包括该译码器中的所有组件.

除了上述以VLSI为平台的实现方法外,基-4[17]结构同样适合于双模译码器的设计,在文献[18]中,Cheng等人通过可重构的基-4网格译码结构实现了支持多标准的高通量的LDPC/Turbo双模译码器. 在存储单元优化方面,Carlo等人[19]通过设计一个可循环的缓存单元来存储信道信息,可以实现不同模式之间无停顿的切换. 他们对不同模式所消耗的缓存单元和译码过程中的迭代过程进行了分析,实现了无停顿切换的LDPC/Turbo双模译码器.

1.2SISO结构实现

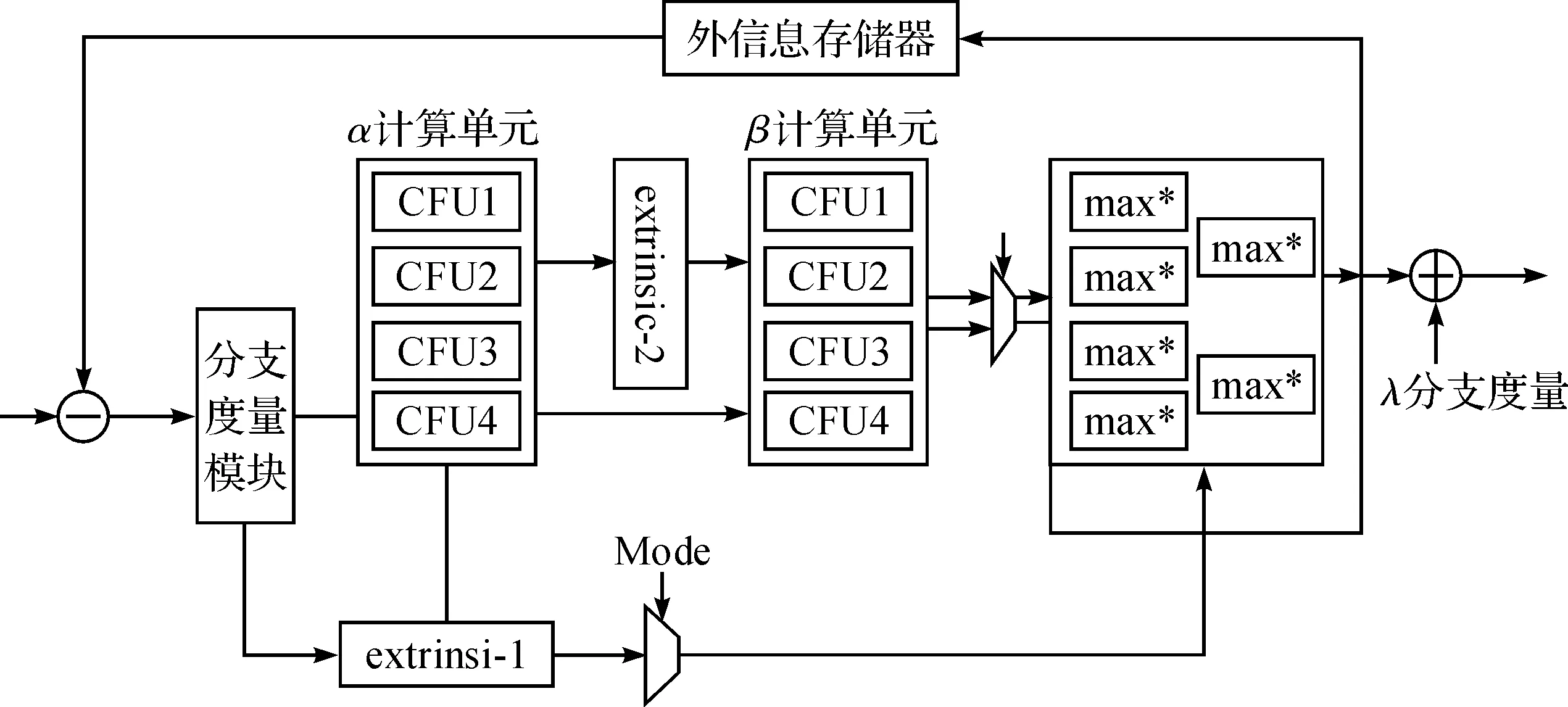

双模译码器的难点是SISO单元的设计,在文献[13]中SISO处理单元结构设计包括2个不同的解码核心(LDPC码和Turbo码) ,每个SISO单元可并行处理12个LDPC码的SPC码,或同时处理Turbo码的8个编码状态,在LDPC模式时采用部分并行译码结构,SISO阵列最大可并行处理96个SPC码的译码. 在Turbo模式采用的是子块并行的译码结构,SISO阵列最大可支持12个子块的并行译码. 文献[13]中SISO处理单元结构如图2,该处理单元主要包括四个功能单元:α(前向度量)计算单元,β(后向度量)计算单元,extrinsic-1单元和extrinsic-2单元. 在Turbo模式下,所有的功能单元都处于工作状态,而在LDPC模式下,6个max*不参与计算过程,而是直接略过输出后验信息.

图2 SISO单元Figure 2 SISO unit

需要说明的是,设计一个低复杂度且具有高灵活度的双模译码器关键的技术基础,是存在大规模的硬件资源共享,BCJR(bahl cocke jelinek raviv)算法不仅可以很好的运用于Turbo码译码过程中,也可以TDMP(Turbo decoding message passing)的形式应用于LDPC中. LDPC码的TDMP算法是一种特殊形式的分层译码,其中校验节点的操作是通过BCJR算法来实现的. 为了更好地应用于移动应用程序中,Giuseppe Gentile[20]等人通过码间网格模式很好地实现了TDMP算法和BCJR算法下的双模译码器结构.

在文献[21]中,作者在共享内存单元、功能单元和算法单元的基础上,权衡速度、功耗、成本、灵活性等多个方面的约束,用ASIP芯片实现了适用于卷积码、Turbo码和LDPC码的多模译码器. 与文献[13]相比,该设计实现了4个并行度的PE(processing elements)计算,该单元的实现功能相当于SISO单元. PE单元主要包括的功能单元与SISO单元类似,实现的功能也相同,文献[21]中PE结构如图3.

图3 PE处理单元Figure 3 PE processing unit

2现存问题分析

现有的通信译码器,仍然着重于译码器结构的实现和简化. 对于多模译码器的实现,大多是基于多算法处理单元的共享设计,除了工作量的增加,仍然保留了本身的缺点,这些在许多研究中已有充分的论述[22]. 除此之外,目前双模译码器的设计还存在如下问题.

1)交织器的优化设计有待加强. 如前所述,双模译码过程中包含信道信息和后验信息的交织和解交织过程,特别是在Turbo模式下,交织器将LET[23]标准中QPP[24]交织公式进行简单的变形,得到交织迭代公式.但是,由于码字中每一位编译码的比特,交织后对应的位置不一样,导致了交织器只能逐位进行,而不能并行的多位处理.

2)LDPC/Turbo双模译码器理论分析手段缺乏. 目前的双模译码器存在算法复杂度较大、数据量大、复用空间较少和各因子选取不当等问题,较少的用理论系统的方法来解决上述存在的问题. 而随着双模译码器技术的发展,高性能低复杂度的技术实现需求也越来越多,利用理论分析指导双模译码器的实现是目前亟需要解决的问题之一.

3)应用的网络信道还比较单一.目前双模译码方案都是在特定的加性高斯白噪声信道(additive white gaussian noise, AWGN)下提出的,目前还是无法灵活地应用到其他信道,例如二进制删除信道 (binary erasure channel, BEC)[25]及二进制对称信道 (binary synchronous communication, BSC)[26]等. 实际的双模译码器实现较复杂,只应用于特定的网络模型显然不能够满足当今无线通信网络的技术发展.

3发展趋势探讨

随着Turbo码和LDCP码的研究发展,在未来移动通信系统设计中,对通信无误传输的需求也越来越高,基于LDPC/Turbo双模译码器的研究需求也越来越迫切. 针对上述存在的问题,可以预见未来的LDPC/Turbo双模译码器的发展将会呈现以下趋势.

1)提高交织并行度. 与当前逐位交织处理不同,并行交织器充分考虑到复用多路交织存储器取址,采用双口RAM,并行输出.

2)基于密度进化理论指导LDPC/Turbo双模译码器实现. 密度进化理论包括连续密度进化、离散密度进化及高斯近似. 它可以分析LDPC码和Turbo码的渐近性能,优化度数分布,迭代次数,归一化因子等.

3)多信道、多码率以及多码长的LDPC/Turbo双模译码器实现. Wimax标准和TD-LTE标准定义多种不同码率和不同码长的码字,在之后的研究和设计当中应当更注重译码器的灵活性和兼容性,不仅仅止步于对码长码率的研究,也包括对多信道的研究. LDPC码和Turbo码的优异性能使得许多通信标准选择这两种码字作为信道编译码方案.不仅如此,在未来的通信系统中,双模以及多模式的纠错译码器在不同通信网络之间的信息交流将会起到重要的作用.

【参考文献】

[1]SUN Songlin, KADOCH M, GONG Liang, et al. Integrating network function virtualization with SDR and SDN for 4G/5G networks[J]. IEEE Network,2015,29(3):54-59.

[2]METZNER J. Correction of two (or often more) vector symbol errors with the outer structure of a hamming single error correcting code[J]. IEEE Communications Letters,2014,18(12):2069-2072.

[3]CHEN Li, JOHNSTON M, TIAN Guiyun. Iterative Detection-Decoding of interleaved hermitian codes for high density storage devices[J]. IEEE Transactions on Communications,2014,62(10):3401-3409.

[4]韩新强,金小萍,冯会真,等.差分协作系统中的软输入软输出多符号差分球形译码[J].中国计量学院学报,2013,24(2):171-176.

HAN Xinqiang, JIN Xiaoping, FENG Huizhen, et al. Soft-input soft-output multiple-symbol differential sphere decoding for differential cooperative system[J]. Journal of China University Metrology,2013,24(2):171-176.

[5]WILDE M M, HSIEH M H, BABAR Z. Entanglement-Assisted quantum turbo codes[J]. IEEE Transactions on Information Theory,2014,60(2):1203-1222.

[6]WANG Yige, FOSSORIER M. Doubly Generalized LDPC Codes over the AWGN Channel[J]. IEEE Transactions on Communications,2009,57(5):1312-1319.

[7]高战立,余桂英,唐玮.FPGA图像采集系统研究与设计[J]. 中国计量学院学报,2014,25(1):75-79.

GAO Zhanli, YU Guiying, TANG Wei. Research and design of an image acquisition system based on FPGA[J]. Journal of china university metrology,2014,25(1):75-79.

[8]LIN Jun, SHA Jin, WANG Zhongfeng, et al. An efficient VLSI architecture for nonbinary LDPC decoders[J]. IEEE Transactions on Circuits and Systems II-Express Briefs,2010,57(1):51-55.

[9]SUN Yang, CAVALLARO J R. Unified decoder architecture for LDPC/turbo codes[C]//IEEE Workshop on Signal Processing Systems. Washington, IEEE,2008:13-18.

[10]SANI A H, COUSSY P, CHAVET C. A first step toward On-Chip memory mapping for parallel turbo and LDPC decoders: a polynomial time mapping algorithm[J]. IEEE Transactions on Signal Processing,2013,61(16):4127-4140.

[11]YOO I, KIM B, PARK I C. Tail-overlapped SISO decoding for high-throughput LTE-Advanced Turbo decoders[J]. IEEE Transactions on Circuits and Systems I: Regular Papers,2014,61(9):2711-2720.

[12]CONDO C, MARTINA M, MASERA G. VLSI implementation of a Multi-Mode turbo/LDPC decoder architecture[J]. IEEE Transactions on Circuits and Systems I-Regular Papers,2013,60(6):1441-1454.

[13]SUN Yang, CAVALLARO J R. A flexible LDPC/turbo decoder architecture[J]. Journal of Signal Processing Systems,2011,64(1):1-16.

[14]FREDERIK N, BRUNO B, SIEBERT B, et al. A unified instruction set programmable architecture for multi-standard advanced forward error correction[C]//IEEE Workshop on Signal Processing Systems. Washington, IEEE,2008:31-36.

[15]BROUNO B, ALEXANDRE G, VEERLE D, et al. A scalable 8.7-nJ/bit 75.6-Mb/s parallel concatenated convolutional (turbo-) codec[C]//In IEEE International Solid-state Circuit Conference (ISSCC). San Francisco: IEEE,2003:152-484.

[16]BRACK T, ALLES M, LEHNIGK-EMDEN T, et al. Low complexity LDPC code decoders for next Generation standards[C]// 2007 Design, Automation & Test in Europe Conference & Exhibition. Nice: IEEE,2007:331-336.

[17]AL-KHAYAT R, MURUGAPPA P, BAGHDADI A A. Area and throughput optimized ASIP for Multi-Standard turbo decoding[C]// 22nd IEEE International Symposium on Rapid System Prototyping (RSP). Karlsruhe: IEEE,2011:79-84.

[18]HUNG L C, SHIANG Y C. Multi-mode radix-4 SISO kernel design for Turbo/LDPC decoding[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2015,23(10):2256-2267.

[19]CARLO C, MAURIZIO M, GUIDO M. A network-on-chip-based turbo/LDPC decoder architecture[C]//Design, Automation & Test in Europe Conference & Exhibition (DATE). Dresden: IEEE,2012:1525-1530.

[20]GENTILEG, ROVINI M, FANUCCI L. A multi-standard flexible Turbo/LDPC decoder via ASIC design[C]//2010 6th International Symposium on Turbo Codes & Iterative Information Processing. Brest: IEEE,294-298.

[21]KUNZE S, MATUS E, FETTWEIS G, et al. Combining LDPC, Turbo and Viterbi decoders: benefits and costs[C]//IEEE Workshop on Signal Processing Systems (SiPS). Beirut: [s. n.],2011:216-221.

[22]WU Zhenzhi, LIU D. High-throughput trellis processor for multi-standard FEC decoding[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2015,23(12):2757-2767.

[23]GERARDIN S, BAGATIN M, PACCAGNELLA A, et al. Upsets in phase change memories due to High-LET heavy ions impinging at an angle[J]. IEEE Transactions on Nuclear Science,2014,61(6):3491-3496.

[24]KIM B J, YOO I, PARK I C. Low-complexity parallel QPP interleaver based on permutation patterns[J]. IEEE Transactions on Circuits and Systems II-Express Briefs,2013,60(3):162-166.

[25]RATHI V, ANDERSSON M, THOBABEN R A, et al. Performance analysis and design of two edge-type LDPC codes for the BEC wiretap channel[J]. IEEE Transactions on Information Theory,2013,59(2):1048-1064.

[26]CHILAPPAGARI S K, CHERTKOV M, VASIC B. An efficient instanton search algorithm for LP decoding of LDPC codes over the BSC[J]. IEEE Transactions on Information Theory,2011,57(7):4417-4426.

The advance overview on LDPC/Turbo dual-mode decoders

WANG Xiumin, HONG Fangfei, SHAN Liang, WANG Yi, CAO Weilin

(College of Information Engineering, China Jiliang University, Hangzhou 310018, China)

Abstract:Turbo code and Low-Density Parity-Check (LDPC) code can achieve excellent performance, which are close to the Shannon limit. They have strong ability of anti-fading and anti-interference. Therefore, it is especially suitable for applications in satellite communication, deep space communication, mobile communication, wireless access and other wireless communication systems. Currently the technology based on the LDPC/Turbo dual-mode decoder has not formed a relatively complete and mature theoretical system. A systematic summary of the relevant research work still lacks. Firstly we reviewed the development status of the LDPC/Turbo dual-mode decoder. Then we summarized the structure of the decoder and the implementation methods of SISO in detail. Meanwhile we analyzed their progress and characteristics. Finally we analyzed the existing problems in the research of the dual-mode decoder and tried to explore its development trends.

Key words:dual-mode decoder; system architecture; SISO

【文章编号】1004-1540(2016)01-0063-05

DOI:10.3969/j.issn.1004-1540.2016.01.012

【收稿日期】2015-12-28《中国计量学院学报》网址:zgjl.cbpt.cnki.net

【基金项目】国家自然科学基金资助项目(No.61379027),国家自然科学青年基金资助项目(No.51404223),浙江省自然科学青年基金资助项目(No.LQ14E060003).

【作者简介】王秀敏(1963- ),女,辽宁省锦州市人,教授,主要研究方向为电子信息与通信类. E-mail:wxm6341@163.com

【中图分类号】TN91

【文献标志码】A