高速光纤总线技术研究

2016-01-21蒋东新

唐 敏,饶 垚,蒋东新,胡 伟,何 磊

(中国电子科技集团公司 第四十四研究所,重庆 400060)

高速光纤总线技术研究

唐敏,饶垚,蒋东新,胡伟,何磊

(中国电子科技集团公司 第四十四研究所,重庆 400060)

摘要:分析了几种常见高速光纤总线技术在物理层、链路层和逻辑层上的相似性和差异性,且研究在实际工程应用中的可用性和可靠性。

关键词:光纤;总线技术;可用性;可靠性

收稿日期:2015-01-15 2015-03-10

作者简介:唐敏(1979-),男,重庆市人,工程师,从事FPGA开发设计和光传输设备研发方面工作;饶垚(1984-),女,重庆市人,工程师,从事光波分复用设备研发工作。

中图分类号:TN929.11

文献标识码:识码:A

文章编号:编号:1008-6390(2015)03-0167-04

基金项目:国家自然科学基金(60443004);重庆市教委科研项目(KJ120824)

在嵌入式系统中,高速光纤总线技术Ethernet、PCI-Express(PCIe)、RapidIO得到了越来越广泛的应用。它们都使用相似的串行解串器(SerDes)技术,提供的吞吐量和时延性能都要超过宽的并行总线技术。随着技术的不断发展,其趋势是采用通用SerDes技术。这意味着这些协议提供的原始带宽不会有明显的差异。相反,每种协议的用途将取决于如何使用带宽。

一、高速光纤总线的物理层、链路层分析

在这三种高速光纤总线的物理层描述中,光纤接口标准均采用相似的结构,如图1所示,由以下几个主要功能模块组成:逻辑控制器、数据缓存FIFO、串行解串器(SerDes)及光电信号转换模块(O/E和E/O模块)。其中的SerDes采用适用于光纤传输的8B/10B编码或16B/20B编码格式,O/E和E/O模块实现光纤通道串行光信号和串行电信号之间的相互转换。

图1 高速光纤总线光纤接口标准

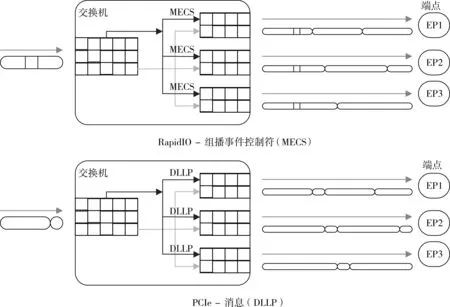

但是,这三种高速光纤总线标准在物理层/链路层的流量控制和误码恢复方面有很大的区别。Ethernet流量控制主要是在网络层用软件实现的,因为对大型网络这是最有效的处理方式。Ethernet唯一的物理层流量控制机制是PAUSE,它将中断一定的传输时间。有限的物理层流量控制意味着Ethernet将采用丢弃数据包的方式处理拥塞。与之不同,PCIe和RapidIO的物理层流量控制机制可确保数据包的可靠传送,每个包都会被发送器保留直到被确认。如果检测到发送误码,链路维护协议可确保发生误码的数据包得到重传。PCIe保证采用数据链路层数据包(DLLP)发送,而RapidIO则使用控制符进行发送。与DLLP不同的是,RapidIO控制符可以被嵌入数据包内,这样即可实现低时延的RapidIO流量控制信息(如缓存占用量)交换,这将允许更快地发送更多的数据包。见图2。

图2 数据流量控制方式

在图2-a部分,器件A不能向器件B发送任何数据包,因为器件B中的缓存是满的。器件B在向器件A连续发送数据包。在图2-b部分,器件B中的一个缓存空出来了,此时器件B必须告知器件A它能发送数据包了。在图2-c的RapidIO描述部分,控制符被嵌入正在发送的数据包内。图2-d是描述PCIe的工作方式,可以看到DLLP在当前数据包传送完成之前是无法得到传送的。因此与其他协议相比,RapidIO协议能以更低时延和更高吞吐量完成可靠的数据包传送。将控制符嵌入数据包的能力使得RapidIO流量控制的其余功能比PCIe或Ethernet都要丰富。

除了更有效的流量控制外,将控制符嵌入数据包使得RapidIO具有PCIe和Ethernet目前无法提供的能力,如图2所示。控制符还可以用来低时延和低抖动地在整个RapidIO系统中分配事件。

图3 高速光纤总线中事件分配

这一功能可以支持将公共实时时钟信号分配到多个端点或为天线系统分配定时信号、帧信号等应用,还可以用于发送其他系统事件信息,实现很多其他光纤总线不能完成的实际工程需求。如图3所示,PCIe的DLLP在每次通过交换机传送时都会引入很大的时延和抖动。相反,RapidIO协议允许在整个RapidIO架构中分配信号时具有低于10个单位间隔(UI)的抖动性能和每次交换低于50ns的时延性能,并且与数据包业务无关。

PCIe和Ethernet可以选择扩展各自的规范以允许事件获得低时延的分配。引入类似控制符的概念对Ethernet来说是很大的进步。Ethernet生态系统下已有几家组织正在改进存储应用中的Ethernet能力,其中就可能需要用到类似控制符的概念。Ethernet还准备采用简单的XON/XOFF流量控制来进一步增强性能。

PCIe目前还不允许将DLLP嵌入TLP,因为这个概念不能兼容传统的PCI/X总线操作。嵌入TLP的DLLP会产生没有数据可以放置到传统总线上的周期。PCIe端点可以工作在存储-转发模式,确保数据包在转发给总线之前全部接收到,而代价是时延的显著增加和吞吐量的降低。由于PCIe主要用于单处理器系统的板上互连,并且一直需要保持与传统总线标准的兼容,所以PCIe最终也是不太可能允许DLLP被嵌入TLP的。

二、高速光纤总线的逻辑层分析

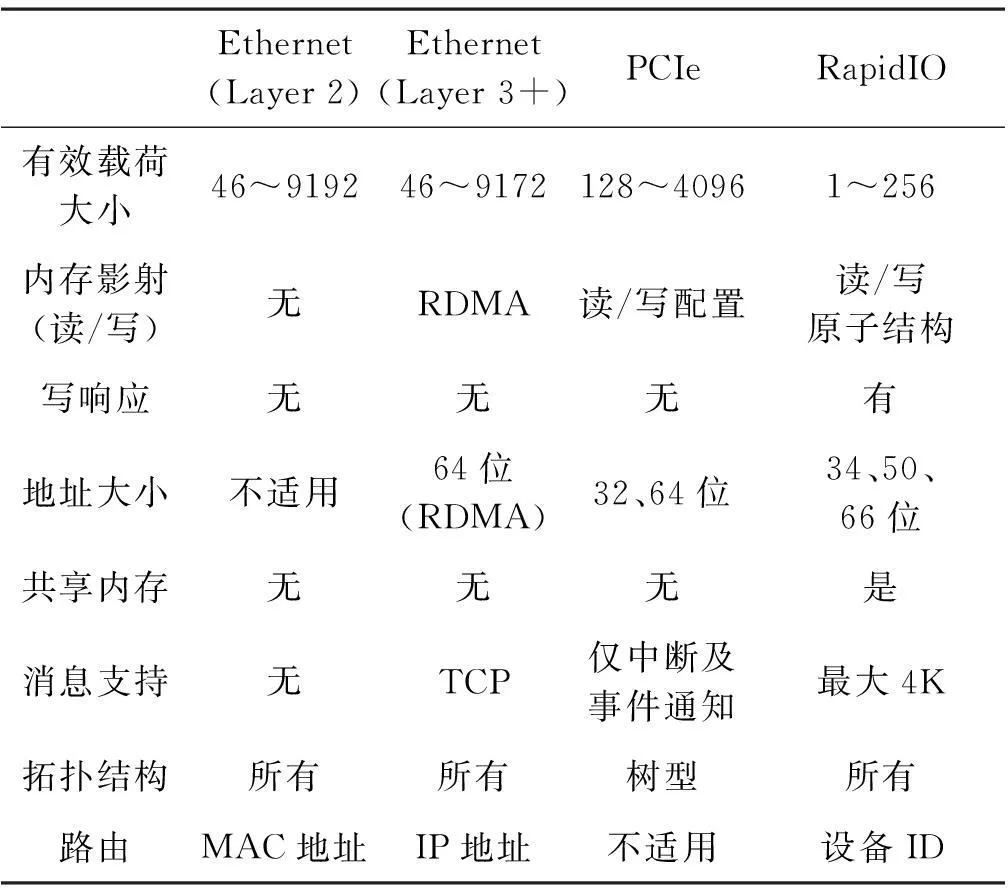

RapidIO、PCIe和Ethernet在逻辑层方面也有多个差异较大的地方,最明显的区别是所支持的语义。表1是这三种标准在协议层的对比。

PCIe数据包支持基于地址的读写语义。在PCIe系统中,发起读或写的实体必须知道系统的全局存储器映射图中的目标地址,这对控制平面应用而言是很自然的一种方法。然而,这种对全局地址映射图的依赖性也会导致难以发展的相关连动软件系统。PCIe协议也支持通过消息TLP的消息传送。不过消息TLP只支持有限数量的功能,如中断和复位信号。这点与Ethernet和RapidIO消息包有很大的不同,后者可用于进程间通信。

与PCIe不同,建立在Ethernet物理层之上的软件协议只支持消息语义。在发送消息时,发送者只需知道接收地址。寻址机制是分层的,因此没有哪个节点必须知道所有的地址。地址可能会随系统发展而改变,支持软件单元实现相互间的松散关联。这种属性对数据平面应用来说是必要的。

表1 RapidIO、PCIe和Ethernet逻辑层对比

RapidIO同时支持读/写和消息语义。除了明显的架构优势和系统灵活性外,对读/写和消息处理的支持允许单路互连同时用于控制数据平面。因此RapidIO系统要比必须结合PCIe和Ethernet的系统更简单,从而具有降低功耗和成本的优势。PCIe不可能在其数据包定义中合并进程间通信消息语义,因为与传统PCI和PCI-X总线的操作相冲突。PCIe是围绕根联合体概念设计的,这个联合体只包含系统中的处理器。

目前大家对Ethernet通过远程直接存储器访问(RDMA)协议支持读写语义还存有争议,该协议支持设备间进行直接存储器拷贝。不过,RapidIO和PCIe读写语义的效率要比RDMA高得多。RDMA协议建立在其他Ethernet协议之上,如TCP,并且每个数据包都需要大量的包头开销。与RapidIO读/写事务处理相比,RDMA的实现要在时延和带宽方面付出大得多的代价。消息语义的一种可能应用是其他协议的封装。RapidIO拥有封装各种协议的标准。这种封装能力给系统设计人员提供了许多优势,包括即将大力推广的RapidIO背板,这就保证了任何以后、传统或是专有协议都可以用标准的RapidIO组件进行封装和传送。例如,用于Ethernet封装的现有RapidIO规范,设计人员就可在基于RapidIO的系统中使用基于Ethernet的软件。虽然Ethernet也支持封装,并且有多种封装标准可以选择,但是Ethernet协议层需要更多的字头开销,封装效率大大低于RapidIO。曾经有组织试图对在PCIe结构上实现各种协议封装进行标准化,但最终失败,因为与传统PCI/X总线密切相关的要求,很难将PCIe扩展成适合嵌入式系统的结构。

三、高速光纤总线的应用分析

大多数设计人员都很熟悉基本的Ethernet协议特征。Ethernet是一种“尽力而为”的数据包传送方式。在Ethernet协议物理层上建立的软件协议提供信息的可靠传输,如TCP/IP、UDP等,因为基于Ethernet的系统一般在网络层执行流量控制,而不是在物理层,所以一般基于Ethernet的系统带宽都要超配20%~70%。因此Ethernet最适合高时延的设备间应用,或带宽要求较低的板上/板间应用。

PCIe针对板上互连的数据包可靠传送作了优化,这种场合的典型时延在毫秒数量级。PCIe协议交换的是事务处理层数据包(TLP),如读和写,以及被称为数据链路层数据包(DLLP)的少量特殊链路信息。DLLP用于链路管理功能,包括物理层的流量控制。PCIe向上兼容传统的PCI和PCI-X器件,这些器件认为处理器位于总线层的顶部,因此PCIe具有能够充分利用与PCI相关的软件和硬件知识产权的优势。但是,也正因为这样,传统PCI总线对交换式PCIe协议有很大的约束。

RapidIO技术则针对嵌入式系统作了优化,尤其是那些要求多处理单元合作的嵌入式系统。与PCIe一样,RapidIO协议交换的是数据包和被称为控制符的少量特殊链路信息。RapidIO兼具PCIe和Ethernet的特性。例如,RapidIO可以提供可靠和非可靠的数据包传送机制。RapidIO也具有许多独特的功能,因此最适合板上、板间以及短距离(小于100m)的设备间应用。

四、高速光纤总线的可靠性分析

在大多数使用光纤总线系统的应用中,对可靠性都有明确要求。系统需要误码检测、误码提醒、故障元件分析与隔离以及恢复机制。从高层看,PCIe、RapidIO和Ethernet在所有这些方面都有相似的功能。不过在备份策略以及快速隔离系统使之免受故障元件影响的功能方面有很大差别。

起初,互联网使用网络层的软件协议,在可能会经历严重损伤的网络上提供可靠的通信。因此Ethernet的原始误码管理功能主要用于检测、隔离和避免网络中的新漏洞,而不是用于单个系统的鲁棒性。系统可靠性通过网络元件的复制来实现。后来的性能增强则增加了标准化的误码捕捉和误码提醒机制,并以此简化网络管理。

RapidIO具有与Ethernet类似的备份、误码捕捉和误码提醒功能。PCIe支持有限的备份策略,因为它的传输层限于树状结构。PCIe非透明桥接(NTB)允许两个或多个树状结构进行通信,以实现1+1备份(也称为1∶1备份)。但是NTB很难拓展到采用N+M备份机制的系统。理论上多根I/O虚拟化(MRIOV)可以用来在PCIe系统中支持N+M备份,但是其中N+M的总数量不超过8。然而,由于MRIOV系统中的子树无法相互通信,从故障恢复可能要求系统中断运行来重新配置系统,以便隔离故障元件,并采用新的元件。

与PCIe和RapidIO相比,Ethernet的误码检测机制通常比较慢,因为Ethernet是针对全球范围内分布的网络设计的。PCIe和RapidIO都有误码检测和提醒机制,其时延要比Ethernet小得多。虽然PCIe和RapidIO都保证数据包的发送,但在误码条件下它们会弃包,以防止故障元件造成致命拥塞。

相反,RapidIO标准允许对误码做出特殊系统响应,如链路再学习。当误码发生时,系统会立即开始弃包,或者它会保留包,并允许拥塞发生。RapidIO使用“漏桶”式误码计数方法,并有两个可配置门限。危险门限能尽早提醒系统管理软件链路上正在发生误码。失效门限用于触发丢包以实现用户定义的误码率。RapidIO误码管理的灵活性保证了嵌入式系统设计人员不断变化的需求。

五、结语

Ethernet、PCIe和RapidIO是现在应用最为广泛的几种高速光纤总线技术,它们都基于相似的SerDes技术,SerDes技术不再是这些技术的差异点,而是它们使用可用带宽的方式。每种技术都有最适合的专门应用领域。

Ethernet最适合地理上分散的、具有长时延的网络。PCIe则能对单板上的分层总线结构提供最理想的支持。这两种技术都可用于板上、板间和设备间通信,而且在许多应用场合被同时用于同一系统。

RapidIO能将这两种互连的优势结合到单个互连中,并可显著节省功率和成本。RapidIO是嵌入式系统的最佳互连选择,具有与PCIe和Ethernet相似的功能,并具有其他互连技术无法复制的功能,如低时延、低抖动的系统事件分发;组合式链路层和网络层流量控制机制;可配置的误码检测和模糊拓扑路由可实现高效的备份、高可靠性和可用性;读/写和进程间通信消息语义的硬件实现。这些功能允许系统架构师创建性能更高、功耗更低并且更容易扩展的系统。

了解这几种常见高速光纤总线的差异性和优缺点可让我们更有针对性地对不同的工程应用做出最优化设计。

参考文献:

[1]IEEE 802.3-2008 Ethernet specification.2008.

[2]PCI Express Card Electromechanical Specification (Revision 1.0a).2003.

[3]RapidIO Interconnect Specification (Revision 2.1).2009.

[4]Sam Fuller. RapidIO : The Embedded System Interconnect[M]. 北京:电子工业出版社,2006.

[5]Trevor Hiatt,Devashish Paul,Barry Wood. RapidIO Gen2 Technology.www. rapidio.org,2009.

[6]Barry Wood. Comparing Ethernet and RapidIO. www. rapidio.org,2010.

[责任编辑王南山]