基于Vivado HLS的FPGA开发与应用研究

2016-01-11党宏社王晓倩

党宏社, 王 黎, 王晓倩

(1.陕西科技大学 电气与信息工程学院, 陕西 西安 710021; 2.浙江大学 控制科学与工程学系, 浙江 杭州 310000)

基于Vivado HLS的FPGA开发与应用研究

党宏社1, 王黎1, 王晓倩2

(1.陕西科技大学 电气与信息工程学院, 陕西 西安710021; 2.浙江大学 控制科学与工程学系, 浙江 杭州310000)

摘要:为在硬件中更快速地实现数字信号处理或图像处理算法,可使用Vivado HLS工具与Zynq系列的全可编程SoC进行FPGA的设计与开发.开发者能够借助它们直接使用C或C++语言进行FPGA的开发,相对于Verilog或VHDL设计而言,开发周期短、成本低。本文详细介绍了Vivado HLS工具的特点与应用等内容,并以“图像色调分离”和“循环编码器”两种不同类型的实例,描述了该工具的使用方法与设计技巧.

关键词:高层次综合; Vivado; FPGA

0引言

FPGA是以硬件描述语言Verilog或VHDL完成电路设计,并经过仿真、时序分析和综合,最终通过大量的基本逻辑门电路去实现复杂的数字逻

辑功能.FPGA以并行运算为主,与传统的PC单片机开发有很大的不同.造成FPGA的开发较难,与一般的程序设计思路有着很大的区别.

在FPGA内进行复杂的时序设计一般使用状态机进行开发,这需要花费较多的时间进行分析与设计.为了得到更好的时序等性能,还需要更多的时间去重复仿真与优化.若要将已有的PC算法程序移植到FPGA时,需要根据设计的逻辑去转换,费时费力.因此,若是有一种能够使用C或C++语言来进行开发FPGA的工具,将会给FPGA设计带来更高的效率,并能够充分利用已有的可靠软件程序,减少开发成本与时间[1].赛灵思公司开发出的Vivado软件是ISE的升级版,并且包含了高层次综合(HLS)工具,它能够以C、C++或System C直接进行设计,对其进行综合优化后即可生成相应的硬件描述语言,用于FPGA开发.

1Vivado HLS简介

Vivado设计套件,是FPGA厂商赛灵思公司2012年发布的FPGA集成设计环境.其中的HLS是极具创新的一个工具,是未来可编程逻辑器件设计的重要方法.

由于Verilog或VHDL等RTL设计语言与软件工程师的知识背景存在一定的差距,难以直接进行FPGA的开发与应用,这已经妨碍了FPGA应用技术的发展.而使用HLS能够让系统设计工程师使用All Programmable SoC实现软硬件的协同设计,大幅度缩短产品的开发与上市进程.HLS提出了一种全新的设计思路,更加注重FPGA设计的“系统级”建模.设计人员在充分理解了软件串行执行与硬件并行执行的特点后,能够大幅提高使用HLS进行FPGA开发的效率[2].

图1所示为Vivado HLS工具的一般开发流程.首先使用C或C++语言设计一个有具体功能的函数,以及一个用于描述期望设计行为的C测试平台.随后用C仿真器验证设计的功能是否满足要求.当设计的功能通过验证后,就可以通过Vivado HLS综合工具生成对应功能的RTL设计,生成的代码可以是Verilog或VHDL.得到 RTL 设计后即可使用Vivado内的仿真工具或Modelsim进行仿真,并进一步根据之前创建的 C 测试平台,验证设计的架构行为和功能[3].

图1 Vivado HLS开发流程

2HLS的功能

Vivado HLS有助于降低整个系统的功耗、物料成本,提高系统性能并加速设计生产力.下面将从Vivado HLS工具的几个特点进行介绍.

2.1加速FPGA设计

对于那些逻辑、时序要求较为宽松,时间紧迫的FPGA开发项目,或是已有成熟的C程序算法的FPGA移植项目,使用Vivado HLS工具进行设计都是不错的选择.

对一个新的开发项目,首先可以在Matlab中进行算法功能验证,当达到功能要求后,将算法代码转换为C、C++代码,然后在Vivado HLS工具中再次进行功能验证和最后的综合优化步骤.对综合优化结果进行分析并修改优化指令或程序结构,直到综合结果能够满足设计要求为止.

使用HLS工具进行的设计一般都用于Matlab和C模型的构建,真正使用HLS工具本身的时间是相对较少的.所以对于已有现成C程序算法的移植项目,只需对程序本身进行必要的修改或不用修改就可以直接进行最后的综合优化步骤.

2.2数据处理

在Vivado HLS中能够实现各种不同的数据处理,包括普通的数值计算、图像处理、系统控制以及网络等方面的数据处理 .

2.2.1任意精度数据

使用任意精度设计,能够解决C语言设计FPGA程序的数据类型问题.在C语言中的浮点数包括单精度浮点和双精度浮点类型,分别占用32位和64位数据空间,以及其它整形类数据都会占用整数字节的数据空间(8位、16位、32位).对于不是占用整数字节的数据,如7位、24位或128位数据,在C语言中是没有对应的数据类型的.若不进行数据类型定义而直接在RTL内综合,就会自动使用整数字节的寄存器型或线型数据,或是根本不能进行数据定义(128位数据),这样将不能充分有效的利用FPGA内的逻辑资源.

使用Vivado HLS内的任意精度类型定义数据,可以根据需要指定每一个整型或浮点数据的位数,HLS软件内的综合工具会进行识别,并按指定的位数去定义最后综合在FPGA内部的数据位数[4].如下的两句声明程序,C_UINT7与C_UINT19分别能够用来定义7位和19位的整形数据.

typedef ap_uint<7> C_UINT7;

typedef ap_uint<19> C_UINT19;

2.2.2图像处理

OpenCV是一个开源发行的跨平台计算机视觉库,可以运行在多种计算机操作系统上[5,6].它具有轻量级而高效的特点,由一系列 C 函数和少量 C++ 类构成,实现了图像处理和计算机视觉方面的很多通用算法,能够应用于人脸识别、运动跟踪、结构分析等多种领域.

HLS工具内包含有专用的OpenCV库函数,包括了大部分计算机版本OpenCV的库函数功能.对于在计算机上已经实现的图像处理程序只需稍加修改即可在FPGA内实现对应功能的图像处理算法.赛灵思的OpenCV库为用Vivado HLS对设计进行了深度优化[7],这些库能提供1080p分辨率的像素处理功能,并且有着很强的并行处理性能.

2.2.3控制及网络处理

控制算法一般都有较高的控制周期要求,网络协议则有较复杂的逻辑,使用硬件描述语言Verilog或VHDL进行编程[8,9]难度非常大.而对于控制或网络数据处理一般都有较可靠的软件实现算法,使用Vivado HLS工具不需修改或稍加修改就可以将其直接进行综合并应用在FPGA内.所以Vivado HLS工具十分适合对有现成算法的功能进行设计,并有巨大的优势.

2.3IP封装

Vivado HLS编译器流程的最后两步就是RTL实现和IP封装.这是Vivado HLS编译器中能够自动实现的两步,赛灵思产品针对组合中不同器件的RTL创建优化细节内置在编译器中,不需要用户具备RTL方面的知识.Vivado HLS编译器的输出自动封装为IP-XACT等其它赛灵思工具能直接使用的格式,因此无需进行其它操作,就可在Vivado或ISE中使用HLS生成的IP核[10].

总之,我们可以使用HLS完成多种设计,包括电机控制、矩阵数据处理、图像处理等各个方面.使用HLS设计套件生成的IP核可以直接在FPGA内调用,为快速实现项目开发提供有力保障.

3HLS应用开发

下面通过2个具体的实例介绍如何使用Vivado HLS进行FPGA的设计与开发.

3.1开发界面

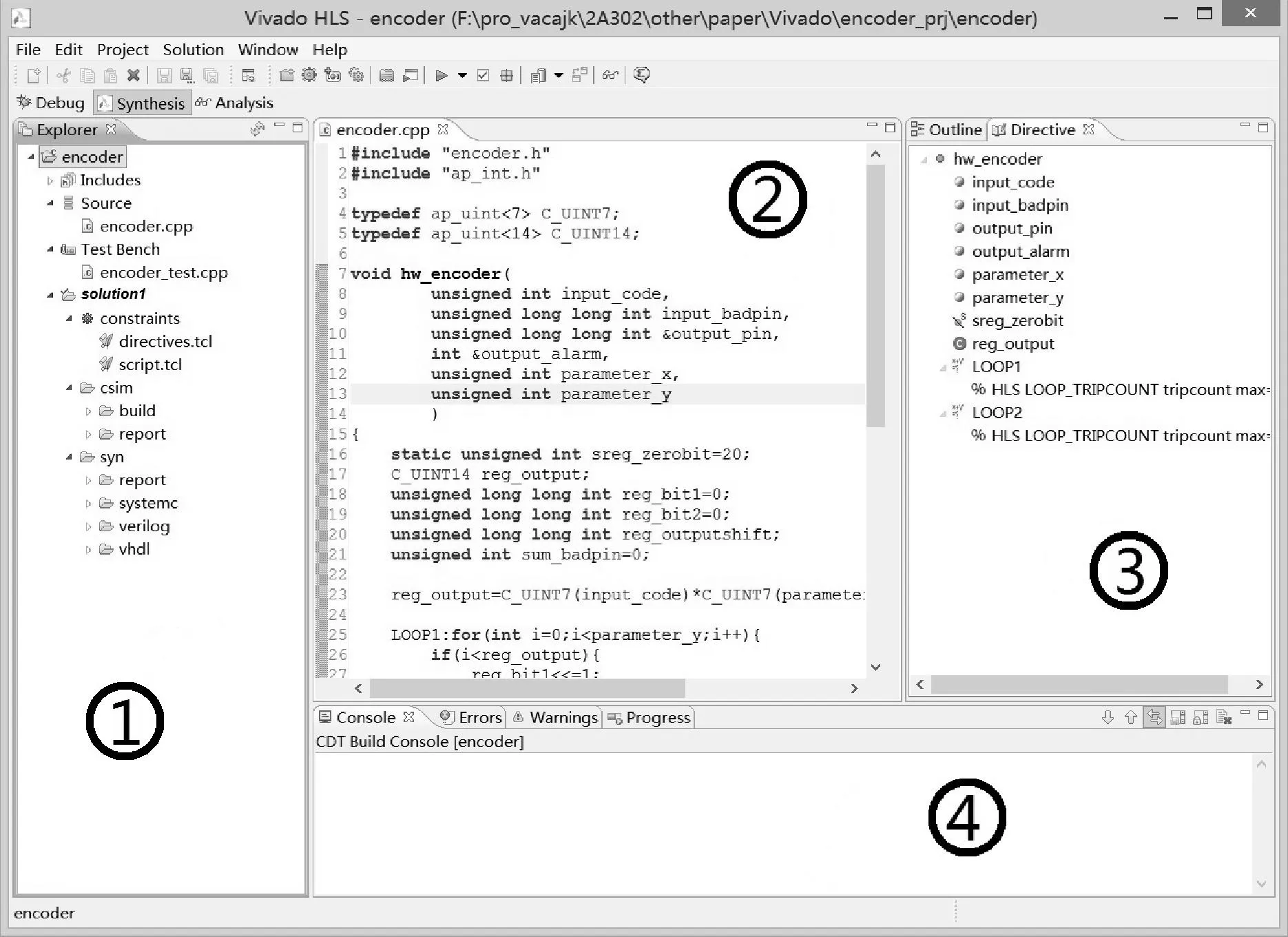

Vivado HLS的基本开发流程如简介中的图1所示,在清楚开发流程后就可使用该工具按步骤进行FPGA开发.Vivado HLS的软件界面如图2,最左边①为设计中用到的库、源代码、测试平台以及解决方案等文件的目录;中间②为修改代码、查看相关综合结果报告的界面;最右边③为综合时的优化指令目录;最下边④可以显示相关调试信息的界面.

图2 Vivado HLS软件界面

首先在源代码目录里加入用于RTL综合的目标功能函数,作为Top Function,然后加入用于对比验证的功能函数,并编写C测试平台用来进行后续的功能验证.使用C仿真器运行程序,对两个功能函数的运行结果进行对比,若结果相同即可进行后续的综合步骤.综合后可根据设计的指标加入优化指令,对综合方法进行优化、约束并再次进行综合,直到相关指标达到设计要求.此时可以进行C/RTL联合仿真,使用C测试平台去仿真验证综合结果.最后将综合后的RTL设计打包为IP核,作为专用的功能模块以备使用.

3.2图像处理开发实例

Vivado HLS能够借助OpenCV图像处理函数库进行多种图像处理算法的开发.下面介绍如何使用该工具设计一个具有图像色调分离功能的模块.

3.2.1色调分离原理

色调分离是指一幅图像原本是由紧紧相邻的渐变色阶构成,被数种突然的颜色转变所代替.这一种突然的转变,亦称作“跳阶”. 基本效果如图3所示,(a)是原始图像,(b)为色调分离后的图像,可以看到色调分离后图像的色调发生了跳变,云彩处的变化较为明显.

(a)原始图像

(b)色调分离后的图像图3 色调分离效果

为了实现色调分离,首先需要了解色调分离的图像处理原理.图4为色调分离前和分离后的图像色阶直方图.可以看到正是因为色阶直方图由本身的看似连续变化转变为了分离的形式,所以才会产生图3中的色调跳变现象.还有诸如色阶拉伸或是曲线调整等方法,也会产生不均匀的色调分离效果.

(a)分离前 (b)分离后图4 色调分离前后的图像直方图

色调分离作为一种简单的减少图像色阶数的处理方法,可以应用在印刷厂原始胶片生成、海报图片制作和图像分割[11]等方面.

3.2.2开发步骤

由前面了解到色调分离后的图像的各个色阶值被平均分配到一个确定的色阶值上,根据分配的对应关系,可以编写程序建立对应的查找表.这样就能够根据原始图像的像素灰度值和查找表直接确定新的灰度值,并最终得到色调分离后的图像.

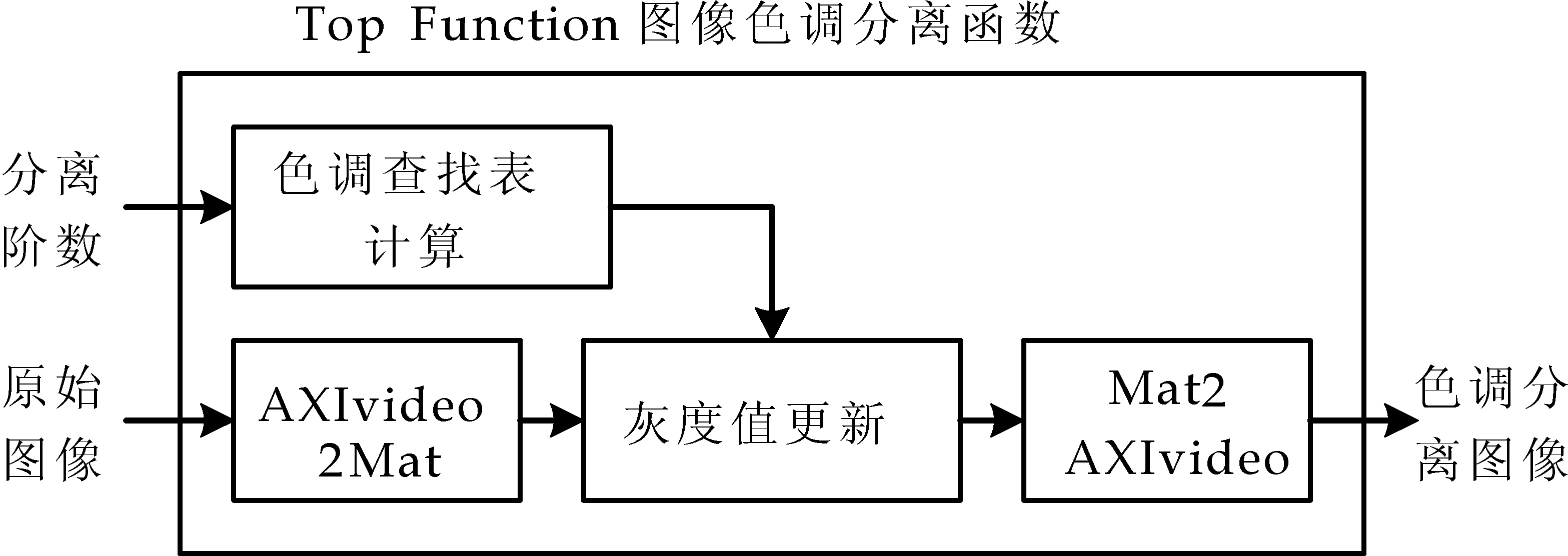

在HLS中设计的软件流程如图5所示.首先根据色调分离参数计算出色调分离的查找表,这样就能由原始图像的像素灰度值直接得到处理后的灰度值.FPGA内嵌的ARM处理器提供图像数据至本模块,由AXI图像数据流转换为OpenCV库函数能够处理的Mat类型.然后对像素点的三个颜色通道的灰度值分别进行查表,得到结果后再次转换为AXI图像数据流并输出至ARM处理器.

图5 色调分离处理流程

按照设计的软件流程编写该图像色调分离模块的程序,作为RTL综合的目标功能函数.同时编写测试平台程序,对该模块进行C功能验证.当功能验证结果正确后即可进行综合与优化.综合功能是HLS工具自行完成的,根据实际要求与不断尝试修改,优化指令能够尽量使设计达到理想要求.在本设计当中主要使用了流水线(Pipeline)和数据流(Dataflow)两种优化方式,有助于提高系统处理图像的速度.

3.2.3综合结果

综合后的时序结果如图6所示.第5和第7行分别表示色调分离模块当中的计算查找表和灰度值更新的步骤,第6、8行为AXI图像数据流和Mat数据类型的转换步骤.每行后面的方块代表该处理步骤在整个模块处理当中的处理顺序和占用的时间比例.

图6 时序分析

同时可以观察到各个步骤所占用的时序是从上至下、从左至右的,这保证了综合后的设计是在最小处理周期情况下有最小处理间隔,而且处理间隔小于延时,即综合后的模块是能够实现流水线处理的[12].

本设计的系统时钟为150 MHz,能够处理最大为1 080 p分辨率的图像.每41.6 ms左右就能处理一张,每间隔13.87 ms就能输入一张,同一时刻可以有3张同样分辨率的图象在进行色调分离并行处理.

3.3循环编码器开发实例

要求设计一种编码器,有8位输入引脚(能以二进制编码方式输入10~60)和30~60个输出引脚.输出端引脚置位高电平的数量是根据输入端读到数值来确定的,如输入上限值配置为30,输出引脚个数配置为60,输入一个数值1则2个引脚要输出高电平,输入数值为30则全部输出要为高.输出的引脚有1~60的序号,根据输出高电平的个数,从起始第1位开始输出高电平.每次调用此模块,起始位会依次向后循环移动,若起始位到达最高位,则下一次会回到第1位.至此,这种循环编码器的功能已基本清楚.

设计中还有一个要求,当编码器后方的设备对编码器输出进行接收的某一引脚发生故障时,会有对应的一个信号反馈并输入到该编码器内.编码器进行编码时需要跳过该故障位,并将输出推后1位.当同时有3个以上的故障信号时,编码器会输出故障信号并取消编码功能.

这个设计若使用C语言进行设计会十分方便,都是一些位操作的语句,而使用Verilog设计就需要考虑一些编码、数据位数等问题.本设计应用的场合不是高速环境,使用Vivado HLS工具进行设计能够满足要求.表1为按要求功能设计出的模块性能,该模块工作频率为100 MHz,使用8位输入情况下的处理周期约为21微秒(210个时钟周期).该设计能够达到系统实时性的要求,更重要的是设计周期较短,只需一天就可完成这种循环编码器的设计.

表1 编码器性能

注:时钟频率为100 MHz

4结束语

介绍并展示了Vivado HLS工具的优势及其应用领域,可通过本文大致了解该工具的使用方法和注意事项.该工具对于不了解硬件设计语言的软件工程师,亦或是FPGA开发工程师都是一种新的FPGA设计思路.在Vivado HLS工具中通过C设计、综合与优化,能够加速FPGA设计,为项目开发节省宝贵的时间.

参考文献

[1] 丛秋波.Vivado设计套件将可编程系统集成度和实施速度提升4倍[J].电子设计技术,2012,19(6):22-24.

[2] 何宾.Xilinx All Programmable Zynq-7000 SoC设计指南[M].北京:清华大学出版社,2013.

[3] 21ic官方微博.赛灵思Vivado 开启“All Programmable”新征程[EB/OL].http://www.21ic.com/wz/CRXDQWHFA/20120501/20120501.htm,2014-08-15.

[4] James Hrica.利用赛灵思Vivado HLS实现浮点设计[J].今日电子,2013,21(1):34-38.

[5] 方玫,喻擎苍,李华强.C++Builder下基于OpenCV的数字图像处理[J].计算机工程与设计,2008,29(4):882-884.

[6] 郭晖,陈光.基于OpenCV的视频图像处理应用研究[J].微型机与应用,2010,29(21):14-16,20.

[7] Xilinx Inc.Accelerating OpenCV applications with zynq-7000 all programmable SoC using Vivado HLS video libraries[EB/OL].http://www.xilinx.com/support/documentation/application_notes/xapp1167.pdf,2014-08-15.

[8] 白瑞林,江吕锋,王建.基于FPGA的模糊自整定PID控制器的研究[J].仪器仪表学报,2005,26(8):833-837.

[9] 马文超,张涛.一种基于FPGA的以太网高速传输平台[J].计算机工程,2012,38(1):242-244.

[10] Xilinx Inc.Vivado design suite tutorial high-level synthesis[EB/OL].http://www.xilinx.com/support/documentation/sw_manuals/xilinx2012_4/ug871-vivado-high-level-synthesis-tutorial.pdf,2014-08-15.

[11] 张馨,刘双喜,郑文秀,等.基于色调分离的棉花异性纤维分割[J].中国棉花加工,2009,29(4):35-37,40.

[12] Xilinx Inc.Vivado design suite user guide high-level synthesis[EB/OL].http://www.xilinx.com/support/documentation/sw_manuals/xilinx2012_4/ug902-vivado-high-level-synthesis.pdf,2014-08-15.

Development and application of FPGA based on Vivado HLS

DANG Hong-she1, WANG Li1, WANG Xiao-qian2

(1.College of Electrical and Information Engineering, Shaanxi University of Science & Technology, Xi′an 710021, China; 2.Department of Science and Engineering, Zhejiang University, Hangzhou 310000, China)

Abstract:In order to more rapid implementation of digital signal processing and image processing algorithm in hardware design.Vivado High-Level Synthesis (HLS) design tools can be used in the design and development of Zynq All programmable with FPGA.HLS can transform a C or C++ design specification into a Register Transfer Level implementation which can be synthesized into a Xilinx FPGA.Compared with Veirlog or VHDL design,this tool will reduce development cycles and costs of FPGA.This paper describes the characteristics and applications of HLS in detail.With the examples of image posterization and loop encoder, we can learn the design method and skills.

Key words:high level synthesis; Vivado; FPGA

中图分类号:TN47

文献标志码:A

文章编号:1000-5811(2015)01-0155-05

作者简介:党宏社(1962-),男,陕西武功人,教授,博士,研究方向:工业过程智能控制、多源信息融合、数字图像处理

基金项目:西安市科技计划项目(NC10015)

收稿日期:*2014-09-26