雷达监控分系统通用自测平台设计∗

2016-01-10

(中国电子科技集团公司第三十八研究所,安徽合肥230088)

0 引言

监控分系统是整部雷达控制和状态监控的枢纽,既要解析、转发、执行来自终端人机界面的控制和查询命令,同时又要采集、分析、上报整部雷达的状态给终端分系统[1]。监控分系统的功能和其他分系统联系非常紧密,因此测试时需要其他分系统的配合,很多问题在分系统调试阶段无法充分暴露出来,只能在整机联调阶段发现问题,此时故障定位和解决的难度都要比分系统调试阶段大上很多。针对这种情况,设计监控分系统自测平台,通过模拟其他分系统与监控分系统之间的通信,达到检验监控分系统各项功能是否正常的目的。

1 总体方案设计

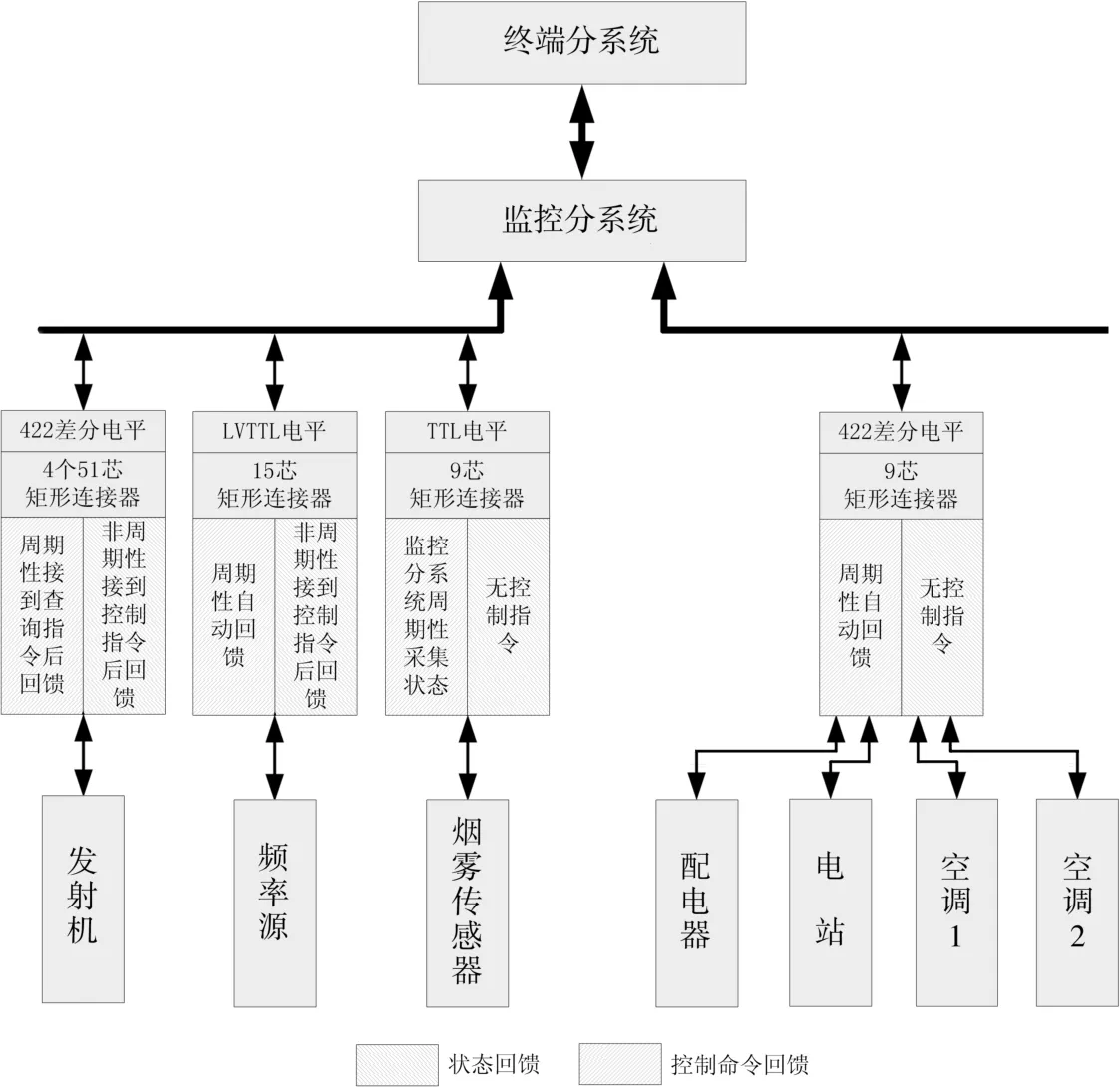

监控分系统作为一个庞大而复杂的协议转换器和执行器,具有接口电平多、通信线路多、任务性质多的特点。从控制和监控的角度看,雷达各分系统之间的关系如图1所示(与监控分系统未发生联系的分系统在图中未标出)。在设计自测平台之前,必须充分考虑这些因素,选择合理的方案。

监控分系统与其他分系统之间的接口电平有LVTTL、TTL和422三种电平,这就需要自测平台能够提供电平转换电路,使各种形式的电平转换为FPGA(Field-Programmable Gate Array,现场可编程门阵列)所能接受的3.3 V电平[2]。针对接口电平多的特点,设计专用的电平转换电路,将不同电平的信号转换成统一的信号,便于后续的处理。

图1 雷达各分系统之间关系

监控分系统需要监控的状态信息以及执行的命令数量众多,每一项都需要占用一条独立的通信线路,这样监控分系统与其他分系统之间就会有大量的通信线路。针对通信线路多的特点,如果直接使用计算机模块和FPGA芯片的接口进行通信,会出现接口资源不足的矛盾。自测平台采用210芯接口来扩展计算机模块和FPGA芯片的接口资源,所有的通信线路都连接在210芯接口的引脚上,这些引脚再和计算机模块及FPGA芯片的接口相连,根据“分时复用”的原则[3],不同的时刻向不同的引脚发送数据,或从引脚接收数据。

任务性质多主要指任务在时间周期上的不同。有些任务是周期性的,有些是非周期性的;有些数据是主动上报给监控分系统的,有些需要接收到监控分系统的询问信号才回馈相应的状态信息。由于使用了计算机模块和FPGA芯片作为主控器件,可以灵活地对器件的功能进行编程设计,因此任务性质不同的问题也很容易得到解决。

综合以上分析,监控分系统自测平台由硬件和软件两部分组成。软件驻留在计算机模块中,负责解析用户操作、组织数据和处理数据。硬件电路一方面为软件提供运行平台,另一方面将计算机接收和发送的数据转换为监控分系统能够识别的各种电平信号,同时根据计算机的指令分时调度硬件资源。

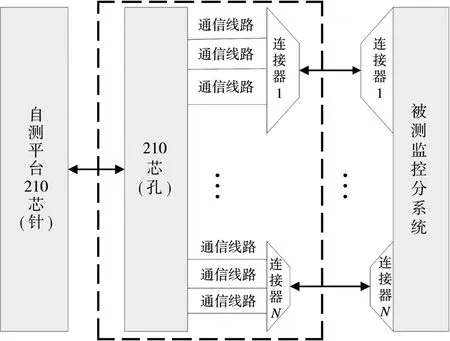

当前不同型号雷达监控分系统采用的接口不一,主要有210芯、100芯、双100芯、CPCI(Compact Peripheral Component Interconnect,紧凑型PCI)、定制等接口类型[4]。为了让自测平台能够适应不同的硬件接口,自测平台的210芯并不是和其他插件一样直接挂在总线上,而是另外增加一个210芯插座,该210芯插座和自测平台的210芯接口相对应(比如自测平台210芯是针,则该210芯插座就应该是孔)。在210芯插座另外一面的针上焊接所有的通信线路,通信线路的另外一端连接各种连接器,通过连接器和被测监控分系统进行通信。硬件连接示意图如图2所示。对于不同形式的硬件接口,只需更换图中虚线框中的部分,即可实现对各种接口的自适应连接。

2 软件设计

2.1 模块划分

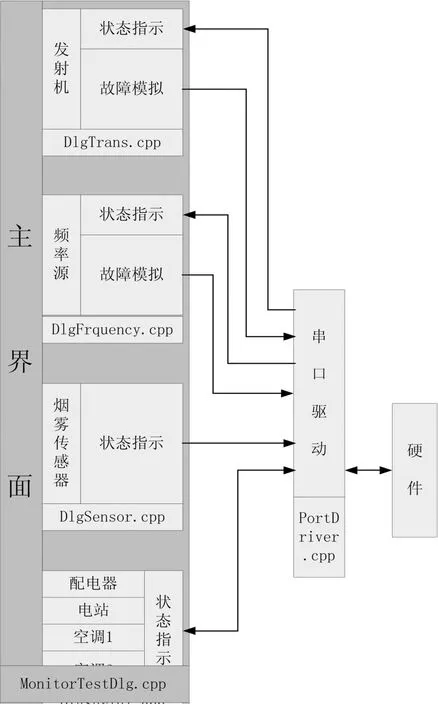

上位机软件基于MFC(Microsoft Foundation Classes)开发。根据需要,把软件系统划分为6个模块,对应的源文件分别是Monitor Test Dlg.cpp、Dlg Trans.cpp、DlgFrquency.cpp、DlgSensor.cpp、DlgSerial.cpp和PortDriver.cpp。

图2 自测平台硬件接口自适应连接示意图

Monitor Test Dlg.cpp是上位机软件的主界面,在系统启动时负责对系统参数进行初始化设定、加载串口驱动和其他子模块,随后开启定时器,驱动串口工作。

Dlg Trans.cpp对应的是发射机分系统,包含模拟发射机各项功能正常与否的函数,同时还要读取终端分系统下发的开关机、复位等指令,根据读取到的指令在上位机界面上作相应的指示。

Dlg Frquency.cpp对应的是频率源分系统,和Dlg Trans.cpp类似,包含模拟频率源各项功能正常与否的函数,同时还要读取终端分系统下发的开关机指令,根据读取到的指令在上位机界面上作相应的指示。

DlgSensor.cpp对应的是烟雾传感器,只向监控发送代表当前是否存在烟雾的指令。

DlgSerial.cpp对应的是配电器、电站、空调1和空调2四个分系统,因为这四个分系统和监控分系统的通信方式相同,功能单一,因此合并成一个模块,以简化设计。该模块根据每收到一次终端的查询指令,相应的计数值就会加1,只要上位机界面上的数字在不断地累加,就说明该分系统和监控通信正常。

PortDriver.cpp是上位机软件的核心模块,负责上位机软件和硬件之间的数据交互,所有的数据都要经过串口驱动进行读和写。串口驱动的另外一项重要功能是对需要发送的数据按协议进行打包,对接收的数据按协议进行解析。

图3是各模块之间的相互关系。

图3 各模块之间的相互关系

2.2 程序流程

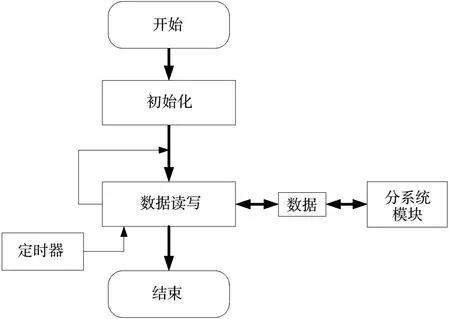

主程序启动后首先加载串口驱动,串口驱动要对端口和数据进行初始化。由于上位机主界面和各子模块的界面是分开设计的,因此主程序还要加载各子模块的界面。界面加载完成后,主程序启动一个定时器,在定时器的驱动下,串口驱动有周期性地对各个端口进行读写操作,将需要发送的数据发送给监控,然后读取端口接收到的数据。定时器只有在主程序关闭时才会终止运行。各分系统模块会把用户的操作转换成0和1(0代表故障,1代表正常)记录在结构体中,交给串口驱动进行处理;另外还要根据串口驱动接收的数据在界面上作相应的指示。图4是上位机软件的程序流程图。

3 硬件设计

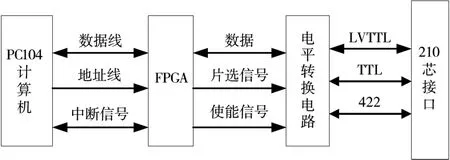

根据总体设计方案,硬件电路由四部分组成:计算机、FPGA、电平转换电路和210芯接口。下面简要介绍各模块的功能。

图4 上位机软件的程序流程图

计算机选用PC104嵌入式计算机模块,该计算机模块被广泛应用在各种型号的雷达中。计算机模块将自身的地址线、数据线和中断信号提供给FPGA使用,所有的数据都从计算机的串口进出。数据线和中断信号是双向流动的,便于计算机和FPGA之间的交互。

FPGA芯片选用EPF10K50RI240-4,该型号芯片成本较低,且能满足设计需要。FPGA负责对计算机信号进行译码,根据计算机指令产生不同的片选信号和使能信号,使数据根据时序从不同的端口输入和输出,从而充分利用计算机有限的IO资源,达到“分时复用”的效果。FPGA还起到缓冲器的作用,把不同波特率的数据转换成计算机串口能够识别的波特率[5]。

电平转换电路主要由各种驱动芯片组成,如162244、163244、164245,实 现 LVTTL、TTL 和3.3 V电平之间的转换以及信号放大等功能。由于422属于差分信号,因此还需要差分信号转换芯片。

电平转换之后的信号送给210芯接口,210芯接口是直接和监控分系统打交道的模块,为每个监控事件提供一个硬件通道。

图5是硬件电路的示意图。

图5 硬件电路示意图

4 结束语

监控分系统自测平台软、硬件架构简捷清晰,采用低成本设计,硬件具有通用性,只需对软件和FPGA程序进行重新设计,即可应用到其他型号雷达的测试中。而且能自适应采用不同硬件接口的监控分系统。这种通用性的设计能够加快雷达监控分系统自测平台的开发,为雷达批量生产提供快速、准确的测试方案。

[1]谢东辉,齐伟民.基于Nios II片上可编程系统(SOPC)实现的雷达监控系统[J].中国科学院研究生院学报,2010,27(1):63-69.

[2]张鹏南,孙宇,夏洪洋.基于Quartus II的VHDL数字系统设计入门与应用案例[M].北京:电子工业出版社,2012:18-19.

[3]李清,张彼德,郭筱瑛,等.分时复用控制多路输出开关电源[J].电测与仪表,2014,51(20):109-115.

[4]钟志华.一种通用雷达自动化测试设备的研究及其应用[D].哈尔滨:哈尔滨工业大学,2011.

[5]吴越,严济鸿,何子述.基于FPGA的多通道高速数据采集系统[J].雷达科学与技术,2012,10(6):671-676.WU Yue,YAN Jihong,HE Zishu.Multichannel High-Speed Data Acquisition System Based on FPGA and USB 2.0[J].Radar Science and Technology,2012,10(6):671-676.(in Chinese)