基于FPGA的正交信号发生器设计

2015-12-28杨峰,文枰

基于FPGA的正交信号发生器设计

杨峰1,文枰2

(1.四川文理学院国有资产管理处,四川达州635000;

2.重庆大学光电工程学院,重庆沙坪坝400030)

摘要:根据直接数字频率合成(DDS)技术,设计了基于FPGA的正交信号发生器,以用于双通道微弱信号相关检测电路中.首先介绍了DDS技术的基本原理;其次采用硬件描述语言编写各个模块的代码,并对其进行功能仿真和验证;然后对各个模块进行硬件电路设计;最后对设计的正交信号发生器进行了实验测试.测试结果表明:正交信号发生器的输出信号的频率特性和相位特性具有很高的稳定性,能够满足相关检测电路的要求.

关键词:正交信号;直接数字频率合成;FPGA

收稿日期:2015-03-21

基金项目:四川文理学院2014年度青年启动项目“GMR生物传感器专用数字锁相检测电路设计”(2014Z006Q)

作者简介:杨峰(1986— ),男,四川通江人.硕士,主要从事仪器科学与技术研究.

中图分类号:TN911文献标志码:A

0引言

双通道微弱信号相关检测电路需要两路相位差为90°的正弦信号(正交信号)作为参考信号.[1]由相关检测理论可知,正交参考信号的性能(如信号相位的稳定性)将直接决定微弱信号检测的质量.

有以下几种方法来产生正交信号:1)采用专用信号发生器产生正交信号.这种方法的缺点是专用信号发生器体积较大、价格贵和不易携带等,通常只适合于在实验室做研究使用;2)采用专门芯片(如AD9850)搭建电路来产生正交信号.这种方法的缺点是:一旦电路设计完成以后,就很难再根据实际需要对输出信号的频率、相位和幅度等参数进行调节;3)采用直接数字频率合成(DDS,Direct Digital Synthesis)技术来实现.

直接数字频率合成(DDS)技术[2]是一种全数字的频率合成技术,它在信号的相对带宽、频率转换时间、相位连续性、高分辨率以及集成化等一系列性能指标方面都优于传统的频率合成技术.

1直接数字频率合成(DDS)技术的原理

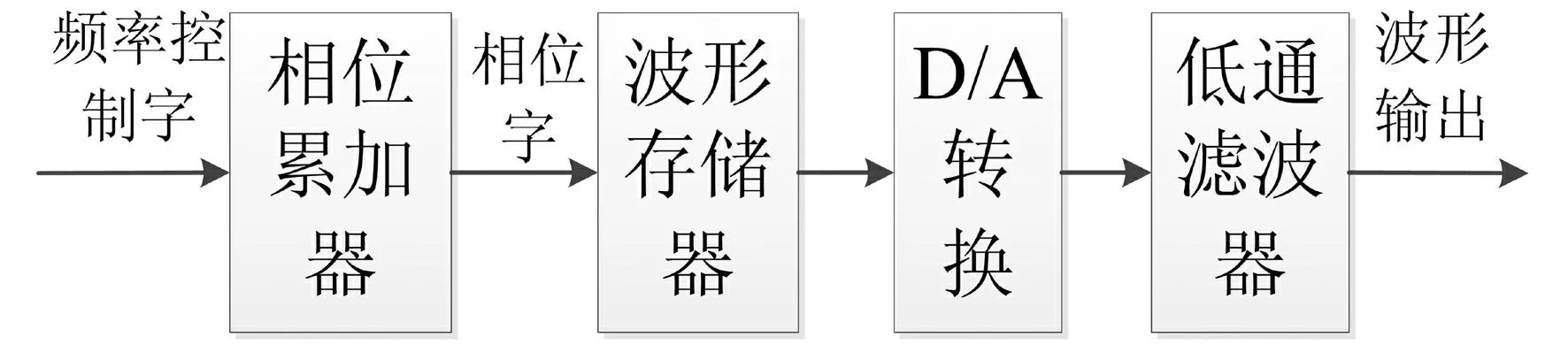

直接数字频率(DDS)技术以奈奎斯特采样定理为基础.[3]一般来说,DDS系统由相位累加器、波形存储器、数模转换器和滤波器等部分组成.[4]在系统时钟的驱动下,相位累加器将频率控制字线性累加,得到的相位字对波形存储器寻址,使之输出与相位字相对应的幅度值,在经过数模(D/A)转换器将其转换成相应的阶梯波后,再用低通滤波器对阶梯波进行平滑处理,就得到所需的连续波形.图1为DDS的原理图.

图1 DDS原理框图

DDS的输出信号的频率fout是系统时钟频率fclk、相位累加器的位数N和频率控制字K的函数,数学关系式为:

(1)

其频率分辨率为:

(2)

由上式可见,当系统时钟频率fclk一定时,相位累加器的位数N越大,DDS输出信号的频率分辨率就越高.

1.1相位累加器

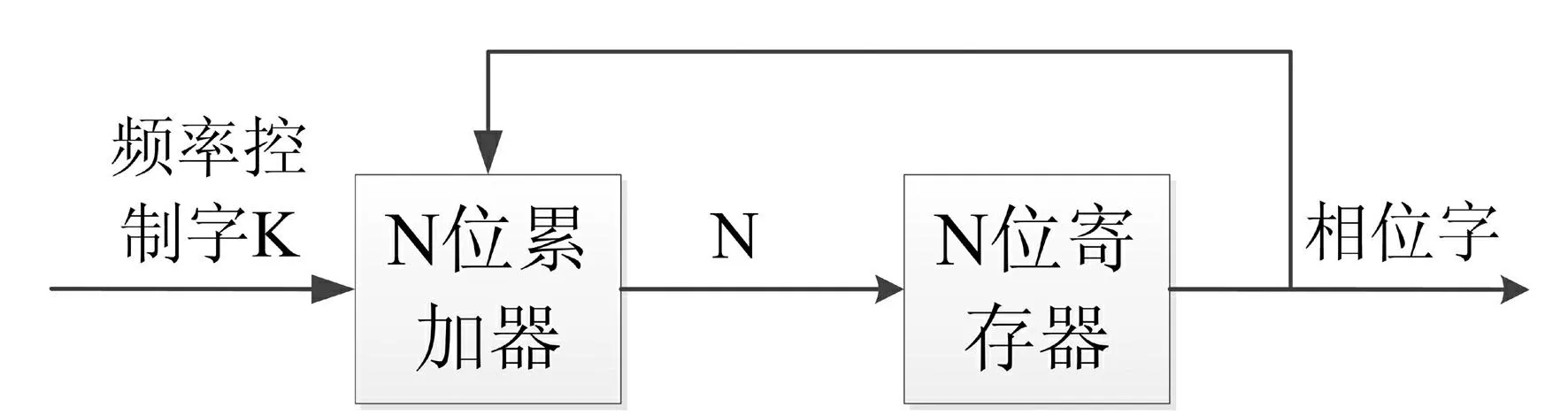

相位累加器是DDS的重要组成模块,由N位加法器和N位累加寄存器构成.在系统时钟的作用下,相位累加器将频率控制字进行线性的累加.当相位累加器加满时便产生一次溢出.相位累加器的溢出频率就是DDS输出信号的频率,而相位累加器的输出数据是合成信号的相位.图2为相位累加器的原理图.

图2 相位累加器原理图

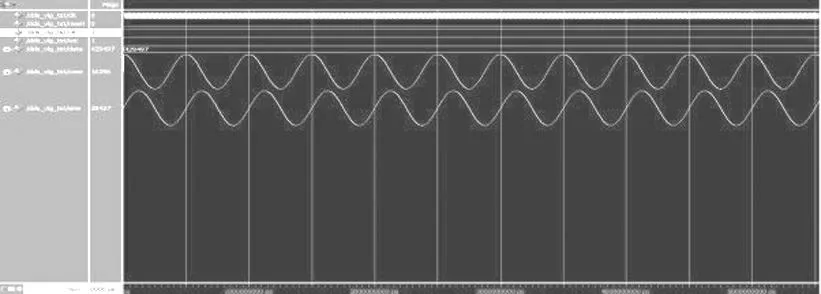

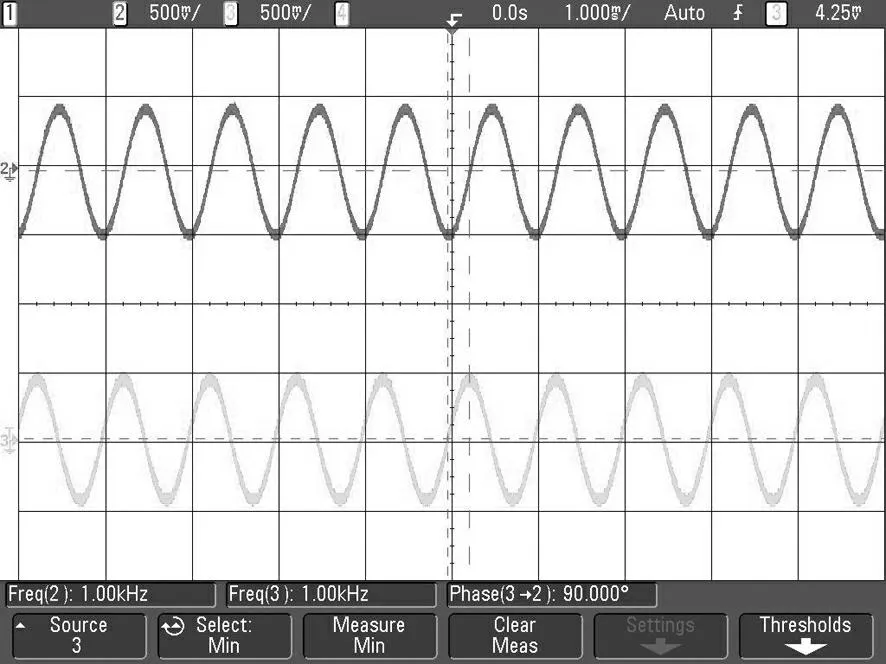

由DDS的原理可知,为了提高DDS输出信号的频率分辨率,可以采用位宽较大的相位累加器,也就是增大N值.[5]但是考虑到ROM查找表的容量限制,地址的位宽A(A 1.2波形存储器 波形存储器是用来存储一个完整周期的正弦波和余弦波的相位序列以及与其相对应的幅度量化序列.用相位累加器输出的相位字的高A位作为波形存储器的输入地址,就可以把波形存储器中相应的波形幅度值读取出来,从而实现相位字到信号幅度的转换. 2DDS的硬件电路实现 正交信号发生器主要包括相位累加器、波形存储器、数模转换器和低通滤波器等几个模块组成.本设计中的相位累加器模块、波形存储器模块以及数模转换器控制模块采用FPGA芯片实现,选用Altera公司的型号为EP2C8Q208C8的FPGA芯片,所有代码采用Verilog HDL编写.[7-8] 2.1相位累加器的FPGA实现 相位累加器的位宽N取32位,频率控制字K的位宽也取32位,ROM查找表的地址位宽A取10位.FPGA系统时钟频率设计为20MHZ,如要得到频率为1000HZ的输出信号,就可以根据公式(1)计算出频率控制字: K=214748.3648 为了节省FPGA资源,我们采用整数运算,因此将频率控制字取整为: K=214748 可以计算,由频率控制字取整造成的误差很小,基本可以忽略不计. 用Verilog HDL编写相位累加器的代码,在Quartus II软件中编译综合.图3为相位累加器的RTL视图. 图3 相位累加器的RTL视图 2.2波形存储器的FPGA实现 首先利用Matlab软件生成正弦、余弦波形量化数据,并用Quartus II软件中的Memory Initialization File工具生成ROM模块中存储的波形数据文件(*.mif文件);然后再用Quartus II中的 Mega Wizard Plug-In Manager工具生成一个ROM模块,选择其深度为1024,位宽为16位,建立两个波形存储器(一个正弦一个余弦).图4为其RTL视图. 图4 ROM查找表的RTL视图 2.4低通滤波器电路设计 从D/A转换器输出的信号中还含有高频谐波及杂散噪声成分,为了得到纯净的输出波形,采用低通滤波器对其进行滤波处理.本设计中选用AD公司生产的AD820芯片设计二阶有源低通滤波器. 3仿真和实验结果 为了验证设计的效果,采用ModelSim软件对设计的DDS模块进行功能仿真.图5为仿真结果.由仿真结果清晰可见,两路信号(一路为正弦信号,一路为余弦信号)的频率和相位都很好的达到了设计要求. 图5 功能仿真结果 功能仿真验证设计的正确性后,将Verilog HDL代码编译后的*.sof文件烧录到FPGA芯片中,并级联各个模块电路,然后对系统电路进行整体测试. 采用Agilent公司型号为DSO6014A的数字存储示波器观察正交信号发生器的输出信号波形.图6为示波器观察结果. 图6 示波器观察结果 由实验结果显示,设计的正交信号发生器输出的两路正弦信号的频率都为1KHZ,且两路正弦信号的相位差保持为90°. 参考文献: [1] 高晋占.微弱信号检测[M].北京:清华学出版社,2004:154-196. [2] A. L. Bramble.Directdigitalfrequencysynthesis[J].in Proc.35th Annu. Preq. Contr. Symp., USERACOM (Ft. Monmouth,NJ), May 1981:406-414. [3] 白居宪. 直接数字频率合成[M].西安:西安通大学出版社,2006:5-10. [4] 陈小荣.基于DDS的正弦信号发生器设计[J].仪器仪表用户,2006(4):98-100. [5] Pau1 O’ Leary, Franeo Maloberti.ADirectDigitalSynthesizerwithImprovedSpectralPerformance[J].IEEE Trans on Communications, vol.39,July 1991:1046-1048. [6] Chao Huang, Lixiang Ren.AsystematicfrequencyplanningmethodinDirectDigitalSynthesizer(DDS)Design[J].Wireless Communications & Signal Processing(WCPS 2009),Nanjing,China,vol.1, pp.1-4, November 2009. [7] 夏雨闻. Verilog数字系统设计教程[M]. 北京:北京航空航天大学出版社, 2008:1-86. [8] 云创工作室.Verilog HDL程序设计与实践[M].北京:人民邮电出版社,2009:100-200. [责任编辑范藻] The Design of Orthogonal Signal Generator Based on FPGA YANG Feng1, WEN Ping2 (1.State-owned Asset Management Department of Sichuan University of Arts and Sciences, Dazhou Sichuan 635000; 2.Optoelectronic Engineering School of Chongqing University, Chongqing 400030, China) Abstract:According to the direct digital frequency synthesis technology, an orthogonal signal generator is designed by using FPGA chip. The purpose is to use it for dual channel weak signal correlated detection circuit. First, the basic principle of DDS technology is introduced; second, the code of each module is edit by using hardware language, and did the functional simulation; then, designed the hardware circuit of each module; finally, the experimental test has been done for the orthogonal signal generator. Experimental results show that the frequency characteristic and phase characteristic of the orthogonal signal generator's output signal has very high stability and meets the requirements of the correlated detection circuit. Key words:orthogonal signal; direct digital frequency synthesis; FPGA