基于FPGA的通用型FIR数字滤波器的研究与设计

2015-12-26张震

摘要:FIR数字滤波器的实现是基于加法器和乘法器,通过延迟将输入信号与固定的抽头系数相乘累加得到滤波结果,其中滤波系数是已知的数值,当我们需要一个固定阶数系数的值不固定时,我们就需要将滤波的系数通过外部输入的方式再与输入信号相乘。对于FIR数字滤波器的通用型的研究是基于传统的串行FIR数字滤波器的结构进行改造,使用VerilogHDL语言在QuartusII和Modelsim软件里面进行设计和仿真。结果表明基于FPGA的通用FIR数字滤波器的设计是可行的。

关键词:加法器;乘法器;串行FIR数字滤波器;串行结构;通用型FIR数字滤波器

中图分类号:TN713+.7

文献标识码:A

DOI:10.3969/j.issn.1003-6970.2015.06.023

本文著录格式:张震,基于FPGA的通用型FIR数字滤波器的研究与设计叮].软件,2015,36(6):125-128

ResearchandDesignofUniversalFIRDigitalFilterBasedonFPGA

ZHANGZhen

[Abstract]:FIRdigitalfilterisrealizedbasedonaddersandmultipliers.Bydelayingthemultiplicationaccumulationoftheinputtedsignalandthefixedtapcoefficients,thefilterresultsareobtained.Thefiltercoefficientisknown.Whenafixedordernumbercoefficientvalueisnotfixed,weneedtomultiplythefiltercoefficientsthroughexternalinpulwiththeinputsignal.ResearchonuniversaltypeofFIRdigitalfilterisbasedontraditionalserialFIRdigitalfilterstructuretransformation,usingVerilogHDLlanguageinquartusandModelsimsoftwarefordesignandsimulation.TheresultsshowthatthedesignofgeneralFIRdigitalfilterbasedonFPGAisfeasible.

[Keywordsl:Adder;Multiplier;FIRdigitalfilter;Serialstructure;GeneralFIRdigitalfilter

0引言

研究人员自20世纪中期以来不断的研究与发现,并且提出了一整套关于数字滤波器的相关理论。数字滤波器[1-3]是对输入的数字信号进行相应的累乘加运算得到输出的滤波信号的处理。利用FIR数字滤波器可以将不同的信号进行处理,从而提取出我们需要的信号而过滤掉干扰信号。不同的实现方法可以分为FIR数字滤波器和IIR数字滤波器[4]。由于FIR数字滤波器是可以实现线性相位的,并且它的单位冲击响应为有限长,因此FIR数字滤波器的系统是总是稳定的[5]。对于数字滤波器具有很强的稳定性、高精度性、灵活性等等比较优秀的特点,随着数字滤波技术的不断发展,FIR数字滤波器在信号处理、数字图像处理以及通信领域等等应用也是十分的广泛[6]。

FIR数字滤波器的系数的实现有两种方式,一种方式是可编程型的,另一种则是固定型的.对于可编程的系数实现使用起来比较的灵活,固定型的有利于实现高速度和低功耗的系统实现,本文使用的是可编程的。

对于阶数为N的FIR数字滤波器的实现,它的表达式为:

在实现FIR数字滤波器的方法中,使用FPGA的硬件实现可以使得FIR数字滤波器具有速度快的优点。但是对于阶数越多实现的FIR数字滤波器消耗的硬件资源也是比较多的,因此本文实现的通用型FIR数字滤波器是以低阶的方式来实现和验证的。

1FIR数字滤波器的基本原理

1.1滤波器的一般表示方式

对于FIR数字滤波器的数学表达式也可以表示成[7]:

式(1)中:N-滤波器的阶数;h(n)-第n级的抽头系数(单位脉冲响应);x(n)-第n时刻的输入信号。FIR数字滤波器的h(n)单位脉冲响应是有限长的,也就是FIR数字滤波器是一个有限长的序列与输入信号的乘积累加和实现的,从式(1)中可以看出FIR数字滤波器是由一个加法器和乘法器的集合构成的,对于每一次的采样都要进行N次的乘法和(N-l)次的加法运算。其中的单位脉冲响应h(n)为实数,在幅度上满足对称条件

h(n)=土h(N_n)。

1.2串行FIR数字滤波器的结构设计

对于h(n)做z域变换可以得到FIR数字滤波器的系统函数H(z),其系统函数表达式为:

n=U

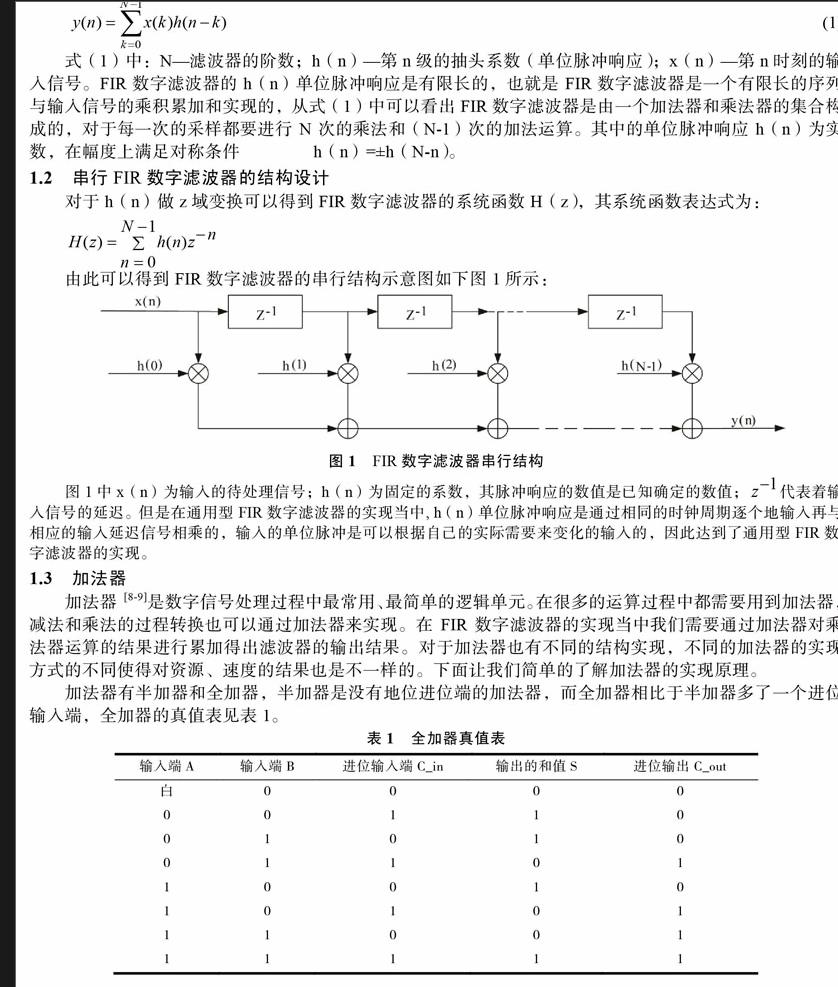

由此可以得到FIR数字滤波器的串行结构示意图如下图1所示:

图1中x(n)为输入的待处理信号;h(n)为固定的系数,其脉冲响应的数值是已知确定的数值;z-l代表着输入信号的延迟。但是在通用型FIR数字滤波器的实现当中h(n)单位脉冲响应是通过相同的时钟周期逐个地输入再与相应的输入延迟信号相乘的,输入的单位脉冲是可以根据白己的实际需要来变化的输入的,因此达到了通用型FIR数字滤波器的实现。

1.3加法器

加法器[8-9]是数字信号处理过程中最常用、最简单的逻辑单元。在很多的运算过程中都需要用到加法器,减法和乘法的过程转换也可以通过加法器来实现。在FIR数字滤波器的实现当中我们需要通过加法器对乘法器运算的结果进行累加得m滤波器的输出结果。对于加法器也有不同的结构实现,不同的加法器的实现方式的不同使得对资源、速度的结果也是不一样的。下面让我们简单的了解加法器的实现原理。

加法器有半加器和全加器,半加器是没有地位进位端的加法器,而全加器相比于半加器多了一个进位输入端,全加器的真值表见表1。

通过上表1的全加器真值表我们就可以得l斗J全加器的逻辑表达式为:

S=AABACin:

C_out=(A&B)|((AAB)&C_in);

从全加器的表达式可以看出和的值与输入信号和进位信号异或的到,进位信号同样与输入信号和进位信号相关。

1.4乘法器

乘法器[10]同样是信号处理的基本逻辑单元之一,比较常用的像滤波器、FFT都需要使用到乘法器。乘法器的实现也是有多种的,下面我们介绍在数字信号处理当中比较常用的一位相加乘法器。

移位相加乘法器的实现相对简单,就是对数进行二进制的转化进行相乘来实现。一位乘法器是根据乘数的每一位是0或1来判断被乘数是否移位相加,如果为1则被乘数移位相加,否则被乘数不想加。

一位乘法器的实现过程如下:

例如一个3bit乘法器需要一个6bit移位寄存器和一个6bit的加法器就可以实现。

2通用型FIR数字滤波器的研究与设计

2.1通用型FIR数字滤波器的原理

通用型的FIR数字滤波器与FIR数字滤波器的设计基本上相同。通用型的原理就是在FIR数字滤波器的基础之上对FIR数字滤波器的单位脉冲响应做一些处理,具体的处理就是将h(n)的单位脉冲响应的数值通过外部可输入的方式,经过寄存器寄存,寄存器的时钟周期和输入信号的时钟为同一个时钟,每一个时钟输入信号延迟一位的同时单位脉冲响应也进行延迟,最后与相应的延迟输入信号进行相乘在相加,输出的结果就是滤波输出。

2.2通用型FIR数字滤波器的结构设计

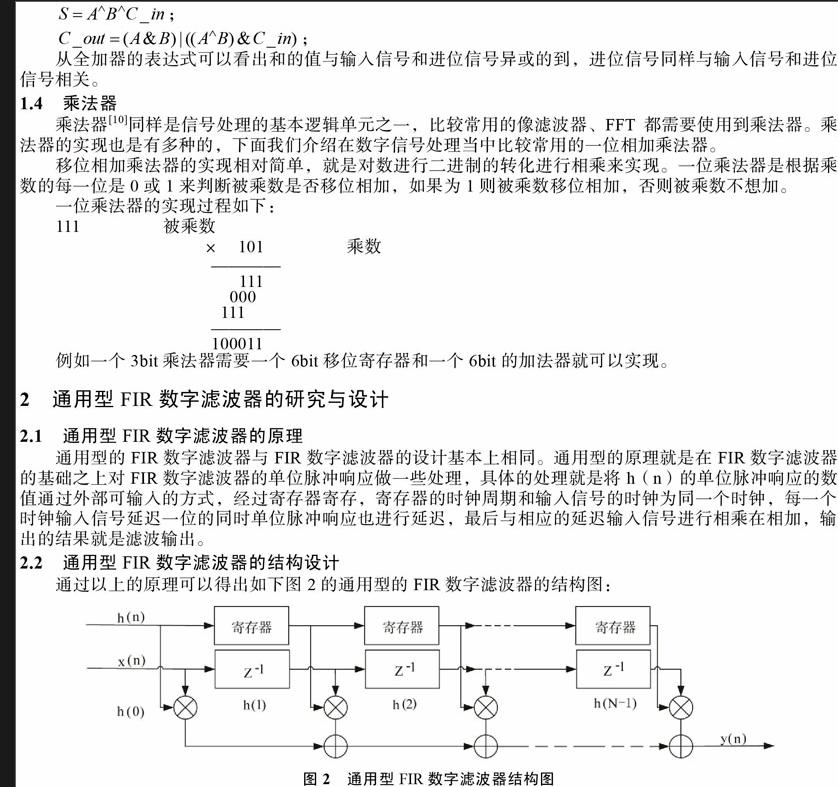

通过以上的原理可以得出如下图2的通用型的FIR数字滤波器的结构图:

从图2和图1的对比我们可以发现通用型FIR数字滤波器与一般的FIR数字滤波器的不同。一般的FIR数字滤波器的脉冲响系数应是固定的和每一个延迟信号直接相乘,而对于通用型的FIR数字滤波器的脉冲响应系数是通过引出输入端口进行输入的脉冲,这个输入的脉冲是根据自己的需要来编写脉冲响应系数的数值的,从而达到了通用型的目的。

对于通用型的FIR数字滤波器的表达式其输出的方式其实和式(1)-样的,只是通用型的结构上和输入方式上的不同,通用型是脉冲响应系数的值通过设置一个输入的端口,通过这个端口来输入脉冲响应系数的值得方式,而这个值是可以改变的。

3通用型FIR数字滤波器的设计验证

3.1设计实现

下面通过VerilogHDL语言通过QuartusII和Modelsim软件来设计一个8阶通用的FIR数字滤波器设计并进行验证。FIR数字滤波器的数据相系数为有符号的9位数,FIR数字滤波器的阶数是L=8,因此在设计中加法器的位数为:9+9+log2(/)一1=20。处理的第一步就是先set,如果setx=0就将滤波器的脉冲响应系数输入到抽头延迟线上,否则就将数据下载到x寄存器中;第二步执行乘积和的计算,对乘积进行一位有符号扩展,并加到前面的部分乘积和上。所有的乘法器为3级流水线结构。最后输出y_out除以256后输I斗『。

3.2验证

3.2.1代码实现

基于VerilogHDL语言的代码结构框架实现如下:

3.2.2验证仿真结果

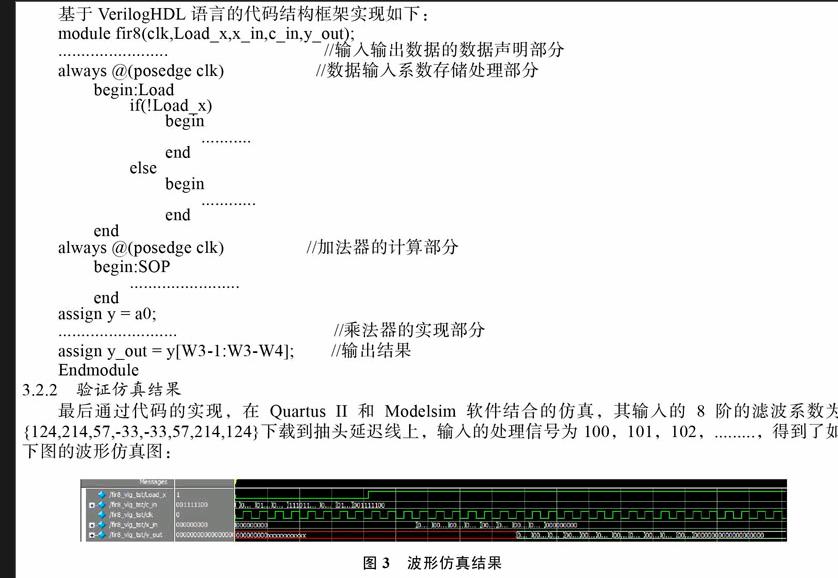

最后通过代码的实现,在QuartusII和Modelsim软件结合的仿真,其输入的8阶的滤波系数为{124,214,57,-33,-33,57,214,124}下载到抽头延迟线上,输入的处理信号为100,101,102,…….,得到了如下图的波形仿真图:

4结语

本文主要介绍了基于FPGA的串行滤波器的一般实现结构进行一些改进来实现通用型FIR数字滤波器的设计,根据串行结构实现的FIR数字滤波器的原理和结构,将串行结构的FIR数字滤波器的脉冲响应系数通过同一个时钟(clk)下载到滤波器当中,然后再与输入的信号进行累乘加的运算得到通用型的FIR数字滤波器。同时阐述了通用型这种设计方法的思想和原理实现方法,根据实验结果证明了通用型FIR数字滤波器的实现的可行性。通过这个实现的方法找到了另外一种实现FIR数字滤波器的实现方式,由于具有通用性对于硬件的资源可以重复的利用,具有很强的研究意义。

参考文献

[1]高学金,齐咏生,王普,基于卡尔曼滤波器和多向核主元分析的发酵过程在线监测[J].新型工业化,2011,1(9):102-110.

[2]刘雪艳,张雪英,黄丽霞.Gammachir滤波器组在语音特征提取中的应用[J].新型工业化,2011,1(11):21-28.

[3]祖霄鹏,肖建康,朱文军.新型正六边形微带多模带通滤波器[J].新型工业化,2011,1(12):113-116.

[4]胡广书.数字信号处理理论、算法与实现[M].北京:清华大学出版社,2003.

[5]吴镇扬.数字信号处理[M].北京:高等教育出版社,2004.

[6]李金明.数字FIR滤波器在监控系统中图像信号处理方面的应用[D].兰州:兰州理T大学,2006.

[7]王正彦,范延滨.用FPGA实现FIR滤波器算法研究[J]测控技术,2004,23(zl):123-126.

[8]朱小佩,萧蕴诗,岳继光.基于流水线结构的8位超前进位加法器设计[J].电子工程师,2009,9(31):1.

[9]王悦,陈涛.基于FPGA的流水线珠算加法器设计[J].科学技术与工程,2013,11(32):1.

[10]鞠芳,马昕,田岚.基于FPGA的数字乘法器性能比较[J].电子器件,2011,06:1.